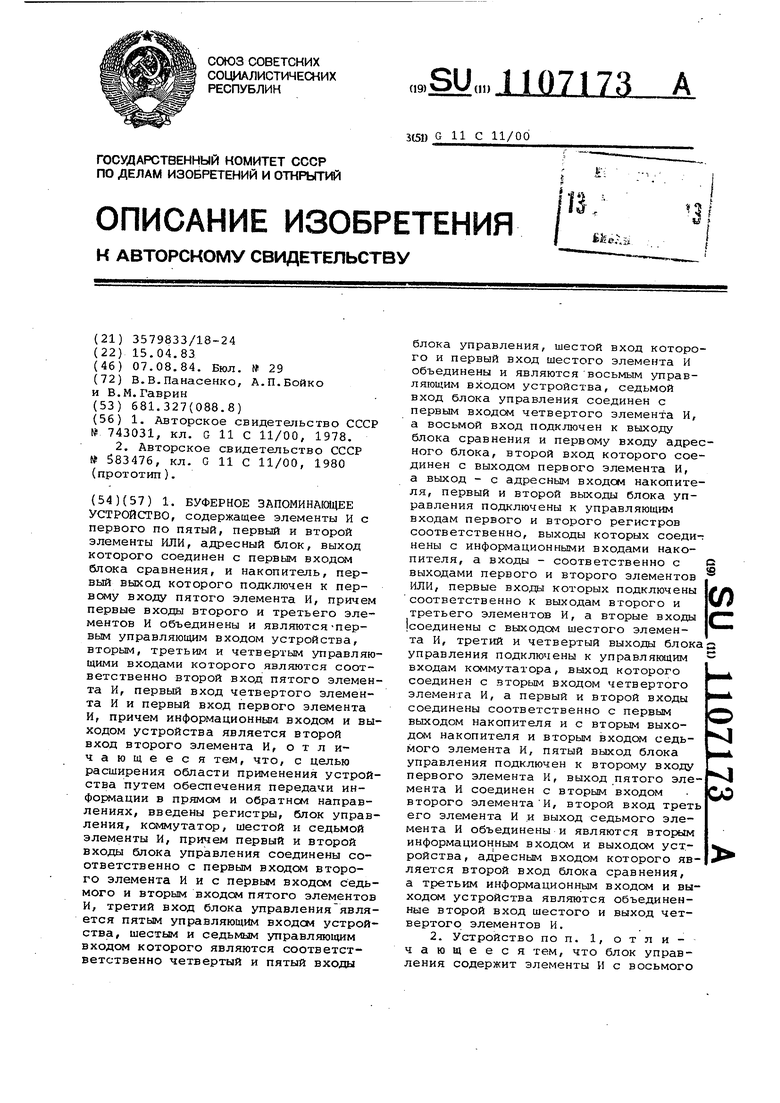

но двенадцатый, элемент НЕ и элементы ИЛИ с третьего по пятый, причем первые входы третьего и пятого элеM(:;iiTOB или и восьмого элемента И являются соответственно входами с первого по третий блока, первые входа четвертого элемента ИЛИ, девятого и одиннадцатого элементов И .объединены и являются четвертым входом блока, второй вход четвертого элемента ИЛИ соединен с первыми входами десятого и двенадцатого элементов И и являетс пятым входом блока, шестым входом которого является второй вход третьего элемента ИЛИ, седьмым входом - объединенные вторые входы пятого элемента ИЛИ, одиннадцатого и двенадцатого элементов И, а восьмым входом - вход элемента НЕ, вторые входы девятого и десятого элементов И подключены к выходу третьего элемента ИЛИ и третьему входу пятого элемента ИЛИ, выходы четвертого и пятого элементов ИЛИ соединены с вторым и третьим входами восьмого элемента И, четвертый вход которого подключен к, выходу элемента НЕ, и третьим входом элементов И с девятого по двенадцатый, выходы которых и выход восьмого элемента И являются соответственно выходами с первого по пятый блока .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1543442A1 |

| Устройство для управления памятью | 1982 |

|

SU1038968A1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1095238A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149314A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1495855A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

1. БУФЕРНОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее элементы И с первого по пятый, первый и второй элементы ИЛИ, адресный блок, выход которого соединен с первым входом блока сравнения, и накопитель, первый выход которого подключен к первому входу пятого элемента И, причем первые входы второго и третьего элементов И объединены и являются-первым управляющим входом устройства, вторым, третьим и четвертым управляющими входами которого являются соответственно второй вход пятого элемента И, первый вход четвертого элемента И и первый вход первого элемента И, причем информационныгл входом и выходом устройства является второй вход второго элемента И, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения передачи информации в прямой и обратном направлениях, введены регистры, блок управления, коммутатор, шестой и седьмой элементы И, причем первый и второй входы блока управления соединены соответственно с первым входом второго элемента И и с первым входом седьмого и вторым входом пятого элементов И, третий вход блока управления является пятым управляющим входом устройства, шестым и седьмым управляющим входом которого являются соответстветственно четвертый и пятый входы блока управления, шестой вход которого и первый вход шестого элемента И объединены и являются восьмым управляющим входом устройства, седьмой вход блока управления соединен с первым входом четвертого элемента И, а восьмой вход подключен к выходу блока сравнения и первому входу адрес ного блока, второй вход которого соединен с выходом первого элемента И, а выход - с адресным входом накопителя, первый и второй выходы блока управления подключены к управляющим входам первого и второго регистров соответственно, выходы которых соеди-т нены с информационными входами накопителя, а входы - соответственно с выходами первого и второго элементов ИЛИ, первые входы которых подключены (Л соответственно к выходам второго и с: третьего элементов И, а вторые входы соединены с выходсм шестого элемента И, третий и четвертый выходы блока управления подключены к управляющим входам коммутатора, выход которого соединен с вторым входом четвертого элемента И, а первый и второй входы соединены соответственно с первым выходом накопителя и с вторым выходом накопителя и вторым входсяи седьмого элемента И, пятый выход блока управления подключен к второму входу первого элемента И, выход пятого элесо мента И соединен с вторым входом второго элементаИ, второй вход треть его элемента И и выход седьмого элемента И объединены и являются вторым информационным входом и выходом устройства, адресным входом которого является второй вход блока сравнения/ а третьим информационным входом и выходом устройства являются объединенные второй вход шестого и выход четвертого элементов И. 2. Устройство поп. 1, отличающееся тем, что блок управления содержит элементы И с восьмого

.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении буферных запоминающих устройств каналов и устройств обмена.

Известно буферное запоминающее устройство, содержащее накопитель, дешифратор адреса, датчики кода адреса, коммутатор, элементы НЕ, коммутатор схем выделения сигналов, элементы ИЛИ, делители частоты и схемы формирования контрольных символов 11,

Недостатком этого устройства является невозможность передачи информации в двух направлениях.

Наиболее близким техническим реШением к изобретению является буферное запоминающее устройство, содержащее накопитель, два элемента ИЛИ, блок сравнения, бЛок формирования адреса, первый элемент И, первую и вторую группы элементов И, причем один из выходов накопителя соединен с одним из входов второго элемента второй группы И, а вторые входы первого и второго элементов этой группы соединены с управляющими шинами считывания, выход первого элемента второй группы И соединен с выходной шиной, первые входы первого и второго элементов первой группы И соединены с управляющей шиной записи, а второй вход первого элемента - с выходной шиной, йходная шина смены адреса соединена с одним из входов первого элемента И, выход.блока формирования адреса - с одним из входов схемы сравнения 2.

Недостатксм известного устройства вляется то, что для передачи информаионного кода в двух направлениях спользуются отдельно вход и отдельо выход, что не позволяет согласовать работу двух устройств с различной шириной информационного кода, , т.е. отсутствует возможность параллельно-последовательного и последовательно-параллельного преобразования информации и возможность управлять разрядностью и количеством информационного кода, что ограничивает область применения устройства.

Целью изобретения является расширение области применения устройства путем обеспечения передачи информации в прямом и в обратном направлениях.

Поставленная цель достигается

тем, что в буферное запоминающее устройство, содержащее элементы И с первого по пятый, первый и второй элементы ИЛИ, адресный блок, выход которого соединен с первым входом блока

сравнения, и накопитель, первый выход которого подключен к первсму входу пятого элемента И, причем первые . входы второго и третьего элементов И объединены и являются первым управляю5 щям входом устройства, вторым, третьим и четвертым управляющими входами которого являются соответственно второй вход пятого элемента И, первый вход четвертого элемента И и первый

0 вход первого элемента И, первым информационным входом и выходом устройства является второй вход второго элемента и, введены регистры, блок управления, коммутатор, шестой и

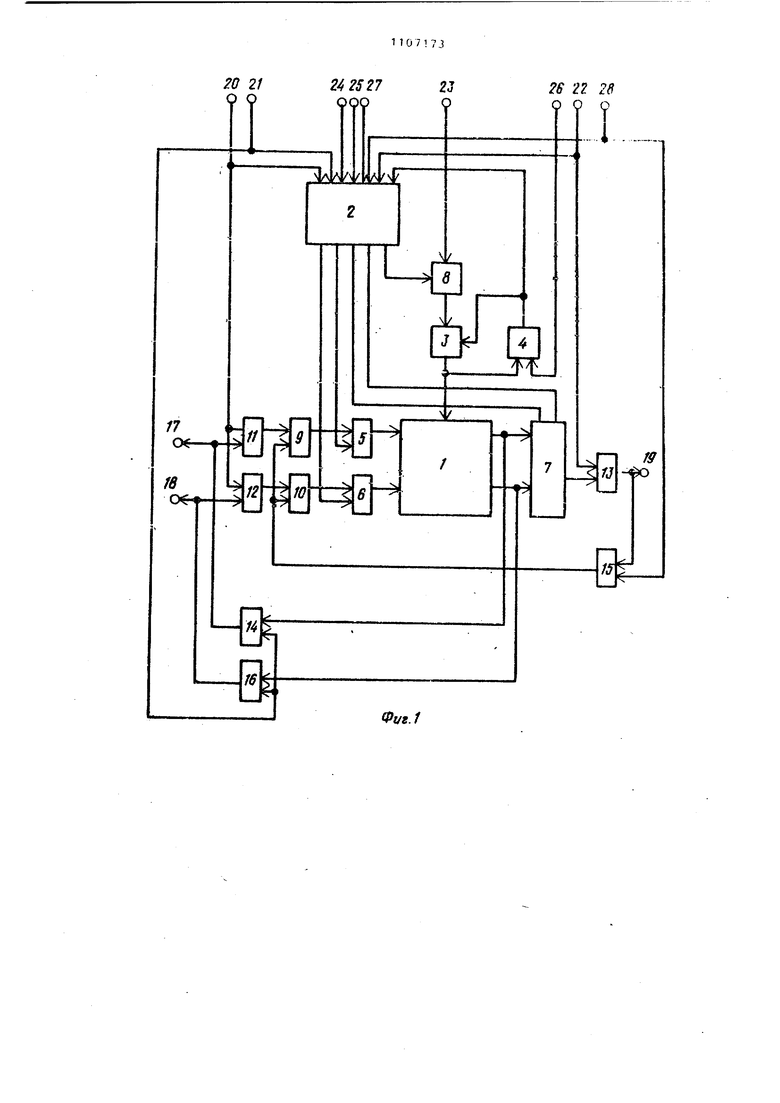

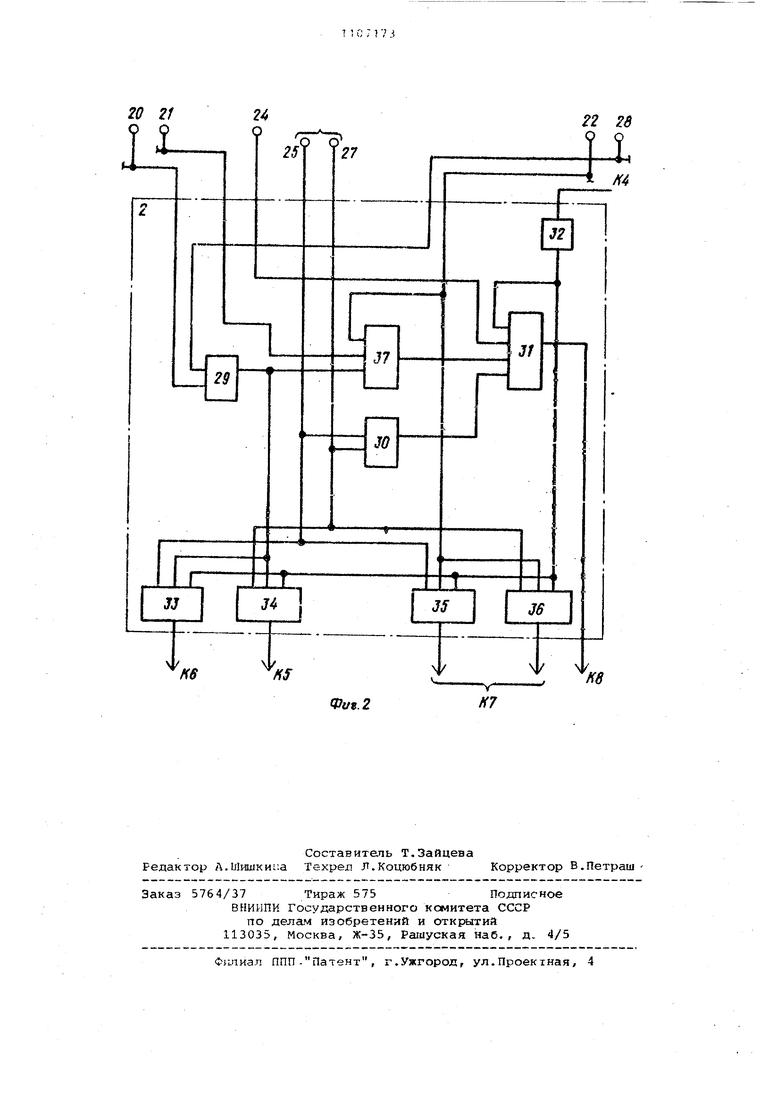

5 седьмой элегленты И, причем первый и второй входы блока управления соединены соответственно с первым входом второго элемента И и с первым входом седьмого и вторым входо пятого элеQ ментов И, третий вход блока управления является пятьм управляющим входом устройства, шестым и седьмым управляющими входами которого являются соответственно четвертый и пятый входы блока управления, шестой вход коiTOporo и первый вход шестого элемента И объединены и являются восьмым управляющим входсм устройства, седьмой вход блока управления соединен с первым входс л четвертого элемента И, а восьмой вход подключен к выходу блока сравнения и первому входу адресного блЬка, второй вход которого соединен с выходом первого элемента И, а выход - с адресным входом накопителя, первый и второй выходы блока управления подключены к управляющим входам первого и второго реги стров соответственно, выходы которых соединены с информационными входами накопителя, а входы - соответственно с выходами первого и второго элементов ИЛИ, первые входы которых подклю чены соответственно к выходам второго и третьего элементов И, а вторые входы соединены с выходом шестого эл мента И, третий и четвертый выхода блока управления подключены к управляющим входам коммутатора, выход которого соединен с вторьом входом четвертого элемента И, а первый и второ входы соединены соответственно с пер вым выходом накопителя и с вторым вы ходом накопителя, и вторым входом седьмого элемента И, пятый выход бло ка управления подключен к второму входу первого элемента И, выход пято го элемента И соединен с вторым входсм второго элемента И, второй вход третьего элемента И и выход седьмого элемента И объединены и являются вто рым информационным входом и выходом устройства, адресным входом которого является второй вход блока сравнения а третьим информационным входом и вы ходом устройства являются объединенные второй вход шестого и выход четвертого элементов И. При этом блок управления содержит элементы И с восьмого по двенадцатый элемент НЕ и элементы ИЛИ с третьего по пятый, причем первые входы третьего и пятого элементов ИЛИ и восьмого элемента И являются соответ ственно входами с первого по третий блока, первые входы четвертого элемента ИЛИ, девятого и одиннадцатого элементов И объединены и являются четвертым входом блока, второй вход четвертого элемента ИЛИ соединен. с первыми входами десятого и двена дцатого элементов И и является пятым входом блока, шестым входом которого является второй вход третьего элемен та ИЛИ, седьмым входсм - объединенные вторые входы пятого элемента ИЛИ одиннадцатого и двенадцатого элементов И, а восьмым входом - вход элемента НЕ, вторые входы девятого и десятого элементов И подключены к выходу третьего элемента ИЛИ и треть ему входу пятого элемента ИЛИ, выходы четвертого и пятого элементов rfjlH соединены с вторым и третьим входами восьмого элемента И, четвертый вход которого подключен к выходу элемента НЕ, и третьим входом элементов И с девятого по двенадцатый, выходы которых и выход восьмого элемента И являотся соответственно выходами с первого по пятый блока. I На фиг. 1 показана функциональная схема предложенного устройства; на фиг, 2 - функциональная схема блока управления. Предложенное устройство содержит накопитель 1, блок 2 управления, адресный блок 3, блок 4 сравнения, первый 5 и второй 6 регистры, коммутатор 7, первый элемент И 8, первый 9 и второй 10 элементы ИЛИ, элементы И 11-16 с второго по седьмой, первый 17, второй 18 и третий 19 информационные входы и выходы, управляющие входы 20-25 с первого по шестой, адресный вход 26, седьмой 27 и восьмой 28управляющие входы устройства. Блок управления содержит третий 29и четвертый 30 элементы ИЛИ, восьмой элемент И 31, элемент НЕ 32, элементы И 33-36 с девятого по двенадцатый и пятый элемент ИЛИ 37. Устройство работает следующим образам, Ввод информации, поступающей на входы 17-19 в накопитель 1, осуществляется через элементы и 11,12 и 15, элементы ИЛИ 9 и 10 и регистры 5 и 6. Вывод информации-из накопителя 1 осуществляется через коммутатор 7 и элементы И 13, 14 и 16 на выходы 17-19. Ввод 1вьшод) информации в (из) накопитель 1 осуществляется по адресам, которые вырабатываются блоком 3. При наличии сигнала обращения на входе 24, блок 2 вырабатывает сигнал управления, поступающий на один из входов элемента И 8, второй вход которого соединен с входсм 23, предназначенным для смены адреса, а выход - с одним из входов блока 3. Блок 4 обеспечивает сравнение внутреннего адреса, вырабатываемого блоксм 3, и внешнего адреса, поступающего с входа 26, и установку блока 3 в исходное состояние, управляя количеством записанного (считанного) информационного кода. При поступлении сигнала кода управления на входы 25 и 27 блок 2 вырабатывает управляющие сигналы,поступающие на входы регистров 5 и 6, обеспечивая управление разрядностью параллельного информационного кода, поступающего на входы и выходы 17 и 18, и последовательного информационного кода, поступающего с входа

и выхода 19, а также обеспечивая управление коммутаторсм 7 по параллельно-последовательному преобразованию считьшаемой на вход и выход 19 информации.

Последовательность ввода и вьдвода информации из накопителя 1 определяется управляющими сигналами на входах 20, 28, 21 и 22, которые формируются в зависимости от режима работы устройства.

При работе в режиме параллельного обмена информация может поступать и выдаваться на информационные входы и выходы 17 и 18. При этом на вход 23 поступает сигнал, обеспечивающий считывание выдаваемой информации, по адресу, формируемому блоком 3., и ее вывод производится на входы и выходы 17 и 18, а запись с этих входов и выходов обеспечивается при поступлении сигнала на вход 20.

При работе в режиме последовательного обмена информация может поступать и выдаваться на вход и выход 19 При этом на вход 22 поступает сигнал обеспечивающий считывание выдаваемой

информации по адресу, формируемому блоком 3, и ее вывод производится на вход и выход 19, а запись с входа 19 обеспечивается при поступлении сигнала на вход 28.

Устройство позволяет производить запись информации в режиме параллельного обмена и считывание этой информации в режиме последовательного обмена или запись информации в режиме параллельного обмена.

Запись (считывание) в режимах параллельного обмена и последовательного обмена начинается по сигналу смены адреса, поступающего на вход 23, только после подачи сигнала обращения на вход 24. в режиме параллельного обмена последующая запись (считывание)информации производится только по сигналу, поступающему на вход 23. В режиме последовательного обмена запись (считывание) информации по следующему адресу производится только после поступления очередного сигнала обращения на вход 24.

Предложенное буферное запоминающее устройство может использоваться в стратстопных синхронных системах передачи (приема) информации и в случае, когда информация передается с магистральных двухнаправленных шин с различной шириной информационного кода и промежуточным хранением в памяти. При этом сокращается количество оборудования за счет более эффективного использования накопителя 1, уменьшается потребляемая мощность устройства и затраты на его изготовление. Это достигается путем совмещения функций параллельно-последовательного (последовательно-параллельного I преобразования и управления разрядностью параллельного кода в одном устройстве.

Технико-эконся ическое преимущество предложенного устройства заключается в более широкой по сравнению с известным устройством области применения.

242527

20 21 О

26 гг 2S

2J

О

о о

П

и

20 2124

О

22 28

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № | |||

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1976 |

|

SU583476A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-15—Подача