1

Изобретение относится к области вычислительной техники и может быть применено в устройствах для сложения чисел.

Известны сумматоры, содержащие регистры, две группы схем «И, схемы сравнения и схемы анализа нуля, причем выходы каждого из разрядов первого регистра соединены со счетными входами соответствующих разрядов второго регистра и со входами схемы анализа нуля, выходы каждого разряда третьего регистра соединены со счетными входами соответствующих разрядов четвертого регистра, выходы каждой схемы «И первой группы соединены со входами соответствующих разрядов первого регистра, а второй - третьего регистра.

Недостатком известного устройства является то, что для контроля результата суммирования необходимо введение спецнальпых схем, увеличивающих время контроля.

Целью изобретения является уменьщение времени контроля сумматора.

С этой целью выходы каждого разряда первого и второго регистров соединены соответственно с первым и вторым входами соответствующей схемы «И второй группы, а выходы каждого разряда третьего и четвертого регистров соединены соответственно с первыми и вторыми входами соответствующей схемы

«И первой группы, выходы первого и третьего регистров соединены со входами первой схемы сравнения и выходы второго и четвертого регистров соединены со входами второй схемы сравнения.

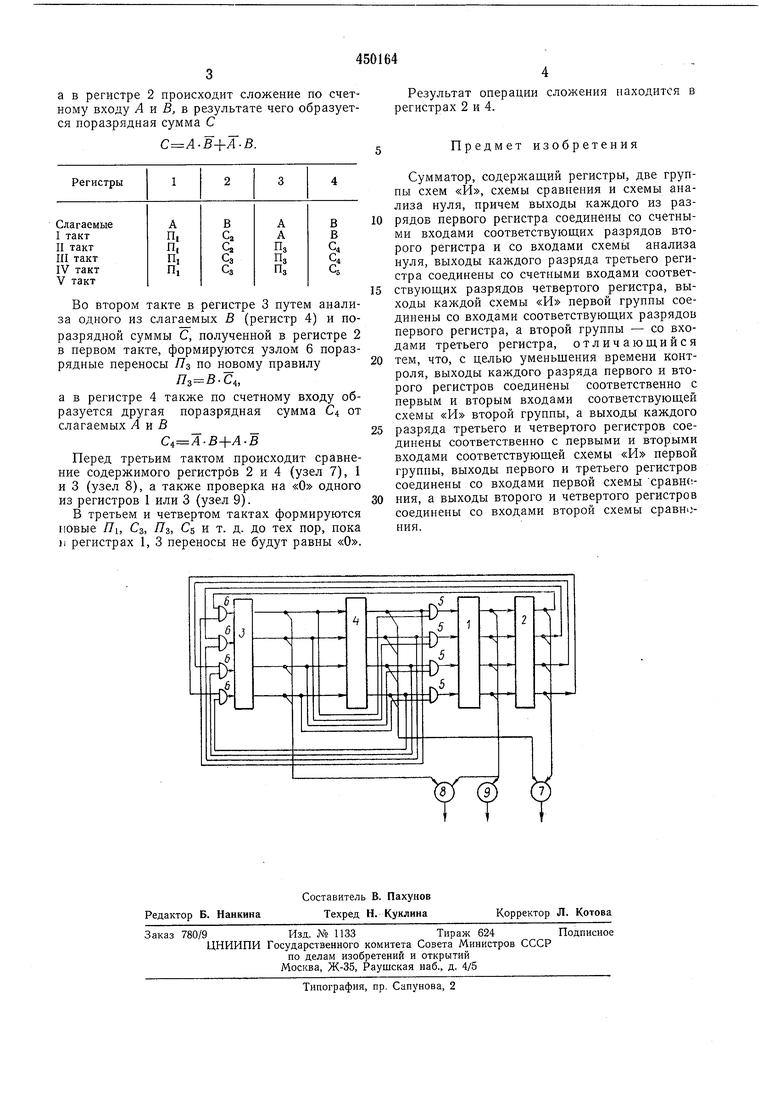

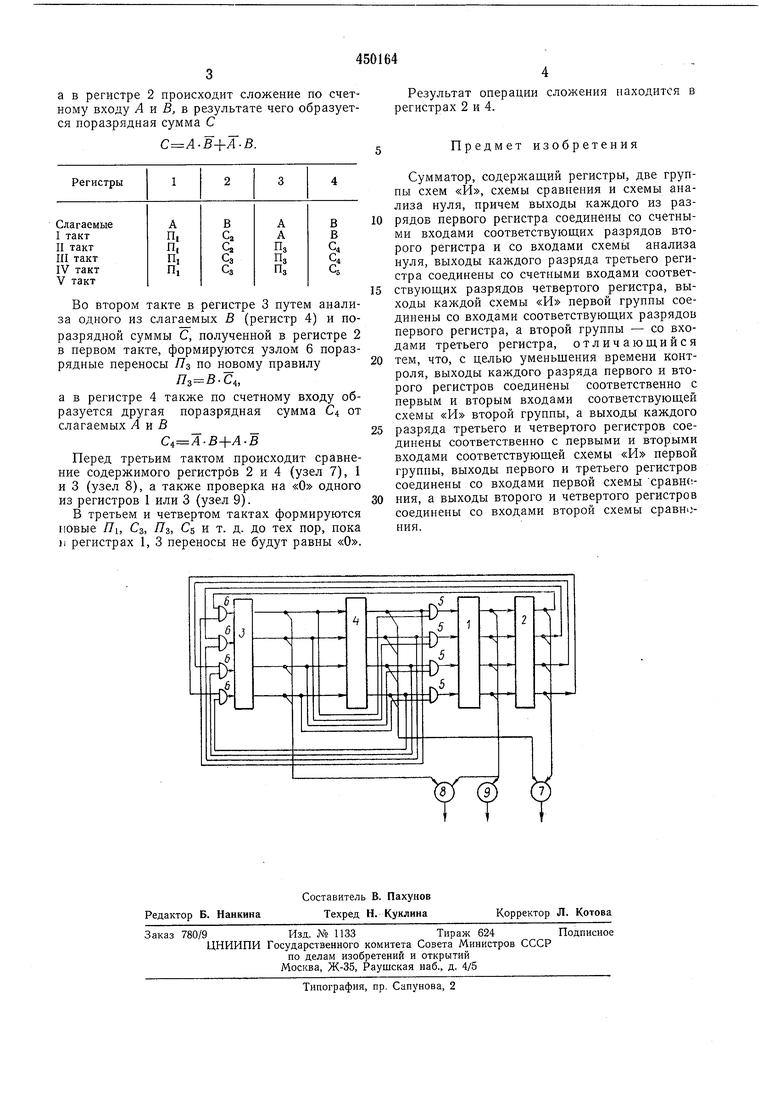

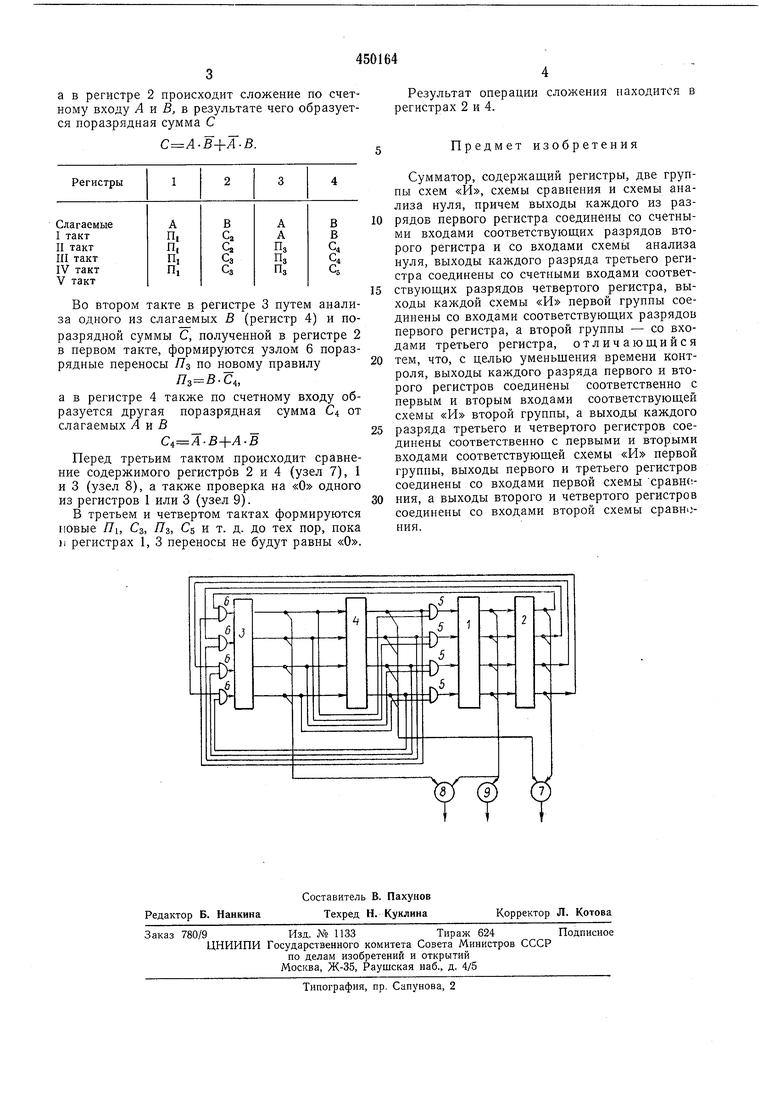

Блок-схема предлагаемого сумматора приведена па чертеже.

Сумматор состоит из регистра 1, соединенного с регистром 2, регистра 3, соединенного с регистром 4, первой группы схем «И 5 и второй группы схем «И 6, причем выходы схем 5 и 6 соединены со входами регистров 1, 3 соответственно, выходы регистров 3, 4 соединены со входами схем 5, а входы схем 6 соединены с выходами регистров 2, 4; выходы регистров 2, 4 соединены, кроме того, со входами схемы сравнения 7, а выходы регистров 3, 1 соединены со входами схемы сравнения 8; кроме того, выходы регистра 1 соединены со входами схемы 9 анализа нуля.

Устройство работает следующим образом.

Перед началом суммирования в регистрах 1, 3 находится первое слагаемое А, в регистрах 2 и 4 - второе слагаемое В.

В первом такте (см. таблицу) в регистре 1 путем логического анализа А R В формируются поразрядные переносы П (узел 5)

.В,

а в регистре 2 происходит сложение по счетному входу Л и В, в результате чего образуется поразрядная сумма С

С А-В+А.В.

Во втором такте в регистре 3 путем анализа одного из слагаемых В (регистр 4) и поразрядной суммы С, полученной в регистре 2 в первом такте, формируются узлом 6 поразрядные переносы Яз по новому правилу

п.в.с,,

а в регистре 4 также по счетному входу образуется другая поразрядная сумма С от слагаемых Л и 5

.Б+Л.5

Перед третьим тактом происходит сравнение содержимого регистров 2 и 4 (узел 7), 1 и 3 (узел 8), а также проверка на «О одного из регистров 1 или 3 (узел 9).

В третьем и четвертом тактах формируются новые Яь Сз, Яз, GS и т. д. до тех пор, пока )i регистрах 1, 3 переносы не будут равны «О.

Результат операции сложения находится в регистрах 2 и 4.

Предмет изобретения

Сумматор, содержащий регистры, две группы схем «И, схемы сравнения и схемы анализа нуля, причем выходы каждого из разрядов первого регистра соединены со счетными входами соответствующих разрядов второго регистра и со входами схемы анализа нуля, выходы каждого разряда третьего регистра соединены со счетными входами соответствующих разрядов четвертого регистра, выходы каждой схемы «И первой группы соединены со входами соответствующих разрядов первого регистра, а второй группы - со входами третьего регистра, отличающийся

тем, что, с целью уменьщения времени контроля, выходы каждого разряда первого и второго регистров соединены соответственно с первым и вторым входами соответствующей схемы «И второй группы, а выходы каждого

разряда третьего и четвертого регистров соединены соответственно с первыми и вторыми входами соответствующей схемы «И первой группы, выходы первого и третьего регистров соединены со входами первой схемы сравне;ния, а выходы второго и четвертого регистров соединены со входами второй схемы сравнония.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для обнаружения и исправления ошибок сумматора | 1982 |

|

SU1038946A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Многовходовой сумматор | 1989 |

|

SU1679483A1 |

Авторы

Даты

1974-11-15—Публикация

1972-12-18—Подача