1

Предложенная схема относится к области автоматики и вычислительной техники и может быть использована при реализации технических средств дискретной автоматики и цифровых вычислительных машин.

Известны схемы для сравнения двоичных чисел, содержащие многоэмиттерные транзисторы, коллекторы которыхобъединены между собой и через резистор подключены к источнику питания, резисторы, диоды.

Однако известные устройства относительно сложны, так как содержат, кроме резисторов, диоды.:

Предложенная схема отличается тем, что, в ней базы транзисторов связаны со входными шинами через резисторы, а эмиттеры подключены ко входным шинам непосредственно.

Это позволяет упростить схему.

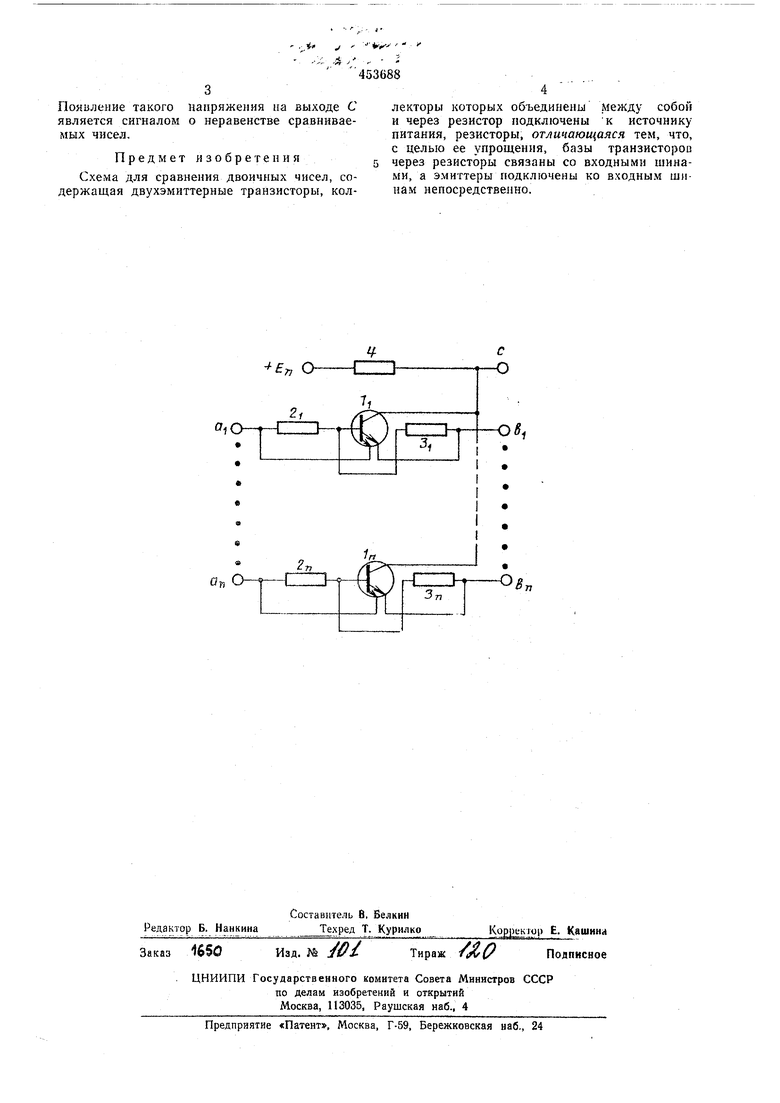

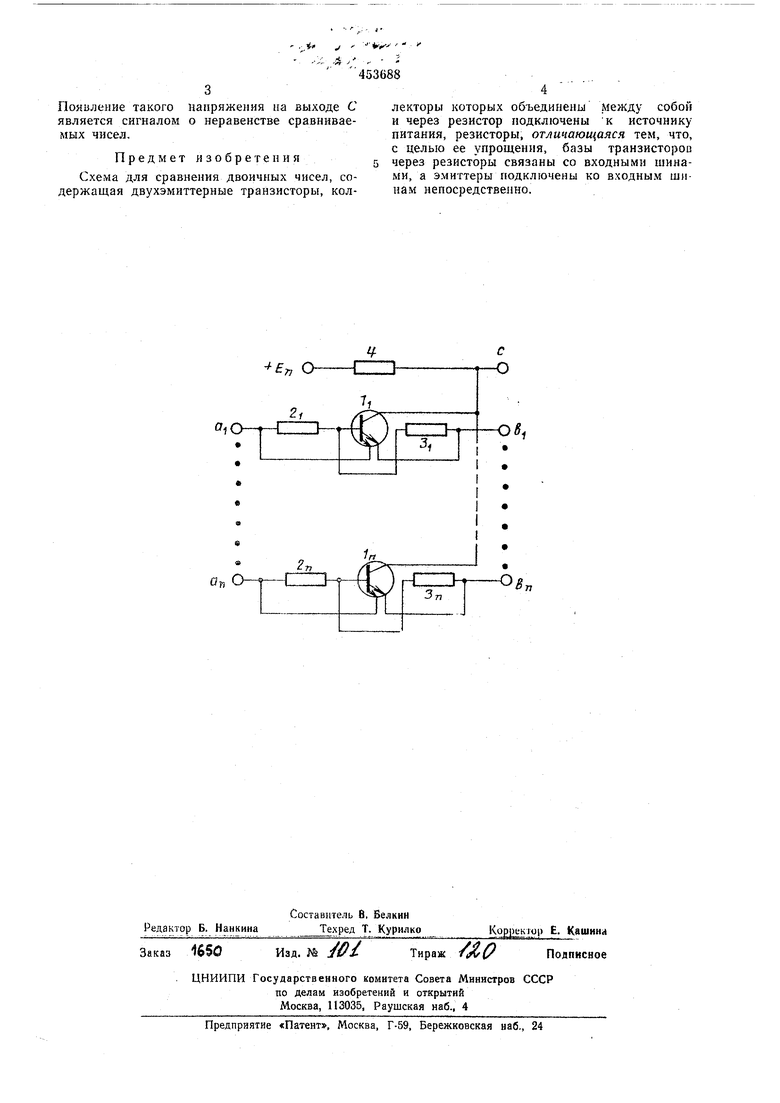

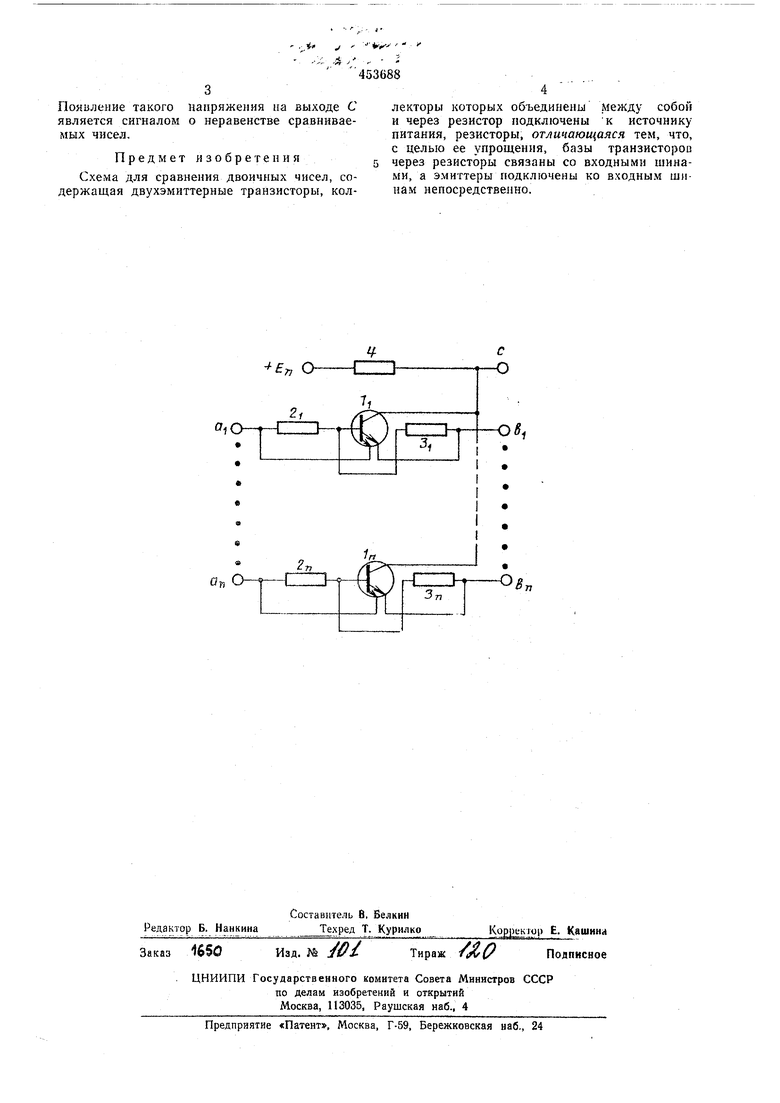

Предложенная схема представлена нл чертеже.

Схема содержит ячейки, каждая из которых состоит из двухэмиттерного транзистора 1 н двух резисторов 2 и 3. Входами ячейки служат соединения эмиттеров транзисторов с резисторами; другие выводы последних объединены вместе и подключены к базе транзистора 1. Выходом схемы является точка соединения коллекторов транзисторов 1,,

1 „, через резистор 4 подключенных к источнику питания.

Схема работает следующим образом. При поступлении на входы i-ii ячейки одинаковых двоичных чисел, например двух «единиц, разность напряжений между входами П; и bj будет равна нулю. Вследствие этого ток в базе транзистора 1,- равен нулю и транзистор заперт, что является сигналом о совпадении г-х разрядов сравнивае.мых чисел. Только в том случае, когда все ячейки выдадут такой сигнал, напряжение на выходе С может стать высоким. Появление этого напряжения является сигналом совпадения сравниваемых чисел А и В.

Прп наличии несовпадения состояний на входах хотя бы одной i-fi ячейки происходит следующее.

Вследствие разности напряжений между

входами а,- и Ь/ по како.му-либо резистору 2 или 3 протекает ток от входа с единичным состоянием, например от в.хода а,. через резистор 2; , базу транзистора 1,. н один из эмиттеров этого транзистора к другому

входу 6, , находящемуся в нулевом состоянии. Вследствие протекания базового тока транзистор 1,- оказывается открыты.м н щунтирует ток резистора 4 на тот вход /-и ячейки, который находится в нулевом состоянии.

Напряжение на выходе С оказывается низким.

Появление такого напряжения на выходе С является сигналом о неравенстве сравниваемых чисел.

Предмет изобретения

Схема для сравнения двоичных чисел, содержащая двухэмиттерные транзнсторы, кол453688

лекторы которых объединены между собоГг и через резистор подключены к источнику питания, резисторы, отличающаяся тем, что, с целью ее упрощения, базы транзисторов через резисторы связаны со входными шинами, а эмиттеры подключены ко входным шинам непосредственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое устройство | 1977 |

|

SU738171A1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1989 |

|

SU1676100A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ НА РАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2549142C1 |

OiO

Даты

1974-12-15—Публикация

1972-03-24—Подача