Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известна схема, выполняющая логическую операцию И [1 Гольденберг Л.М. Импульсные устройства. М.: Радио и связь, 1981, стр. 52, рис. 2.27а, содержащая два транзистора (двухэмиттерный и одноэмиттерный), три резистора и источник питающего постоянного напряжения. Названная схема может иметь еще один транзистор (дополнительный), если существует потребность иметь в схеме определенный известный выход-выход с открытым коллектором [1, стр. 52, второй абзац].

Недостатком ее является малая нагрузочная способность. Электрический ток только одного транзистора формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это привело бы к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению его нагрузочной способности.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент ИЛИ/ИЛИ-НЕ [Манаев Е.И. Основы радиоэлектроники. Радио и связь, 1985, стр. 342, рисунок 14.23], содержащий шесть транзисторов, пять резисторов и два источника постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из шести транзисторов формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Приведенный логический элемент относится к ЭСЛ-элементам (ЭСЛ - эмиттрено-связанная логика).

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И.

Это достигается тем, что в триггерный логический элемент И, содержащий питающий постоянный источник, минусовой вывод которого соединен с общей шиной и заземлен, последовательно между собой соединенные первый резистор, первый n-р-n транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу (плюсовой вывод) питающего постоянного источника, свободный вывод второго резистора заземлен, последовательно включенные третий резистор и второй n-р-n транзистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода питающего постоянного источника, эмиттер второго транзистора подключен к общему выводу эмиттера первого транзистора и второго резистора, источник опорного напряжения, минусовой вывод которого заземлен, а плюсовой - соединен с базой второго транзистора, последовательно включенные третий n-р-n транзистор и четвертый резистор, соединенный с эмиттером третьего транзистора, также имеется пятый резистор, введены р-n-р дополнительный транзистор, n-р-n двухэмиттерный дополнительный транзистор и дополнительный резистор, эмиттер р-n-р дополнительного транзистора подсоединен к общему выводу третьего резистора и коллектора второго транзистора, база этого дополнительного транзистора подключена к общему выводу первого резистора и коллектора первого транзистора, а также к коллектору третьего транзистора, наконец, коллектор приведенного дополнительно транзистора соединен и с базой третьего транзистора, и с одним из двух выводов пятого резистора, свободный вывод последнего пятого резистора подключен к свободному выводу четвертого резистора и их общий вывод образует относительно «земли» выход логического элемента, коллектор n-р-n двухэмиттерного транзистора подсоединен к базе первого транзистора, выводы эмиттеров двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента, между базой последнего транзистора и общим выводом выхода питающего постоянного источника напряжения, первого и третьего резисторов включен дополнительный резистор.

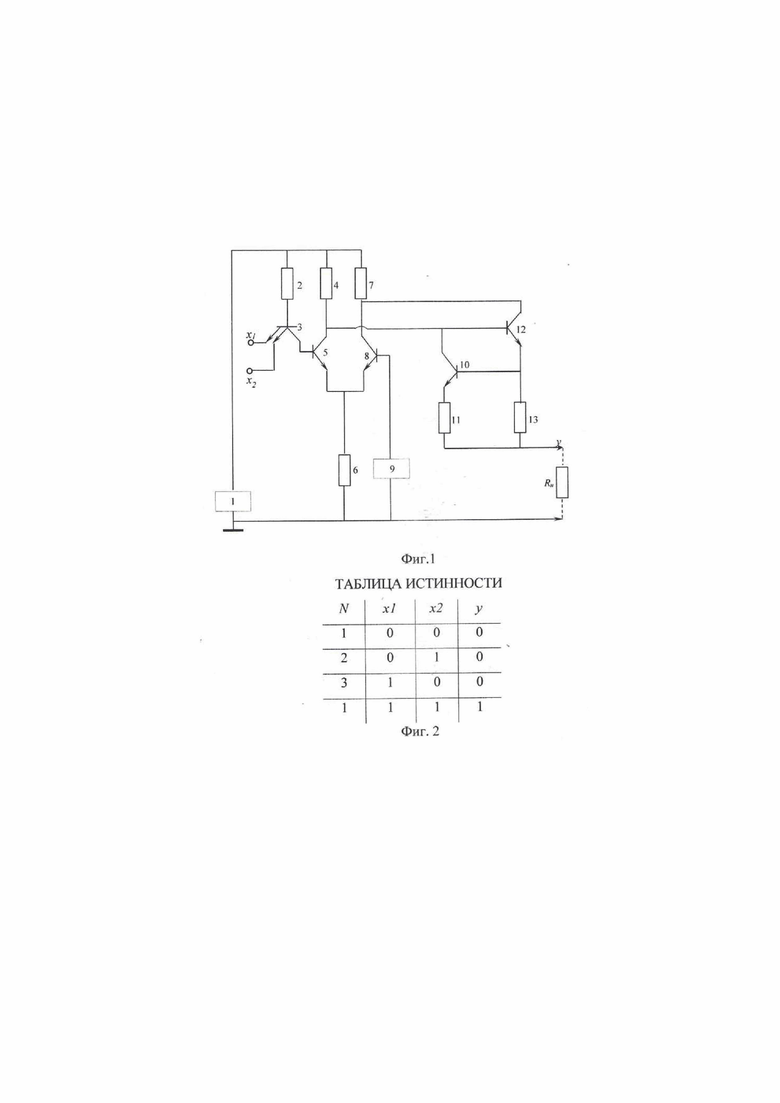

Сущность изобретения поясняется схемой триггерного логического элемента И (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном логическим элементе И общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. К выходу (плюсовой вывод) этого источника подсоединен один из выводов резистора 2, другой его вывод подключен к базе двухэмиттерного n-р-n транзистора 3. Два вывода эмиттеров этого транзистора образуют относительно «земли» два входа x1 и x2 логического элемента. Последовательно между собой включены резистор 4, n-р-n транзистор 5 и резистор 6. Свободный вывод резистора 4 подсоединен к общему выводу резистора 2 и выхода источника 1. База транзистора 5 подключена к коллектору транзистора 3, а свободный вывод резистора 6 заземлен.

Последовательно включены резистор 7 и n-р-n транзистор 8. Свободный вывод резистора 7 подсоединен к общему выводу резисторов 2, 4 и выхода питающего источника 1. Эмиттер транзистора 8 подключен к общему выводу резистора 6 и эмиттера транзистора 5. С базой транзистора 8 соединен выход (плюсовой вывод) источника 9 опорного напряжения, минусовой вывод этого источника заземлен.

Последовательно между собой включены n-р-n транзистор 10 и резистор 11. Коллектор транзистора 10 подсоединен к общему выводу резистора 4 и коллектора транзистора 5. Свободный вывод резистора 11 соединен с выходом у относительно «земли» логического элемента. Последовательно включены р-n-р транзистор 12 и резистор 13. Эмиттер транзистора 12 подсоединен к общему выводу резистора 7 и коллектора, транзистора 8. База транзистора 12 подключена к общему выводу резистора 4 и коллекторов транзисторов 5 и 10. Коллектор транзистора 12 соединен и с базой транзистора 10, и с одним из выводов резистора 13. Другой вывод резистора 13 подключен к общему выводу резистора 11 и выхода логического элемента у.

На фиг. 1 часть схемы на транзисторах 10 и 12 является триггером на транзисторах противоположного типа проводимости, а часть схемы на транзисторах 5, 8 представляет собой переключатель тока. Резисторы 4 и 7 входят и в состав переключателя тока, и в состав триггера на транзисторах противоположного типа проводимости. На фиг. 1 также приведен пунктирными линиями резистор RH, условно отображающий внешнюю нагрузку логического элемента.

Триггерный логический элемент И работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на транзисторах 10, 12 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда, в том числе на резисторах 4 и 13, нулевые значения напряжения. Они прикладываются к базам транзисторов 10, 12 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 10 и 12 открыты, их электрические токи создают напряжения, в том числе и на резисторах 4 и 13 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 10, 12 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространенные триггеры, переходить из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

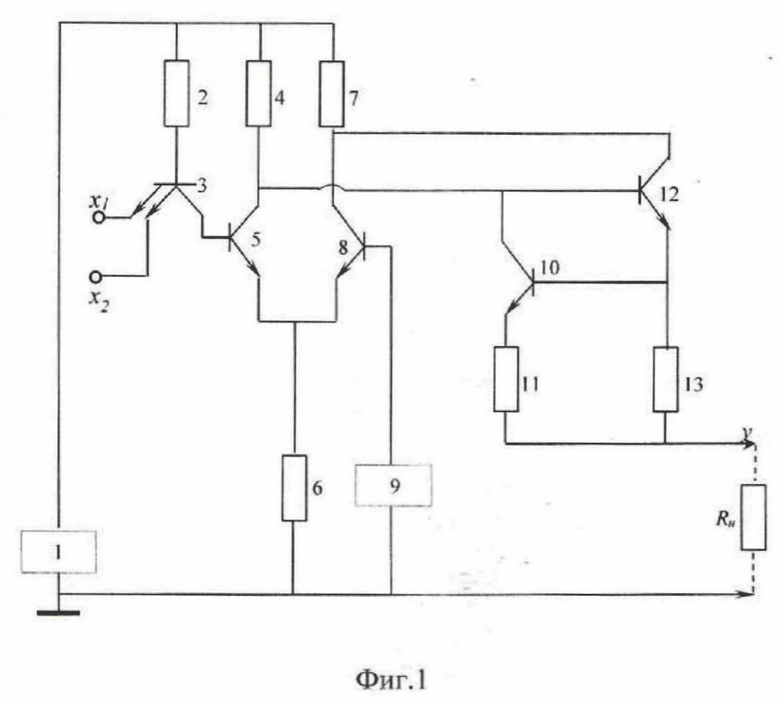

Работа логического элемента И отражается таблицей истинности (фиг. 2), где x1 и х2 - условное отображение входных сигналов, у - условное отображение сигнала на выходе логического элемента и N - номер строки по порядку. В соответствии со строками 1-3 таблицы истинности на один или оба входа х1 и х2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных р-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный р-n переход транзистора 3 тоже открыт, в итоге на базе транзистора 5 низкий уровень напряжения. За счет соответствующего значения напряжения источника 9 опорного напряжения обеспечивается требующееся значение силы электрического тока через транзистор 8. Этот ток создает на резисторе 6 напряжение, которое плюсом приложено к эмиттеру транзистора 5. Значением напряжения на резисторе 6 обеспечивается значение разности напряжений между базой и эмиттером транзистора 5 в районе порогового напряжения или близкое к нему значение. Тогда имеется малое значение силы коллекторного тока этого транзистора и малое напряжение на резисторе 4. Это малое напряжение не может обеспечить второе состояние триггера и включено между базой р-n-р транзистора 12 и через резистор 7 его эмиттером плюсом к эмиттеру и минусом к базе. Значением сопротивления резистора 7 обеспечивается состояние р-n-р транзистора 12 в районе порогового напряжения и тоже первое состояние триггера на транзисторах противоположного типа проводимости с учетом напряжения на резисторе 4, которое, как отмечено выше, имеет малое значение по абсолютной величине. Напряжение на резисторе 7 включено между базой и эмиттером р-n-р транзистора 12 минусом к эмиттеру и полюсом через резистор 4 к базе. Напряжение на резисторах 4 и 7 в базо-эмиттерной цепи транзистора 12 включены встречно и как отмечено ранее, имеют различные значения. Электрические токи транзисторов 10 и 12 триггера на транзисторах противоположного типа проводимости в первом состоянии создают на внешней нагрузке и на выходе у логического элемента напряжение уровня логического нуля (фиг. 2).

В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входа x1 и х2 логического элемента поступают напряжения уровня логической единицы. Оба базо-эмиттерных перехода транзистора 3 и его базо-коллекторный переход, как и ранее, открыты, тогда на базах транзисторов 3 и 5 высокий уровень напряжения. Это приводит к повышению силы электрического тока транзистора 5 и повышению напряжения на резисторе 4, которое минусом приложено к базе р-n-р транзистора 12 и поддерживает его открытое состояние. Небольшое и недостаточное препятствие этому оказывает напряжение на резисторе 7, которое минусом приложено к эмиттеру транзистора 12. Повышение силы электрического тока транзистора 5 приводит к уменьшению значения напряжения на базо-эмиттерном переходе транзистора 8, уменьшению силы коллекторного тока транзистора 8 и малому значению напряжения на резисторе 7. Это малое напряжение не может закрыть р-n-р транзистор 12, и в итоге оно и напряжение на резисторе 4 обеспечивают открытое состояние транзистора 12 и второе состояние триггера на транзисторах противоположного типа проводимости. Электрические токи транзисторов 10, 12 триггера на транзисторах противоположного типа проводимости во втором состоянии создают на внешней нагрузке и на выходе у логического элемента напряжение уровня логической единицы (фиг. 2).

Приведенные прототип и триггерный логический элемент И относятся к ЭСЛ-элементам (ЭСЛ - эмиттерно-связанная логика). Известно, что ЭСЛ-элементы имеют повышенное быстродействие [например, Гольденберг Л.М. Импульсные устройства. - М.: Радио и связь, 1981, стр. 57, раздел «Динмамические характеристики», абзацы 1, 2, …6].

Таким образом, в триггерном логическом элементе И сила электрического тока внешней нагрузки равна сумме силы токов двух транзисторов 10, 12, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| ТРИГГЕРНЫЙ СИНХРОННЫЙ D ТРИГГЕР | 2024 |

|

RU2827115C1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент ИЛИ | 2022 |

|

RU2797567C1 |

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| Триггерный асинхронный D триггер | 2021 |

|

RU2771668C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2022 |

|

RU2805495C2 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике, и, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Техническим результатом изобретения является повышение нагрузочной способности триггерного логического элемента И. Триггерный логический элемент И содержит p-n-p дополнительный транзистор, n-р-n двухэмиттерный дополнительный транзистор и дополнительный резистор. Эмиттер р-n-р дополнительного транзистора подсоединен к общему выводу третьего резистора и коллектора второго транзистора. База р-n-р дополнительного транзистора подключена к общему выводу первого резистора и коллектора первого транзистора, а также к коллектору третьего транзистора. Коллектор р-n-р дополнительного транзистора соединен и с базой третьего транзистора, и с одним из двух выводов пятого резистора. Свободный вывод пятого резистора подключен к свободному выводу четвертого резистора и их общий вывод образует относительно «земли» выход логического элемента. Коллектор n-р-n двухэмиттерного транзистора подсоединен к базе первого транзистора. Выводы эмиттеров n-р-n двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента. Между базой n-р-n двухэмиттерного транзистора и общим выводом выхода питающего постоянного источника напряжения, первого и третьего резисторов включен дополнительный резистор. 2 ил.

Триггерный логический элемент И, содержащий питающий постоянный источник напряжения, минусовой вывод которого соединен с общей шиной и заземлен, последовательно между собой соединенные первый резистор, первый n-р-n транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу (плюсовой вывод) питающего постоянного источника, свободный вывод второго резистора заземлен, последовательно включенные третий резистор и второй n-р-n транзистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода питающего постоянного источника, эмиттер второго транзистора подключен к общему выводу эмиттера первого транзистора и второго резистора, источник опорного напряжения, минусовой вывод которого заземлен, а плюсовой - соединен с базой второго транзистора, последовательно включенные третий n-р-n транзистор и четвертый резистор, соединенный с эмиттером третьего транзистора, также имеется пятый резистор, отличающийся тем, что в него введены р-n-р дополнительный транзистор, n-р-n двухэмиттерный дополнительный транзистор и дополнительный резистор, эмиттер р-n-р дополнительного транзистора подсоединен к общему выводу третьего резистора и коллектора второго транзистора, база этого дополнительного транзистора подключена к общему выводу первого резистора и коллектора первого транзистора, а также к коллектору третьего транзистора, наконец, коллектор приведенного дополнительного транзистора соединен и с базой третьего транзистора, и с одним из двух выводов пятого резистора, свободный вывод последнего пятого резистора подключен к свободному выводу четвертого резистора и их общий вывод образует относительно «земли» выход логического элемента, коллектор n-р-n двухэмиттерного транзистора подсоединен к базе первого транзистора, выводы эмиттеров двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента, между базой последнего транзистора и общим выводом выхода питающего постоянного источника напряжения, первого и третьего резисторов включен дополнительный резистор.

| RU 2760464 C1, 25.11.2021 | |||

| Триггерный логический элемент И | 2019 |

|

RU2728954C1 |

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Быстродействующий Д-триггер | 1990 |

|

SU1734195A1 |

| Устройство для измерения магнитной восприимчивости слабомагнитных материалов | 1986 |

|

SU1383240A1 |

| CN 113922658 A, 11.01.2022 | |||

| Устройство для управления электропневматическим тормозом железнодорожного транспортного средства | 1974 |

|

SU507471A1 |

Авторы

Даты

2023-08-28—Публикация

2022-06-29—Подача