1

Предлагаемое изобретение относится к области вычислительной техники и может быть использовано в вычислительных машинах с применением двоично-десятичного кода.

Известно арифметическое устройство, содержащее тетрады регистра результата, выход последней тетрады которого соединен с первыми входами сумматора и схемы «И, второй вход которой подключен к первому входу устройства, а выход - ко входу первой тетрады регистра результата, причем второй вход сумматора связан со вторым входом устройства, а выход - со входом регистра коррекции, выход которого соединен со входом схемы коррекции, и триггер управления.

Цель изобретения - повышение быстродействия устройства.

Это достигается тем, что в предлагаемом устройстве выход схемы коррекции соединен с первым входом первой дополнительной схемы «И, второй вход которой соединен с единичным выходом триггера управления, а выход - с первым входом дополнительной схемы «ИЛИ, выход которой подключен ко входу второй тетрады регистра результата, а второй вход - к выходу первой тетрады регистра результата, причем единичный и нулевой входы триггера управления соединены соответственно с выходами дополнительных - второй и третьей - схем «И, первые входы которых объединены и связаны с третьим входом устройства, а вторые входы соединены соответственно с четвертым и первым входами устройства.

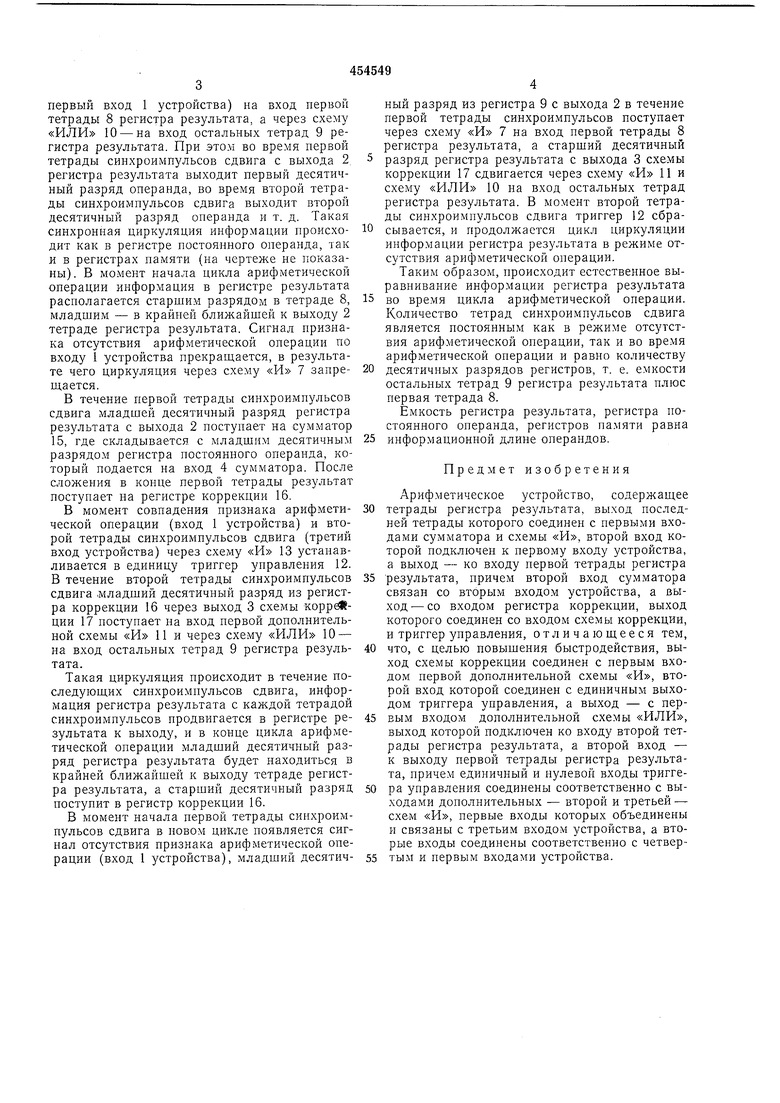

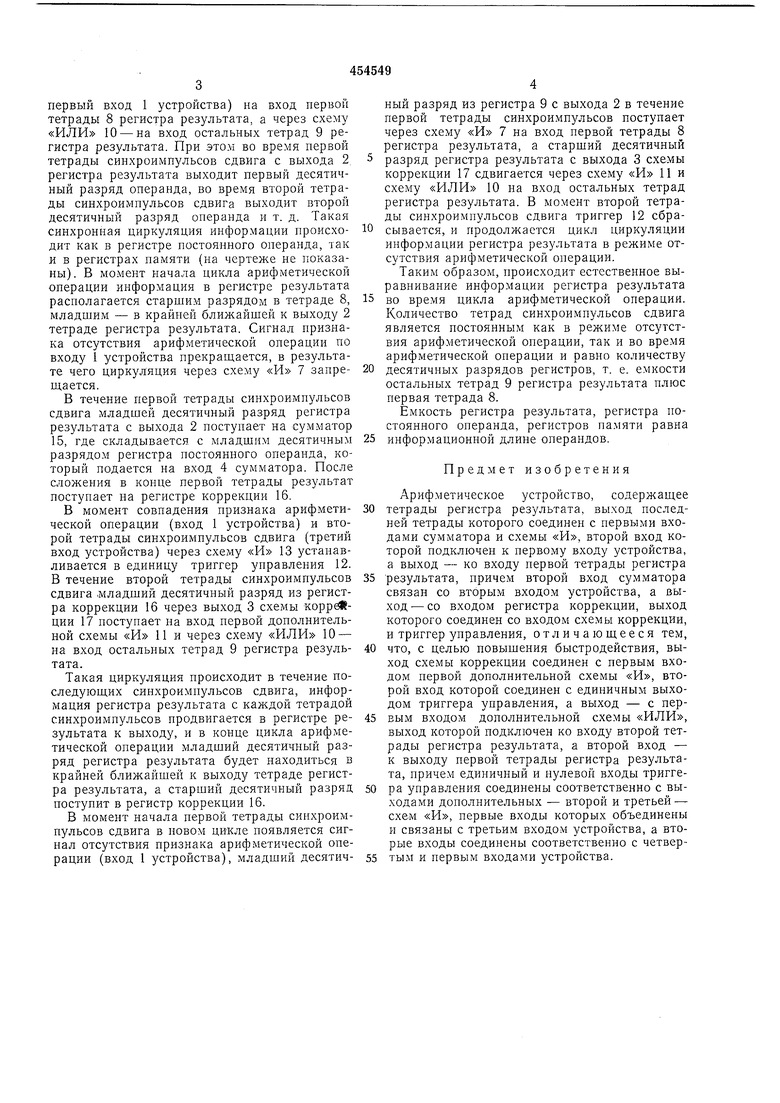

На чертеже изображена схема предложенного устройства.

На схеме: 1 - первый вход устройства для подачи признака отсутствия арифметической операции; 2 - выход регистра результата; 3 - выход устройства коррекции; 4 - второй вход устройства с регистра постоянного операнда на сумматор; 5 - третий вход устройства для подачи синхроимпульсов сдвига второй тетрады; 6 - четвертый вход устройства для подачи признака арифметической операции; 7 - первая схема 8 - первая тетрада; 9 - остальные тетрады регистра результата; 10 - схема 11 - первая дополнительная схема 12 - триггер управления; 13 - вторая дополнительная схема 14--третья дополнительная схема 15 - сумматор; 16 - регистр коррекции; 17 - схема коррекции. Хранение информации в первой тетраде 8 и

остальных тетрадах 9 регистра результата в режиме отсутствия арифметической операции происходит путем циркуляции ее с выхода 2 остальных тетрад 9 регистра результата через первую схему «И 7 (по признаку отсутствия

арифметической операции, поступающему на

первый вход 1 устройства) на вход первой тетрады 8 регистра результата, а через схему «ИЛИ 10 - на вход остальных тетрад 9 регистра результата. При этом во время первой тетрады синхроимпульсов сдвига с выхода 2. регистра результата выходит первый десятичный разряд операнда, во время второй тетрады синхроимпульсов сдвига выходит второй десятичный разряд операнда и т. д. Такая синхронная циркуляция информации происходит как в регистре постоянного операнда, так и в регистрах памяти (на чертеже не показаны). В момент начала цикла арифметической операции информация в регистре результата располагается старшим разрядом в тетраде 8, младшим - в крайпей ближайшей к выходу 2 тетраде регистра результата. Сигнал признака отсутствия арифметической операции по входу 1 устройства прекраш,ается, в результате чего циркуляция через схему «И 7 запрещается.

В течение первой тетрады синхроимпульсов сдвига младшей десятичный разряд регистра результата с выхода 2 поступает на сумматор 15, где складывается с младшим десятичным разрядом регистра постоянного операнда, который подается на вход 4 сумматора. После сложения в конце первой тетрады результат поступает на регистре коррекции 16.

В момент совпадения признака арифметической операции (вход 1 устройства) и второй тетрады синхроимпульсов сдвига (третий вход устройства) через схему «И 13 устанавливается в единицу триггер унравления 12. В течение второй тетрады синхроимпульсов сдвига младший десятичный разряд из регистра коррекции 16 через выход 3 схемы корреЖции 17 поступает па вход первой дополнительной схемы «И 11 и через схему «ИЛИ 10 - на вход остальных тетрад 9 регистра результата.

Такая циркуляция происходит в течение иоследуюших синхроимпульсов сдвига, информация регистра результата с каледой тетрадой синхроимпульсов продвигается в регистре результата к выходу, и в конце цикла арифметической операции младший десятичный разряд регистра результата будет находиться в крайней ближайшей к выходу тетраде регистра результата, а старший десятичный разряд поступит Б регистр коррекции 16.

В момент начала первой тетрады синхроимпульсов сдвига в новом цикле появляется сигнал отсутствия признака арифметической операции (вход 1 устройства), младший десятичный разряд из регистра 9 с выхода 2 в течение первой тетрады синхроимпульсов поступает через схему «И 7 на вход первой тетрады 8 регистра результата, а старший десятичный разряд регистра результата с выхода 3 схемы коррекции 17 сдвигается через схему «И 11 и схему «ИЛИ 10 на вход остальных тетрад регистра результата. В момент второй тетрады синхроимпульсов сдвига триггер 12 сбрасывается, и продолжается цикл циркуляции информации регистра результата в режиме отсутствия арифметической операции.

Таким образом, происходит естественное выравнивание информации регистра результата во время цикла арифметической операции. Количество тетрад синхроимпульсов сдвига является постоянным как в режиме отсутствия арифметической операции, так и во время арифметической операции и равно количеству десятичных разрядов регистров, т. е. емкости остальных тетрад 9 регистра результата плюс первая тетрада 8.

Емкость регистра результата, регистра постоянного операнда, регистров памяти равна информационной длине операндов.

Предмет изобретения

Арифметическое устройство, содержащее тетрады регистра результата, выход последней тетрады которого соединен с первыми входами сумматора и схемы «И, второй вход которой подключен к первому входу устройства, а выход - ко входу первой тетрады регистра результата, причем второй вход сумматора связан со вторым входом устройства, а выход- со входом регистра коррекции, выход которого соединен со входом схемы коррекции, и триггер управления, отличающееся тем, что, с целью повышения быстродействия, выход схемы коррекции соединен с первым входом первой дополнительной схемы «И, второй вход которой соединен с единичным выходом триггера управления, а выход - с первым входом дополнительной схемы «ИЛИ, выход которой подключен ко входу второй тетрады регистра результата, а второй вход - к выходу первой тетрады регистра результата, причем единичный и нулевой входы триггера управления соединены соответственно с выходами дополнительных - второй и третьей - схем «И, первые входы которых объединены и связаны с третьим входом устройства, а вторые входы соединены соответственно с четвертым и первым входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU798822A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

Авторы

Даты

1974-12-25—Публикация

1973-01-17—Подача