1

Изобретение относится к вычислительной технике, в частности, к электронным клавишным вычислительным ма ринам (ЭКВМ) с двоично-десятичной арифметикой..

Известно арифметическое устройство (АУ) электронной клавшлной вычислительной машины Искра-112, содержащее многоразрядный регистр сдвига, сумматор, схему коррекции, регистр коррекции, схекы И, ИЛИ, схему управления импульсами сдвига регистра. ставшей тетргщы 1 №огоразрядного регистра через схемы И, ИЛИ соеданен с входом младшей тетрады регистра и с входом сумматора. При отсутствии операции информация в регистре циркулирует с выхода старшей тетрады на вход младшей, циркуляция информации через сумматор запрещена. При выполнении операции запрещается циркуляция информац,ии с выхода регистра на вход и выход старшей тетрады подключается ко входу сумматора. Информация проходит через сумматор, регистр коррекции (длиной в тетраду), схему коррекции и поступает на вход младшей тетрады регистра. При этом происходит как бы удлинение регистра на тетраду (из-за регистра коррекции), следовательно.

5 епичивается количество сдвигов в регистре 1.

Однако число сдвигов информации ; при отсутствии операций я при операции различно. Поэтому АУ требует дополнительной схем управления импульсами сдвига, анализируккцей наличие операции, что увеличивает объем оборудования и усложняет структуру АУ. Наиболее близким к предлагаемому является АУ, содержащее ,су«матор, регистр коррекции, схему коррекции, многозарядный регистр, триггер управления, схемы И, ИЛИ и управляющие цепи. Для выравнивания количества сдвиIroB информации при отсутствии опера.ции с количеством сдвигов при выполнении арифметических операций, при которых информация в регистре должна пройти через сумматор, старшая тетрада регистра соединена с остальными тетрадами через дополнительный элемент ИЛИ. При отсутствии опергщии информация в регистре циркулирует с

5 выхода на вход через дополнительный элемент И, а запис с выхода сумматора на вход регистра запрещается триггером управления. При выполнении операции циркуляция информации с выхода

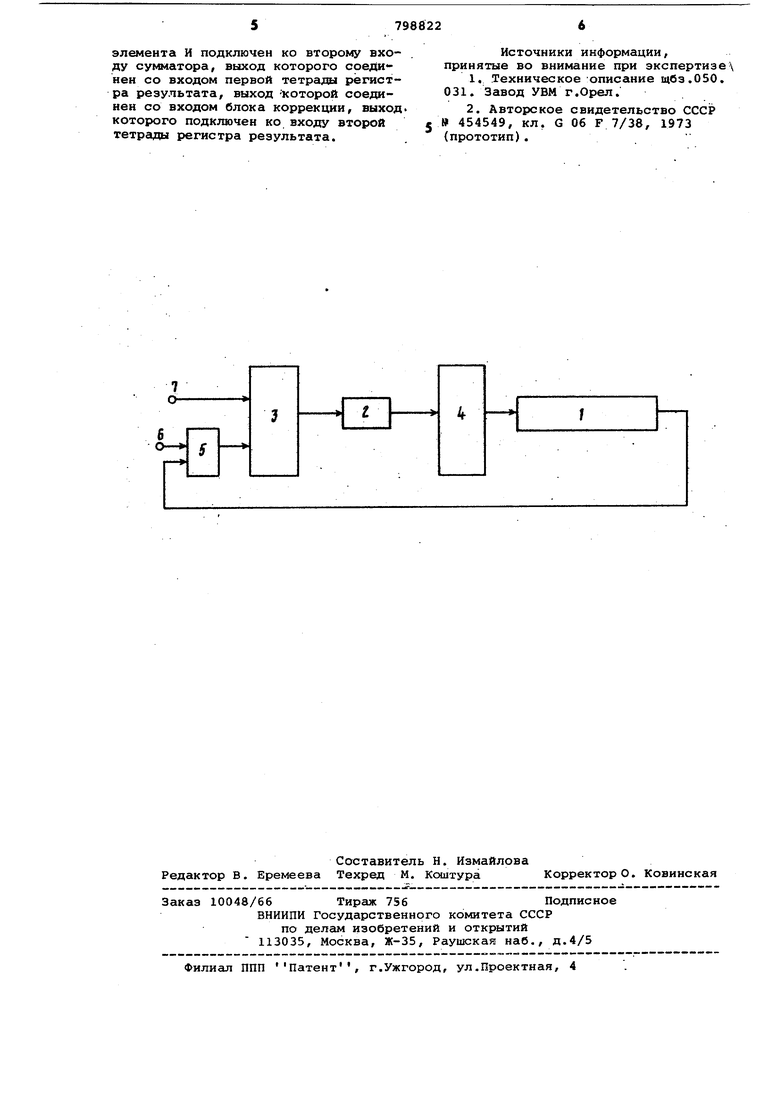

0 на вход регистра запрещается, а также запрещается триггером управления связь старшей тетрады с остальными тетрадами, ко входу которых через до полнительный элемент ИЛИ подключаетс выход схемы коррекции I.ZL Поскольку между сумматором и блоком коррекции включен тетрадный коррекции, количество сдвигов информации остается таким же, как и при отсутствии операции. Недостаток АУ - наличие дополнительных элементов И, ИЛИ, триггера управления, дополнительного тетрадного регистра коррекции и дополнительных связей. Цель изобретения - упрощение стру туры АУ и уменьшение оборудования. Поставленная цель достигается тем что в арифметическом устройстве, содержащем тетрады регистра результата сумматор, первый вход которого подключен к первому входу устройства, блок коррекции и элемент.И, первый вход которого соединен с выходом последней тетрады регистра результа та, а второй вход подключен ко второму входу устройства, выход элемента И подключен ко второму входу сумматора, выход которого соединен со входом первой тетради регистра результата, выход которой соединен со входом блока коррекции, выход которого подключен ко входу второй тетрады регистра результата. На чертеже представлена блок-схема устройства. Устройство содержит регистр результата, состоящий из п-тетрад регист ра 1 и первой тетрады регистра 2, .сумматора 3 блока 4 коррекции, элемента И 5. Арифметическое устройство работа следующим образом. Хранение информации в старшей те раде 2 и остальных тетрадах регистр 1 в режиме отсутствия арифметическо операции происходит путем циркуляци информации с выхода регист5)а 1 чере элемент И 5 на вход сумматора 3 при наличии признака на зходе б. На вто рой вход сумлатора по входу 7 в это случае второй операнд не подается. Тогда информация с выхода элемента И 5 поступает в сумматор 3, складывается с нулем и неизменная записыв тся в первую тетраду 2. С выхода первой тетрады 2 информация поступает на вход блока 4 коррекции. Так как коррекция не нужна, то информация не изменяется и с выхода блока 4 коррекции поступает на вход второ тетрады регистра 1 и т.д. В момент начала цикла арифметической операции информация в тетрадах регистра расположена всегда таким образом, что в первой тетраде располагается старший разряд, а на выходе регистра 1 находится мпадший разряд. Через элемент И 5 на сумматор 3 в течение первой тетрады поступает мпадший разряд регистра 1. По входу 7 на сумматор 3 в это же время поступает младший разряд второго операнда. В это же время с выхода первой тетрады 2 старший разряд через блок коррекции записывается в соседнюю, вторую тетраду регистра 1. На сумматоре 3 выполняется по-битно сложение младшего разряда регистра 1 с младшим разрядом второго операнда и сумма по-битно записывается в первую тетраду 2 . К началу второй тетрады в первой тетраде 2 регистра результата записана сумма младших разрядов. На сумматоре 3 начинается сложение вторых разрядов, а сумма младших разрядов, проходя через блок 4 коррекции, на котором при необходимости корректируется, записывается во вторую тетраду регистра 1. К началу старшей тетрады старший разряд, находившийся в начале цикла операции в первой тетраде 2, расположен в младшем разряде .регистра 1. В течение старшей тетрады старший разряд с выхода регистра 1 поступает на сумматор 3, складывается со старшим разрядом второго операнда и сумма записывается в первую тетргщу 2. Цикл выполнения арифметической операции закончен. В новом цикле (режим отсутствия арифметической операции) по входу 7 второй операнд на сумматор 3 не по- . дается и информация циркулирует с выхода регистра 1 на вход сумматора 3 и дальше на вход первой тетрады 2. Длина цикла АУ в режиме хранения информации и в режиме арифметической операции одинакова и постоянна и равна емкости тетрад регистра 1 плюс тетрада 2.. Исключение из структуры АУ дополнительных .элементов И, ИЛИ, триггера управления, регистра коррекции и использование старшего разряда регистра в качестве регистра коррекции позволяет упростить структуру устройства и уменьшить оборудование. Формула изобретения Арифметическое устройство, содержащее тетрады регистра результата, сумматор, первый вход которого подключен к первому входу устройства, блок коррекции и элемент И, первый вход которого соединен с выходом последней тетрады регистра результата, а второй вход подключен ко второму входу устройства, отличающееся тем, что, с целью уменьшения количества оборудования, выход

элемента И подключен ко второму входу сумматора, выход которого соединен со входом первой тетрадол регистра результата, выход -которой соединен со входом блока коррекции, выход которого подключен ко входу второй тетрады регистра результата.

Источники информации, принятые во внимание при экспертизе

1.Техническое описание щбз.050. 031. Завод УВМ г,Орел.

2.Авторское свидетельство CCCi 5 454549, кл, G 06 F 7/38, 1973

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Арифметическое устройство | 1973 |

|

SU454549A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для суммирования двоично-десятичных кодов | 1977 |

|

SU684542A1 |

| Арифметическое устройство с микропрограммным управлением | 1990 |

|

SU1797108A1 |

Авторы

Даты

1981-01-23—Публикация

1979-03-07—Подача