Предлагаемое устройство отиосится к области вычислительной техники и может быть исиользовано в арифметических устройствах Электройиых вычислительных машии.

Известны иоследовательп1 1е двоично-десятичные суммирующие устройства, содержащие иолусумматор-вычитатель, линии задержки, схемы «П, «ИЛИ, схемы задержки иа десятичный разряд, схему коррекции результата, иакоиитель.

Однако известные устройства достаточно сложны.

В иредлагаемом устройстве выход наконителя соедииеи со входом схемы анализа на нуль иервого слагаемого, второй вход которой связан со входом устройства, а выход - с иервым входом схемы «И, второй вход которой подключен к генератору одиночного импульса, третий вход - к доиолиительному выходу схемы коррекг1ии результата, а выход - ко второму входу схемы «ИЛИ, нричем выход второй схемы заде)жки иа десятичный разряд соединен со вторым входом иолусумматора-вычитателя.

Это иозволяет упростить устройство.

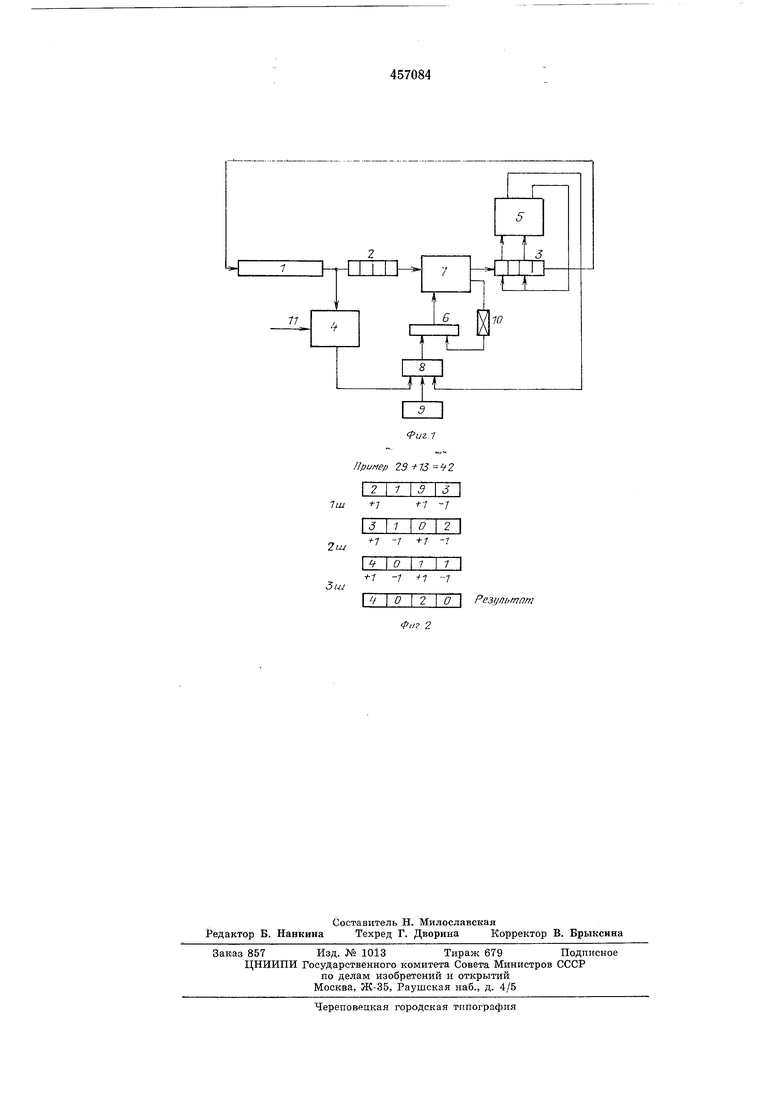

Па фиг, 1 ириведена функциональная схема предлагаемого устройства, где 1 - накоиптель; 2 - вторая схема задержки на десятичный разряд; 3 - иервая схема задержки иа десятичный разряд; 4 - схема анализа на нуль

2

иервого слагаелюго; 5 - схема коррекции результата; 6 - схема 7 - иолусумматор-вычнтатель; 8 - схема 9-генератор одиночного имиульса; 10 - лииия задсржки; 11 - вход устройства.

Выход накопителя 1 иодсоедииеи ко второГ схеме 2 задержки иа десятичный и ко входу схемы 4 аиализа иа нуль ие|)вого слагаемого, выход которой иодключеп к первому

входу схемы «И 8.

Выход второй схемы задер/кки иа десятичный разряд нодсоединен ко второму входу иолусумматора-вычнтателя 7, первый выход которого через линию задержки 10 иодключен

к схеме «ИЛИ 6, выход последией соедннеп с иервым входом иолусумматора-вычитателя. Второй выход полусумматора-вычитателя соединен с первой схемой 3 задержки на десятичный разряд, выходы которой иодс(,пиепы

ко входу накопнтеля 1 и входам схем1 1 5 коррекции результата, а выход схемы коррекции результата подключен ко входам nepBoii ехемы задержки и ко второму входу схемы «И 8. Выход генератора 9 одиночного имиульеа связан с третьим входом схемы «И 8.

Схема аиализа на нуль иервого слагаемого

ироверяет иа нуль первое слагаемое, постуиаюи;ее с выхода пакопнтеля. Если опо равно

пулю, то сигнал с выхода схемы анализа запрещает подачу единичного кода на второй вход полусумм агор а-вгэ1читатсл я.

Схема коррекции результата обнаруживает случай, когда сумма равна 10, осуп1;ествляет коррекцию суммы иутем стирания второго и четвертого разрядов, а также вырабатывает сигнал, заирещающий подачу на вход схемы «И 8 единичного кода в момент ирихода на вход нолусумматора-выч1ггате; я иервого елагаемого.

Генератор одиночного имнульеа для образования кода единицы. В данном устройстве сумма получается нутем последовательного прибавления стольких единиц к одному из слагаемых, сколько их содержится в другом слагаемом.

Рассмотрим работу суммирующего устройства на примере 29 + 13 42 (см. фиг. 2). Информация в накопителе расположена так, что первые разряды двух слагаемых расположены одно за другим, затем следуют один за другим вторые разряды слагаемых. С выхода накопителя младший разряд второго слагаемого поступает на вход второй схемы задержки на десятичный разряд и на вход схемы анализа на нуль иервого слагаемого. Так как с выхода схемы анализа на нуль в ириведеииом примере не иоявляется сигнала запрета, то на первый вход .юлусумматора-вычитателя поступает код единицы в момет подачи иа второй вход полусумматора-вычитателя разряда иервого слагаемого и вычитается из него. В следующий момент нрихода не ЭБОго разряда второго слагаемого иа вход сумматора к нему прибавляется единица. Получеииая сумма поступает на вход первой схемы задержки на десятичный разряд и ироверяется. В данном случае сумма равна 10 {см. фиг. 2), иоэтому оиа корректируется, т. е. в накоиитель заиисывается нуль млади1его разряда суммы. По иравилам сложения в двоичио-десятичиом коде в следующий разряд суммы должен быть прибавлеи перенос.

В данном устройстве это равиосильио заирету вычитания единицы из второго разряда иервого слагаемого. Это осуществляется путем

подачи сигнала занрета со схемы коррекции результата иа вход схемы «И.

в момент ирихода второго разряда второго слагаемого к нему ирибавляется единица. Во втором таге на выходе иакоиителя оиять появляется ие)вый разряд иервого слагаемого, не рав1и и | 0. Из него вычитается единица, а к иервому разряду следу1ои;его слагаемого добавляется единица. Второй разряд иервого слагаемого не нуль, следовательно, из иего вычитается единица в тот же разряд второго слагаемого.

Р1так, шаг за шагом, пока все разряды иервого слагаемого не равны «О.

И р е д м е т н з о б р е т е и и я

Последовательное двоичио-десятичное суммирующее устройство, содержащее полусумматор-вычитатель, первый выход которого соединен через линию задержки с первым входом схемы «ИЛИ, выход которой подключен к первому входу полусумматора-вычитателя, второй выход которого соединен с первым входом первой схемы задержки на десятнчный разряд, первый и второй выходы которой связаны соответственно с первым и вторым входами схемы коррекции результата, выход которой соединен со вторым н третьим входами первой схемы задержки на десятичный разряд, третий выход которой соединен со входом иакоиителя, схему «И и вторую схему задержки иа десятич1И)1Й разряд, оглича/ощееси тем, что, с целые уирощения устройства, выход накопителя соедииеи со входом схемы задержки иа десятичиый разряд и с иервым входом схемы анализа на нуль иервого слагаемого, второй вход которой связаи со входом устройства, а выход - с иервым вхо,Чом схемы «И, второй вход которой иодключеи к генератору одиночиого нмиульеа, третий вход - к доиолиительному выходу схемы коррекции результата, а выход-ко второму входу схемы «Р1ЛИ, причем выход второй схемы задержки иа десятичиый разряд соедииеи со вторым входом иолусумматора-вычнтателя.

7ш

2ш

3uj

пример 29 -1-73 2 2 1 Э 3

i-1 -7

+ -7 +1 -г 1 10 I I П

V-7 -7 +-1 -1 И/ I g I 2 О Рез1/Л1,тпп2 Фи 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство преобразования двоичного кода в десятичный | 1976 |

|

SU633013A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Устройство для суммирования | 1976 |

|

SU674018A1 |

| УСТРОЙСТВО Д.ПЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 1971 |

|

SU300449A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

Авторы

Даты

1975-01-15—Публикация

1972-01-17—Подача