1

f Изобретение относится к автоматике и вычислительной технике и может быть применено при построении устройства для передачи цифровой информации с контролем и испраБлением ошибок.

Известное устройство для передачи информации с коррекцией ошибок, содержащее входной дешифратор, соединенный через регистр сдвига с шифратором, счетчик разрядов числа, соединенный с регистром хранения номера искаженного разряда, подKJUO4eHHoro к дешифратору номера искаженного разряда, который соединен с регистром сдвига, и триггер, подключенный к входному дешифратору, характеризуется не- возможностью передачи и приема достоверной информации при сбоях в передающей и приемной частях устройства.

Цель изобретения - повышение достоверности передачи и приема информации,

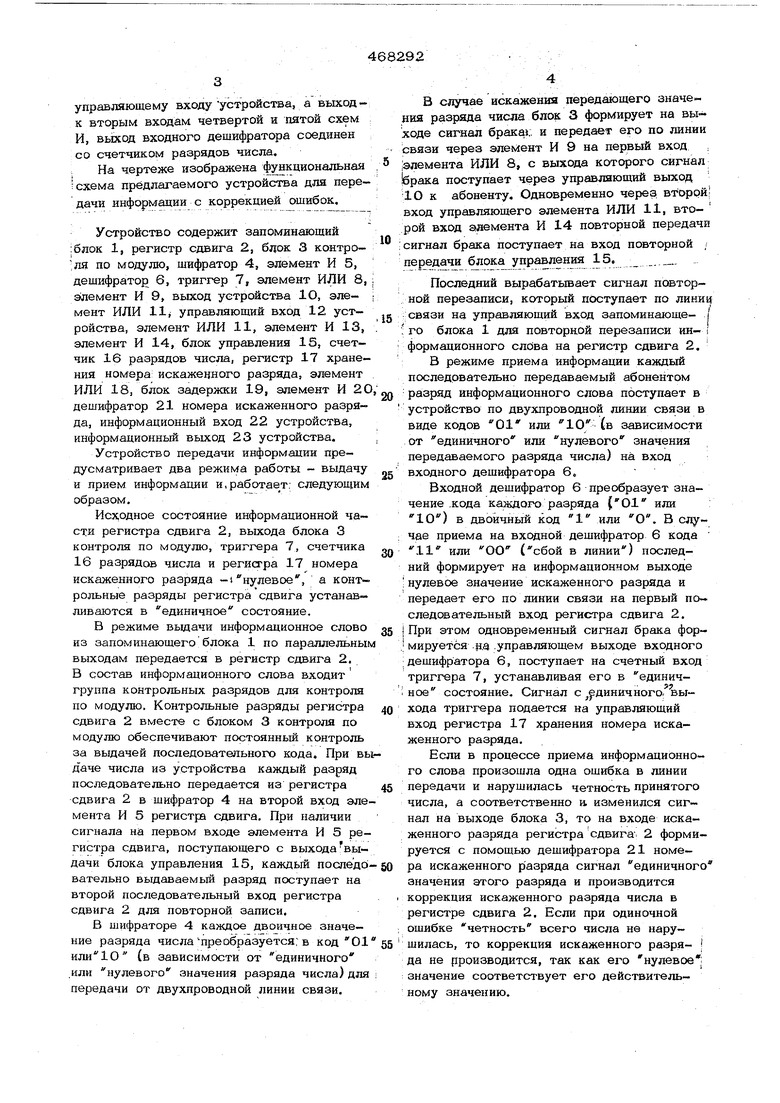

ДJШ этого предлагаемое устройство дополнительно содержит блок управления, запоминающий блок, блок контроля по моду- I лю, блок заде()жки, пять схем И и три схемы ИЛИ , причем выходы запоминающего олока срединены с соответствующими входами регистра сдвига, выходы которого соответственно соединены с запоминающим блоком, с блоком контроля по модулю и с первым входом первой схемы И , выход блока контроля по модулю соединен с пер выми входами второй и третьей схем И, первый выход блока управления соединен с регистром сдвига, счетчиком разрядов числа и триггером, второй выход, - с запоминающим блоком, а третий выход - с первыми входами четвертой и пятой схем И, первым входом первой схемы ИЛИ и вторым входом первой схемы И, вьгход которой подключен к регистру сдвига, выход счетчика разрядов числа соединен со вторым входом третьей схемы И и блоком задержки, выход которого подключен к второму входу первой схемы ИЛИ, выход последней соединен со вторым входом вто рой схемы И, выход которой подключен к первому входу второй схемы ИЛИ, второй вход которой соединен с триггером, а выход - с первым входом третьей схемы ИЛИ, второй вход которой подклпочен к управляющему входуустройства, а выходк вторым входам четвертой и пятой схем И, вькод входного дешифратора соединен со счетчиком разрядов числа. На чертеже изображена функциональная г схема предлагаемого устройства для передачи информации с коррекцией ошибок. Устройство содержит запоминающий :блок 1, регистр сдвига 2, блок 3 контро;ля по модулю, шифратор 4, элемент И 5, дешифратор 6, триггер 7, элемент ИЛИ 8, элемент И 9, выход устройства Ю, элемент ИЛИ 11; управляющий вход 12 устройства, элемент ИЛИ 11, элемент И 13, элемент И 14, блок управления 15, счетчик 16 разрядов числа, регистр 17 хранения номера; искаженного разряда, элемент ИЛИ 18, блок задержки 19, элемент И 20 дешифратор 21 номера искаженного разряда, информационный вход 22 устройства, информационный выход 23 устройства. Устройство передачи информации предусматривает два режима работы - выдачу и прием информации и,работае т: следующим образом. Исх,одное состояние информационной части регистра сдвига 2, выхода блока 3 контроля по модулю, триггера 7, счетчика 16 разрядов числа и регистра 17 номера искаженного разряда -(нулевое, а конт рольные разряды регистра сдвига устанавливаются в единичное состояние. В режиме вьщачи информационное слово из запоминающего блока 1 по параллельны выходам передается в регистр сдвига 2, В состав информационного слова входит группа контрольных разрядов для контроля по модулю. Контрольные разряды регистра сдвига 2 вместе с блоком 3 контроля по модулю обеспечивают постоянный контроль за выдачей последовательного кода. При вь даче числа из устройства каждый разряд последовательно передается из регистра сдвига 2 в шифратор 4 на второй вход эле мента И 5 регистра сдвига. При наличии сигнала на первом входе элемента И 5 регистра сдвига, поступающего с выходавыдачи блока управления 15, каждьш поспедо вательно выдаваемьш разряд поступает на второй последовательный вход регистра сдвига 2 для повторной записи, В шифраторе 4 каждое двоичное значение разряда числапреобразуется: в код 01 (в зависимости от единичного .или нулевого значения разряда числа) для передачи от двухпроводной линии связи. В случае искажения передающего значеия разряда числа блок 3 формирует на выоде сигнал 6paKas,. и передает его по линии вязи через элемент И 9 на первый вход , лемента ИЛИ 8, с выхода которого сигнал рака поступает через управляющий выход Ю к абоненту. Одновременно чере второй; вход управляющего элемента ИЛИ 11, второй вход элемента И 14 повторной передачи игнал брака поступает на вход повторной / передачи управления 15. Последний вырабатьгоает сигнал повторной перезаписи, который поступает по линии связи на управляющий вход запоминающе- го блока 1 для повторной перезаписи информационного слОва на регистр сдвига 2. В режиме приема информации каждый последовательно передаваемый абонентом разряд информационного слова поступает в устройство по двухпроводной линии связи в виде кодов 01 или 10 (в зависимости от единичного или нулевого значения передаваемого разряда числа) на вход входного дешифратора 6. Входной дешифратор 6 преобразует значение .кода каждого разряда (О1 или 10) в двоичный код 1 или О. В случае приема на входной дешифратор 6 кода 11 или ОО (сбой в линии) последний формирует на информационном выходе нулевое значение искаженного разряда и передает его по линии связи на первый последовательный вход регистра сдвига 2, При этом одновременный сигнал брака формируется ..а .управляющем выходе входного дешифратора 6, поступает на счетный вход триггера 7, устанавливая его в единичное состояние. Сигнал с ,,диничного. выхода триггера подается на управляющий вход регистра 17 хранения номера искаженного разряда. Если в процессе приема информационного слова произошла одна ошибка в линии передачи и нарушилась четность принятого числа, а соответственно и изменился сигнал на выходе блока 3, то на входе искаженного разряда регистра сдвига 2 формируется с помощью дешифратора 21 номера искаженного разряда сигнал единичного значения этого разряда и производится коррекция искаженного разряда числа в регистре сдвига 2, Если при одиночной ошибке четность всего числа не нарушилась, то коррекция искаженного разряда не рроизводится, так как его нулевое значение соответствует его действительному значению. Если при приеме информационного слова произошло более одного сбоя в линии передачи, то на выходе переполнения счет- | . ного триггера формируется сигнал брака j и через второй вход элемента ИЛИ 8 по- I ступает на управляющий выход 10 устройстаа для сообщения передающему або-1 венту о наличии сбоев и требования повторной выдачи предыдущего переданного информационного слова. Если сбой произощел в приемной части устройства, то на выходе блока 3 формируется сигнал брака и поступает на второй вход элемента И 9, После приема информационного слова устройством сигнал с выхода переполнения счетчика 16 разрядов числа через время задержки, которое формируется блоком задержки 19 и равно времени исправления устройством единичного сбоя в линии передачи, поступает через стробирующий элемент ИЛИ 18 на первый вход элемента И 9. На выходе элемента И 9 формируется ; сигнал брака, поступающий через элемент ИЛИ 8 на управляющий выход 10 устройства для сообщения передающему абоненту о наличии сбоев и требования повторной выдачи предыдущего информационного слова При поступлении сигнала от передающего абонента на управляющий вход 12 в режиме приема расшифровьгоается устройством как брак принятой информ,ации и устанавливается в исходное состояние приема предыдущего информационного слова. Предмет изобретения Устройство .для передачи информации с i коррекцией ошибок, содержащее входной дешифратор, соединенный через perHCTj) сдвига с шифратором, счетчик разрядов числа, соединедйьШ; с регистром хранения номера искаженного разряда, подключенного к дешифратору. jiQMepa искаженного разряда,...которьй соединен с регистром сдвига, и триг:гер;:;-яойключенный к входному дещифрдзро.ру,,.р-т личающеесятем, что, с 1ШЛЫР повышения достоверности передачи и приема информации, устройство дополнительно содержит блок управления, ; запоминающий блок, блок контроля по модулю, блок задержки, пять схем И и три схемы ИЛИ, причем выходы запоминающего блока соединены с соответствующими входами регистра сдвига, выходы которого соответственно соединены с запоминающим блоком, с блоком контроля по модулю и с первым входом первой схемы И, выход блока контроля по модулю соединен с первыми входами второй и третьей схем И, первый ВЫХОД блока управления соединен с регистром сдвига, счетчиком разрядов числа и триггером, второй выход- с запоминающим блоком, а третий выход - с первыми входами четвертой и пятой схем И, первым входом первой схемы ИЛИ и вторым входом первой схемы И, выход которой подключен к регистру сдвига, выход счетчика разрядов числа соединен со вторым входом третьей схемы И и блоком задержки, выход которого подключен к второму входу первой схемы ИЛИ, выход последней соединен со вторым входом второй схемы И, выход которой подключен к первому входу второй схемы ИЛИ, второй вход которой соединен с триггером, а выход - с первым входом третьей схемы ИЛИ, второй вход которой подключен к управляющему входу устройства, а выход - к вторым входам четвертой и пятой схем И, выход входного дешифратора соединен со счетчиком разрядов, числа.

8

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1290537A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

| Устройство для приема последовательного кода | 1982 |

|

SU1089608A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

J

L.

18

XI

12 о-

15

3 o

Авторы

Даты

1975-04-25—Публикация

1974-03-11—Подача