ны с соответствующими входами второй схемы формирования ошибки настройки, их сигнальные по функциям чувствительности выходы связаны с соответствующими сигнальными входами блока формирования сигнала настройки, со вторым входом которого соединен выход второй схемы формирования ошибки настройки, а соответствующие дополнительные выходы блока формирования сигнала настройки связаны с параметрическими входами дополнительных параметрически настраиваемых моделей. Блок формирования сигнала настройки содержит переключатель ошибки, выход которого через схему умножения, первый и второй последовательно включенные циклические переключатели подключен к соответствующим выходам блока формирования сигнала настройки, схему контроля . скорости изменения параметра, схему переключения, третий циклический переключатель и генератор тактовых импульсов, один из выходов последнего присоединен к управляющему входу первого циклического переключателя, другой - к управляющему входу третьего циклического переключи теля, выход которого связан со вторым входом схемы умножения, ее выход подключен .ко входу схемы контроля скорости изме«ения параметра, один выход которой соединен с первым управляющим входом второго циклического переключателя и одним из унравляющнх входов схемы переключения, другой вход которой, а также первый вход переключателя ошибки и второй управляющий вход второго циклического переключателя связать с управляющим входом блока формирования сигнала настройки. Второй выход схемы контроля Скорости изменения параметра подключен ко второму управляющему входу переключателя ошибки и управляющему выходу блока формирования сигнала настройки, первый и второй входы которого соединены соответственно с двумя входами переключателя ощибки, а сигнальные входы - с четырьмя соответствующими входами схемы переключения. Блок контроля качества настройки содержит схему деления и схему сравнения. Первый и второй входы блока контроля качества настройки через две цепи, состоящие из последовательно соединенных схемы определения модуля и сглаживающего фильтра каждая, связаны с двумя соответствующими входами схемы деления, выход которой соединен с одним входом схемы сравнения непосредственно, с другим - через последовательио соединенные схему управления запоминанием и схему запоминания. Выход схемы сравнения подключен к выходу блока контроля качества настройки, а его третий вход связан с унравляющим входом схемы управления запоминанием.

В связи с этим становится возможным: обеснечить устойчивость нроцесса благодаря адаптивности структуры модели к изменениям параметров входного сигнала и параметров объекта; уменьшить количество множительных устройств (до одного), что существенно упрощает конструктивно все устройство; уменьшить размерность вектора одновременно настраиваемых нараметров, что новышает скорость настройки и новышает устойчивость процесса; повысить точность определения характеристик системы по мере расширения спектра входного сигнала; при

небольшом числе моделей нолучить высокую точность приближения модели к объекту.

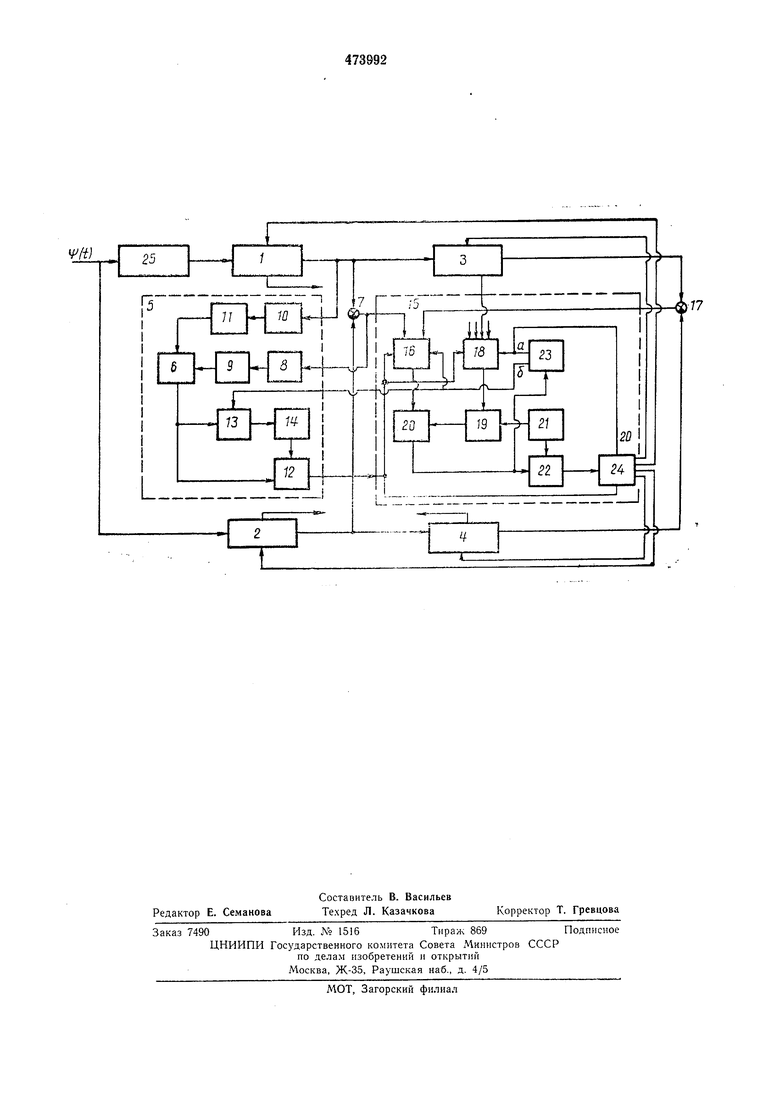

На чертеже изображена блок-схема устройства.

Устройство для определения параметров

линейных динамических объектов включает в себя набор моделей 1-4, представляющих собой линейные фильтры, онисываемые онераторами, причем

О-гР + «iP + gp

Wsfp),

W,(p ПР-}

(р) - W4(/;), f(p)

где р - оператор дифференцирования,

GO, Й1, аз - переменные параметры последовательных моделей, принимающие значения от нуля до максимально допустимого в зависимости от режима работы схемы;

6о, Ь, Ьч - переменные параметры параллельных моделей, изменяющиеся аналогнчно; f (/) - оператор фильтра с постоянными параметрами и порядком . Кроме того, под параметрическим входом моделей имеется ввиду схема управления параметрами, жестко соединенная с каждым параметром модели, состоящая из интегратора с бесконечной памятью и управляемого сопротивления «а выходе интегратора. Сигнальные по

функциям чувствительности выходы моделей представляют собой точки съема потенциалов в модели без нарушения нроцессов, протекающих в схеме. Число выходов по функциям чувствительности постоянно для каждой

модели и равно числу настраиваемых параметров, т. е. трем.

Блок контроля качества настройки 5 состоит из схемы деления 6, на один вход которой подключен выход первой схемы формирования ошибки настройки 7 через схему определения м.одуля 8 и сглаживающий фильтр 9, а второй вход подключен к выходу первой последовательной модели через аналогичную цепь, состоящую из схемы определения модуля 10 и сглаживающего фильтра II. Выход схемы деления 6 подключен на схему сравнения 12 и на схему управления запоминанием 13, выход которой подключен ко входу схемы запоминания 14.

Блок 15 формирования сигналов настройкн состоит из нереключателя ошибки 16, один вход которого связан с выходом схемы формирования ошибки настройки 7, а второй связан с выходом схемы формирования ошибки

настройки 17, и схемы переключения 18, соответствующие входы которой подключены к выходам моделей, каждый вход имеет три канала, по которым он жестко связан с тремя сигнальными выходами по функциям чувствительности соответствующей модели, а выход схемы переключения 18, тоже трехканальный, подключен на вход циклического переключателя 19. На один вход схемы умножения до блока 15 поступает сигнал с выхода переключателя ошибки 16, а на второй вход - сигнал с выхода циклического переключателя 19. Генератор тактовых импульсов 21 служит для управления циклическими переключателями 19 и 22. Схема контроля скорости измерения параметров 23 состоит из сглаживающего фильтра, узла определения модуля и порогового элемента, включенных последовательно, вход которой подключен к выходу схемы умножения 20, а выходы подключены на управляющие входы переключателя ошибки 16, схемы переключения 18, циклический переключатель 24 и на управляющий вход схемы управления запоминанием 13.

Устройство работает в следующей последовательности.

При первичном включении на входе переключателя ошибки 16 появляется сигнал со схемы формирования ошибки настройки 7, что соответствует отключению пары моделей 3 и 4. На выходе схемы переключения 18 появляются сигналы функций чувствительности по первому каналу, соответствующие функциям чувствительности параметров модели 1. На выходах а и б схемы контроля скорости изменения параметров 23 - пулевые значения сигналов. Генератор тактовых импульсов 21 находится в рабочем режиме с частотой следования импульсов ( где 0)1 - основная частота входного воздействия У (t.) Выход циклического переключателя 19 коммутирует функции чувствительности первого канала с частотой со, выход циклического переключателя 22 переключает с такой же частотой сигналы трех параметричес-ких цепей первого капала. Выход циклического переключателя 24 подключен к трем параметрическим входам модели 1. На выходе схемы сравнения 12 - положительный потенциал, поскольку на вход схемы сравнения через замкнутые контакты схемы управлепия запоминанием 13 и схемы запоминания поступает сигнал с выхода схемы деления 6.

При таком начальном состоянии схемы происходит настройка параметров модели 1. На параметрические входы модели 1 поступают сигналы до тех пор, пока суммарная скорость измеиеиия параметров ие упадет ниже установлеппого порога в схеме контроля скорости изменения параметров 23. При этом на выходе а появляется импульс, в результате которого переключаются схемы переключения 18 и циклический переключатель 24, осуществляя при этом подачу сигналов функций чувствительности по трем параметрам модели 2 на вход циклического переключателя 19 п подачу сигналов пастройки с выхода циклического переключателя 24

-на параметрические- входы модели 2. Процедура пастройки продолжается до следующего срабатывапия схемы контроля скорости изменения параметров 23 в функции скорости настройки параметров. При этом на

выходе а этой схемы появляется и.мпульс, а на выходе б - положительный иотенциал.

Импульс с выхода а перебрасывает схему переключения 18 и циклический переключатель 24 в положение, соответствующее третьему каналу. Потенциал с выхода б переключает вход схемы умножения 20 на выход второй схемы формирования ошибки настройки 17, а также прп помощи схемы управления запомипаиием 13 размыкает вход схемы запоминания 14. При этом на вход схемы сравнения 12 поступает текущее значение первой нормированной ошибки и зпачеиие ошибки в момент размыкания схемы управлеиия запоминаипем 13. Процедура пастройки и переход с пастройки модели 3 к пастройке моделп 4 апалогичны переходу от пастройки модели 1 к настройке модели 2. Это относится и к переходу модель 4 - модель 1. В случаях, когда текущее значение

нормированной ошибки становится больше, чем зафиксированное на схеме запоминания 14, сигиал на выходе схемы сравпеипя меняет полярность, схема управления запоминанием 13, переключатель ошибки 16, схема переключения 18 и циклический переключатель 24 переходят в начальное состояние.

Предмет изобретения

1. Устройство для определения параметров лппейных динамических объектов, содержащее две, подключенные первая параллельно, а вторая последовательно с объектом, параметрически настраиваемые oдeли, выходы которых подключены к соответствующим входам схемы формирования ошибки настройки, сигиальпые по фупкцпям чувствптельпости выходы параметрпчески настраиваемых моделей подсоедипеиы к сигиальиьпг входам

блока формирования сигнала пастройки, содержащего схему улгиожеппя, причем выходы блока формирования сигналов настройки связапы с параметрическими входами параметрически пастраиваемых моделей, выход схелип

формирования опп1бки пастройкп соедппеи с одним из входов блока формирования спгпала пастройкп, отличающееся тем, что, о целью повышения точности определения параметров и расширеиия функцпопальпых воз oжпocтeй, опо содержит две дополнптельпые параметрически иастраиваемые модели, причем одна из них связана последовательно с первой, а другая - со второй паралгетрически настраиваемой моделью, вторую схему

формирования ошибки иастройки и блок контроля качества настройки, первый вход которого связаН с выходом первой параметрически настраиваемой модели, второй вход - с выходом первой схемы формирования ошибки настройки, третий вход соединеи с управляющим выходом блока формирования сигналов настройки, а выход подключен к управляющему входу последпего ходы дополнительных параметрически страиваемых моделей соединены с coduv,. соответствующими входа.ми второй схемы формирования ошибки настройки, их сигнальные но функциям чувствительности выходы связаны с соответствующими сигнальными входами блока формирования сигнала настройки, ...г f гг , ,-, ,1-, л.(-,г-чт лгтг1гчtnrrтто, тгт со вторым входом которого соединен выхоул .J J 111JJ iV- -l W MJ. .-V r4 /-4t-i/ г /14/ л I I т /1л/-1Т-чЛТ о ЦТ IT а Г iriT.Tl LIT и П РТППЙ второй схемы формирования ошибки настройки, а соответствующие дополнительные выходы блока формирования сигнала настройки связаны с нараметрическими входами дополнительных параметрически настраиваемых моделей. 2. Устройство по и. 1, отличающееся тем, что блок формирования сигнала настройки содержит переключатель ошибки, выход которого через схему умножения, первый и второй последовательно включенные циклические нереключатели подключен к соответствующим выходам блока формирования сигнала настройки, схему контроля скорости изменения параметра, схему переключения, третий циклический нереключатель и генератор тактовых имнульсов, один из выходов носледнего присоединен к унравляющему входу первого циклического иереключателя, другой - к управляющему входу третьего циклического переключателя, выход которого пасвязан со вторым входом схемы умножения, ее выход нодключен ко входу схемы контроля скорости изменения нараметра, один выход которой соединен с первым управляющим входом второго циклического переключателя и одним из управляющих входов схемы переключепня, другой вход которой, а также первый вход переключателя ошибки и второй управляющий вход второго циклического переключателя связаны с управляющим входом блока формирования сигнала настройки, второй выход схемы контроля скорости изменения параметра нодключен ко второму управляющему входу нереключателя ошибки и унра ляющёмГ вь ходу Тг1ока Г1 ПТГТИ Т/ТТ ITirnr 1- г г, - формирования сигнала настройки непвый и Г v тт второй входы которого соединены соответственно с двумя входами переключателя ошибки, а сигнальные входы - с четырьмя соответствующими входами схемы переключения 3. Устройство по п. 1, отличающееся тем что блок контроля качества настройки содержит схему деления и схему сравнения причем нервый и второй входы блока контроля ( .Ч, „. качества настройки через две цепи, состоя щие из последовательно соединенных схемы определения модуля и сглаживающего фильтра каждая, связаны с двумя соответствующими входами схемы деления, выход которой соединен с одним входом схемы сравнения пепосредственно, с другим - через последовательно соединенные схему управления запоминанием и схему заиоминаиия, выход схемы сравнения нодключен к .выходу блока контроля качества настройки, а его третий вход связан с управляющим -входом схемы управления заиоминанием.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система идентификации параметров многомерного нелинейного динамического объекта | 1986 |

|

SU1385122A1 |

| Устройство для идентификации параметров объекта | 1981 |

|

SU987580A1 |

| Устройство для определения параметров линейных динамических объектов | 1977 |

|

SU642681A1 |

| Самонастраивающаяся система управления | 1983 |

|

SU1158974A1 |

| Устройство для определения статической характеристики нелинейности типа"насыщение" | 1973 |

|

SU470794A1 |

| Устройство для восстановления сигналов | 1988 |

|

SU1608706A1 |

| Самонастраивающаяся система управления | 1980 |

|

SU962852A2 |

| Система автоматического управления процессом полимеризации дивинил-стирольного каучука | 1987 |

|

SU1531069A1 |

| Самонастраивающаяся система управления с эталонной моделью | 1990 |

|

SU1827664A1 |

| Устройство для определения параметров линейных динамических объектов | 1977 |

|

SU684515A1 |

Авторы

Даты

1975-06-15—Публикация

1973-04-23—Подача