которой связан с выходом сумматора 4 и с входом второго делителя частоты 10, соединенного выходом со вторым входом блока управления .

В исходном состоянии запоминающий регистр 3 и делители частоты 9, 10 находятся в «нулевых состояниях, схемы совпадения 8, 11 закрыты. Импульсы с генератора 2 эталонной частоты поступают на первый вход блока I выделения периода и управления.

Работа устройства начинается с момента поступления на третий вход бло.ка управления I первого входного импульса, соответствующего началу периода 7 входного сигнала / . Блок управления 1 с первого выхода выдает сигнал через схему «ИЛИ 7 и линию задержки б на первые входы схем совпадения 5. Число, записанное в запоминающий регистр 3, переносится в обратном коде в сумматор 4. «Нулевое состояние запоминающего регистра 3 соответствует записанному в него числу 0. Число разрядов в запоминающем регистре и сумматоре - п.

Все триггеры находятся в «нулевом состоянии.

При переносе в сумматоре 4 записывается число , что соответствует «единичному состоянию всех триггеров сумматора. Сигнал с первого выхода бло.ка управления 1 также поступает на второй вход схемы совпадения 11 и открывает ее, поступая на сбросовую шину первого и второго делителей частоты 9, 10, подтверждает их «нулевое состояние.

Блок управления 1 начинает пропускать через себя импульсы частоты /о с генератора 2 эталонной частоты. Эти импульсы поступают со второго выхода блока управления 1 на вход сумматора 4. Первый импульс частоты /о переполнит сумматор. При переполнении сумматор с выхода выдает имлульс, который через открытую схему совпадения 11 поступает на выход устройства. Импульс с выхода сумматора 4 также поступает на вход второго делителя частоты 10 и через схему «ИЛИ 7 и линию задержки б - на импульсные входы схемы совпадения 5 для очередного переноса числа в обратном коде с запоминающего регистра 3 в сумматор 4. Та:К как в запоминающем регистре число О остается неизменным, то частота на выходе сумматора будет равна fo. Когда с выхода сумматора 4 пройдет число импульсов К, равное коэффициенту умножения устройства и коэффициенту деления второго делителя частоты 10, с выхода второго делителя поступит импульс на второй вход блока управления 1, который запирающим потенциалом с первого выхода закрывает схему совпадения II, а сигналом с третьего выхода открывает схему совпадения 8. Импульсы частоты fo начинают поступать через схему совпадения 8 на вход первого делителя частоты 9, имеющего коэффициент деления К. С выхода первого делителя

частоты частота - поступает на вход запоК

минающего регистра 3.

С выхода сумматора 4 импульсы продолжают поступать, но на выход они не проходят; так как схема совпадения 11 закрыта, выходные импульсы со второго делителя частоты 10

на блок управления 1 воздействия не оказывают, пока не поступит следующий входной импульс умножаемой частоты /j. . При поступлении второго входного импульса запирающий потенциал с третьего выхода блока

управления 1 закрывает схему совпадения 8. Поступление импульсов на запоминающий регистр 3 прекращается.

С первого выхода блока управления 1 поступит сигнал через схему «ИЛИ 7, линию

задержки 6 на импульсные входы схем совпадения 5, поступит сигнал на второй вход схемы совпадения 11 и на сбросовые входы первого и второго делителей частоты 9, 10. Делители частоты 9, 10 установятся в «нулевое состояние, а схема совпадения 11 откроется для прохождения импульсов с выхода сумматора 4 на выход устройства. Из запоминающего регистра 3 переносится число в обратном коде в сумматор 4.

Таким образом, за время Т. между двумя входными импульсами / (равное периоду входного сигнала) на выход устройства через схему совпадения I1 поступило К импульсов. Время, в течение которого проходили выходные импульсы через схему совпадения И, равно TO-К, где Го - период выходного сигнала генератора эталонной частоты. Время, в течение которого поступали импульсы частоты /о через схему совпадения 8 и первый делитель

частоты 9 на запоминающий регистр 3, равно

Г,-Го-/(.

Количество импульсов, поступивших на запоминающий регистр 3, определяется выражением:

Т х-Тр-К

(1)

- N + ,

То-К

где N - число импульсов, записанное в запоминающий регистр; ДЛ - дробная часть частного от деления.

После прихода второго входного импульса на вход блока управления 1 с запоминающего регистра 3 записанное в него число переносится в обратном коде в сумматор 4. В результате в сумматоре окажется число 2 -1-Л ; начальное число, которое было в сумматоре 4 перед переносом, на результат переноса не влияет.

Для переполнения сумматора 4 поступающей на него частотой /о (периодом Го) необходимо () импульсов. При переполнении с выхода сумматора поступает импульс через схему совпадения 11 на выход устройства, на второй делитель частоты 10 и на схему совпадения 5 для очередного переноса из запоминающего регистра 3 числа N в обратном коде. Частота на выходе сумматора и на выходе

устройства равна --- , а период - N+1

TO (N + 1). Сумматор в устройстве выполняет роль управляемого делителя частоты.

При поступлении с выхода сумматора 4 К импульсов второй делитель частоты 10 выдаст сигиал на второй вход блока управления 1, который закроет выходную схему совпадения 11 и откроет схему совпадения 8 до прихода следующего входного импульса.

Из формулы (1)

Т.,-То-К

Л + ДЛ

То-К

определим период Т входной частоты

Т,

-

То-К

Т

Л + 1 + AiV; Г., 7о /С (-V + 1+ АЛ )

Го К

To-K(N+)+To -/(AA.

Найдем время прохождения К выходных импульсов с периодом ToCV+l). Оно равно: To{N+)-K. Сравним период входного сигнала Г Го/C(V+1)+Го/CAjV с временем прохождения К выходных импульсов T,.K(N+l).

Эти промежутки времени отличаются друг от друга на Го-ТС-АЛ, где АЛ - дробная величина, минимальное значен-ие которой О, а максимальное стремится к 1.

В зависимости от значения АЛ выходные импульсы могут распределяться строго равномерно внутри периода входного сигнала при АЛ 0 (идеальный случай умножения) или с погрешностью при . Го() - период выходных импульсов; Го/С-АЛ - суммарная погрешность от некратности периодов входного и выходного сигналов.

При АЛ, близкой к 1, максимальная суммарная погрешность от некратности около

Т,-К.

Если , максимальная суммарная погрешность от некратности равна шагу квантования (периоду выходного сигнала Ту); при максимальная суммарная погрешность от некратности меньше шага квантования.

Суммарная ошибка от некратности, равная шагу квантования, допустима. При измерении выходной частоты fy она может увеличить показания частотомера на единицу младшего разряда.

При измерении выходной частоты появление максимальной погрешности маловероятно, так как АЛ/ должно быть близко к 1 и измерение оканчиваться в определенный момент во второй половине периода входного сигнала.

Для выполнения условия, когда возможно появление максимальной ошибки от некратности, равной квантованию, необходимо, чтобы , и, следовательно, максимальная выходная частота от умножения входной частоты должна в /С раз быть меньше частоты /о генератора образцовой частоты.

fo

/.

К

где , - выходная частота устройства.

Схема совпадения 8 открывается на время ГУ -7о-Л(ЛЧ1)Го-/(-АЛ. Так как Г -КАЛ Го-/С, то на запоминаюш,ий регистр

3 импульсь с первого делителя частоты 9 не поступят. Для поступления одного импульса е делителя частоты 9 необходи.мо, чтобы схема совпадения 8 была открыта на время То-К. Б установившемся режиме число, записанное в

запоминающий регистр, остается постоянным, Для разных входных частот оно различно.

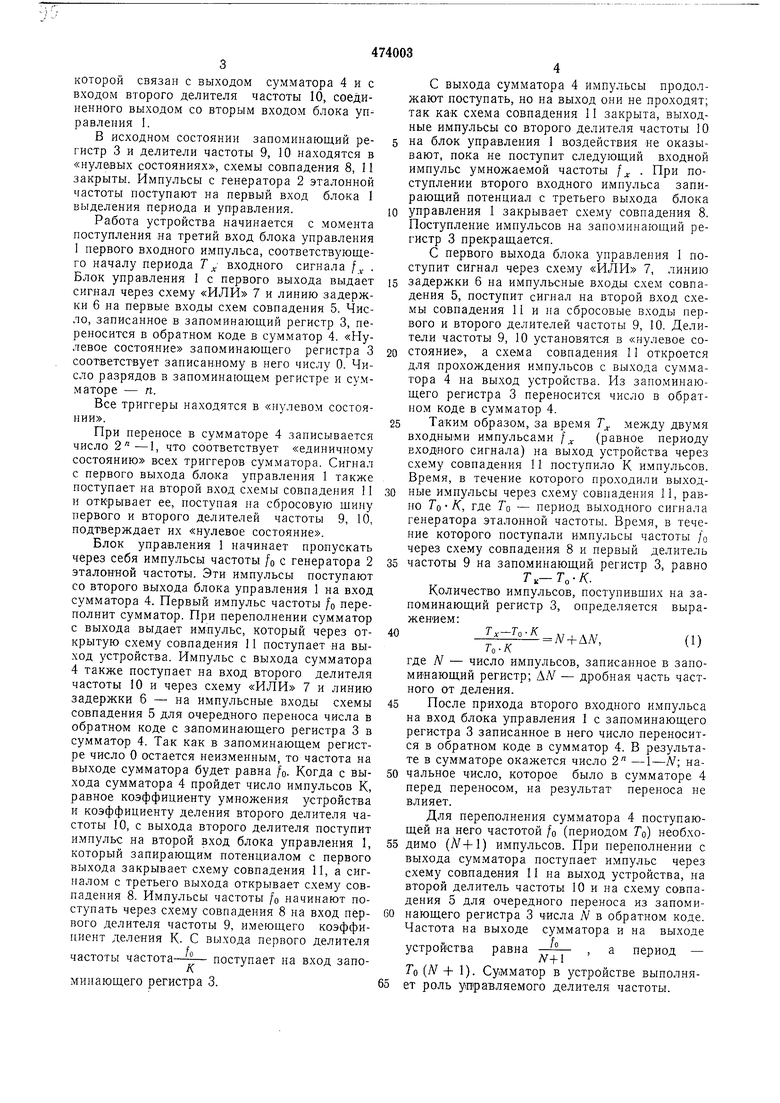

После поступления третьего входного имнульса последовательность работы узлов устройства повторяется. Таким образом, уже после прихода второго входного импульса частоты /с устройство начинает работать в установившемся режиме. Переходный процесс после подачи первого входного импульса составляет один период входного сигнала. После поступления первого входного импульса на выход поступило К выходных импульсов, но они были неравномерно расположены внутри периода Г . входного сигнала. С приходом второго входного импульса на выходе появится К

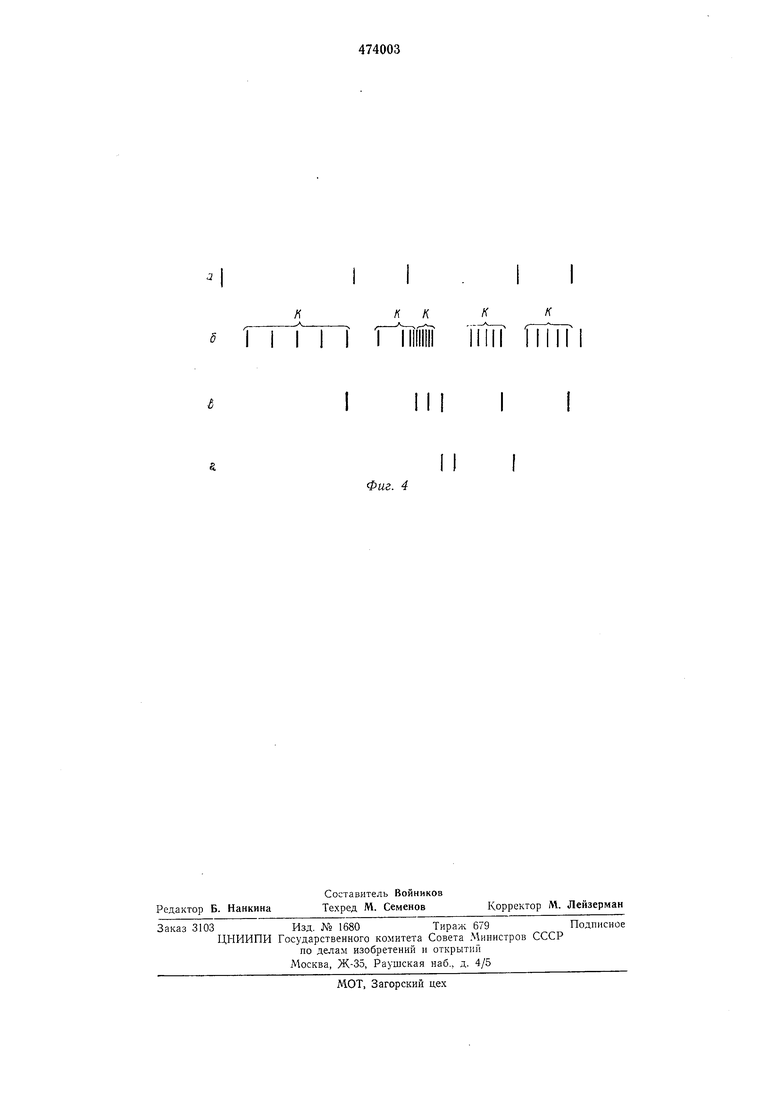

выходных импульсов, равномерно расположенных внутри периода Г,, входного сигнала. Диаграмма работы устройства после поступления первого входного импульса изображена на фиг. 2, где изображены:

а) входная частота f ;

б)выходная частота /у ;

в)выходные импульсы с второго делителя частоты 10;

г)выходные импульсы с первого делителя частоты 9.

В установившемся режиме за каждым входным импульсом на блок управления 1 поступает имлульс с выхода второго делителя частоты 10.

Рассмотрим работу устройства при изменении входной частоты в течение времени умножения.

Первый случай - уменьшение входной частоты (увеличение периода). Последующий входной импульс поступил через промел уток времени Т Т . Время, на которое откроется схема совпадения 8. будет равно: Г,. -Го K{N+l).

Количество и.мпульсов, прошедших на запоминающий регистр 3, определяется выражением

Г.у-Го-К(.У-И)

F + F,

(2) Го-Д

55 где F - количество импульсов, поступивших на запоминающий регистр; Af - дробная часть.

Определим величину Г. из формулы (2)

-()f + Af;

То-К

т ,

.: N + F + I + АРТа-к

T To-K(N + F+l) + To-K-&F. (3)

Б запоминающем регистре 3 при начальном установившемся режиме записало число Л . В результате изменения периода входного сигнала в запоминающий регистр 3 дописывается F импульсов. Новое число в запоминающем регистре - (Л + /). При переносе числа (N + 1) в обратном коде из запоминающего регистра 3 в сумматоре 4 запишется число 2 -Л-F-1. Сумматор начинает делить частоту /о на Л + У- + 1, следовательно, период выходного сигнала будет Го (N + F+l). Бремя, в течение которого поступает К. выходных импульсов, составит TQ- (N + F+) сравнивая его с выражением (3), видим, что оно отличается от нового периода Т на 7о /С Д, что соответствует погрешности некратности периодов входного и выходного сигналов.

Наступил установившийся режим. Нереходпой процесс в этом случае составляет один период входного сигнала, в течение которого К, выходных импульсов расположены неравномерно внутри периода входного сигнала.

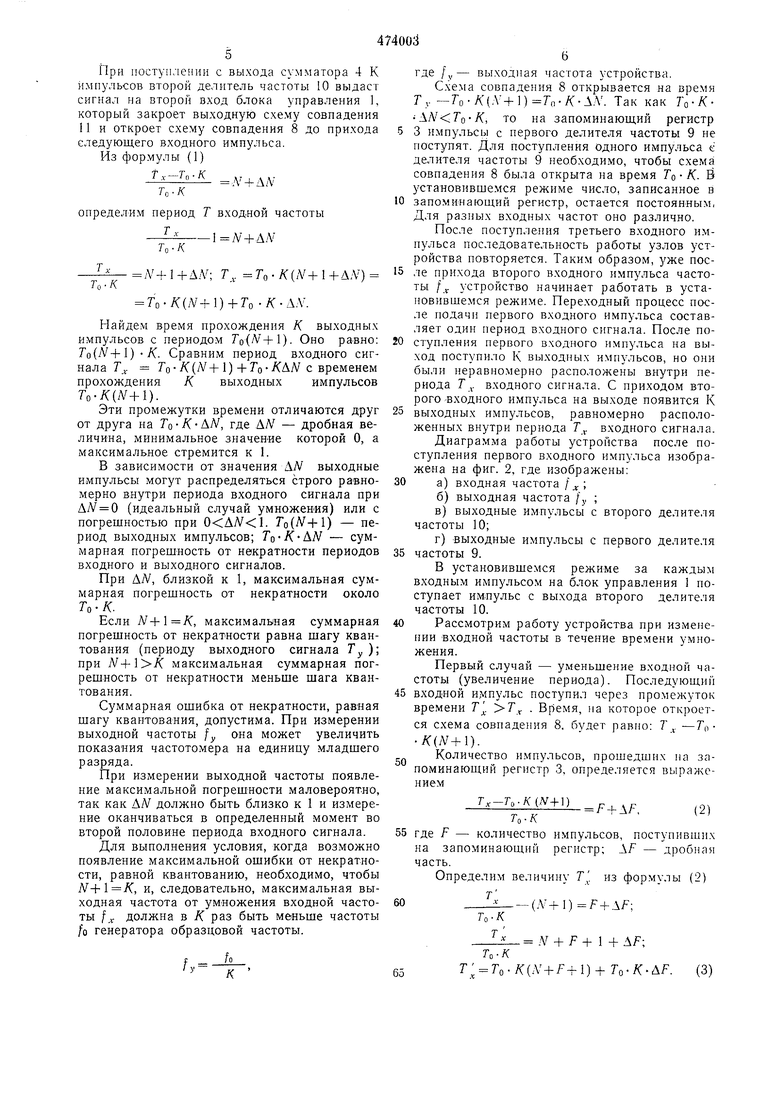

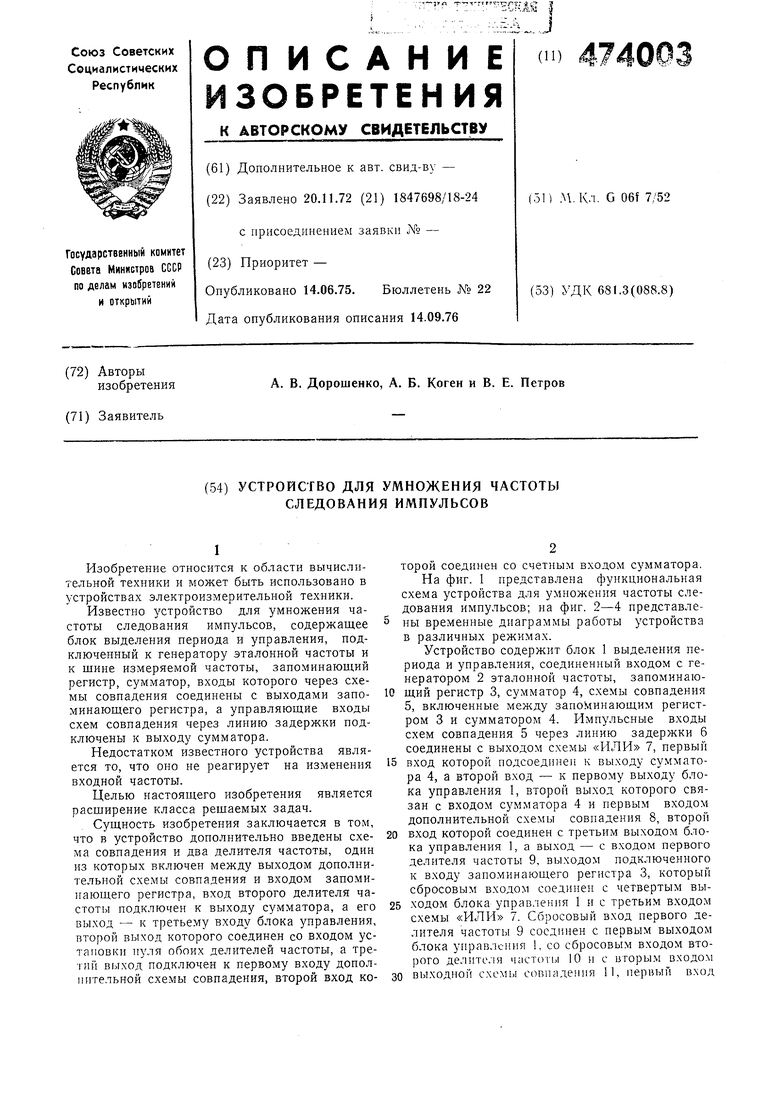

Диаграмма работы устройства для данного случая изображена на фиг. 3, где:

а)входная частота /у ;

б)выходная частота / ;

в) выходные импульсы со второго делителя частоты 10;

г) выходные импульсы с первого делителя частоты 9.

Рассмотрим работу устройства при увеличении входной частоты (уменьшении периода).

Нри уменьшении периода входной частоты порядок следования на входы блока управления 1 импульсов входпой частоты I и импульсов с выхода второго делителя частоты 10 изменяется. Друг за другом на вход блока управления 1 поступают два импульса входной частоты, импульс со второго делителя частоты 10 между ними не успевает пройти. При поступлении второго входного импульса блок управления 1 с четвертого выхода выдает сигнал, который сбрасывает запоминающий регистр 3 в «нулевое положение и, поступая через схему «ИЛР1 7 и линию задержки 6 на схе.мы совпадения 5, переписывает в обратном коде из запоминающего регистра число «О, соответствующее его «нулевому положению, в сумматор 4. На выходе сумматора 4 устанавливается частота /о. Второй делитель частоты 10 форсированно заполняется и выдает на второй вход блока управления 1 первый импульс, который воздействия на устройство не оказывает. Выходная схема совпадения 11 остается открытой, схема совпадения 8 - закрытой. На выход устройства поступит следующая пачка из К импульсов. Когда поступит К-й импульс, второй делитель частоты 10 выдаст второй импульс на второй вход блока управления 1.

Блок управления 1 закроет выходную схему совпадения И и откроет схему совпадения 8. На запоминающий регистр 3 с первого делителя частоты 9 начнут поступать импульсы до прихода следующего импульса входной частоты /J. на блок управления 1 и могут еще поступить несколько импульсов с выхода второго делителя частоты до поступления входного импульса частоты /, по они никакого воздействия не окажут. При поступлении импульса входной частоты блок управления 1 закрывает схему совпадения 8, переносит с

запоминающего регистра 3 число в обратном коде в сумматор 4, сбрасывает первый и второй делителИ в«пулевое положение, и открывает выходной вентиль 11. Далее повторяются уже известные операции. Проходят /С импульсов на выход устройства, поступает и.мпульс с выхода второго делителя частоты 10 па блок управления 1, который закрывает схему совпадения 11 и открывает схему совпадения 8. На запоминающий регистр 3 начинают поступать импульсы до момента прихода импульса входной частоты на вход блока управления 1. После этого начинается установившийся режим.

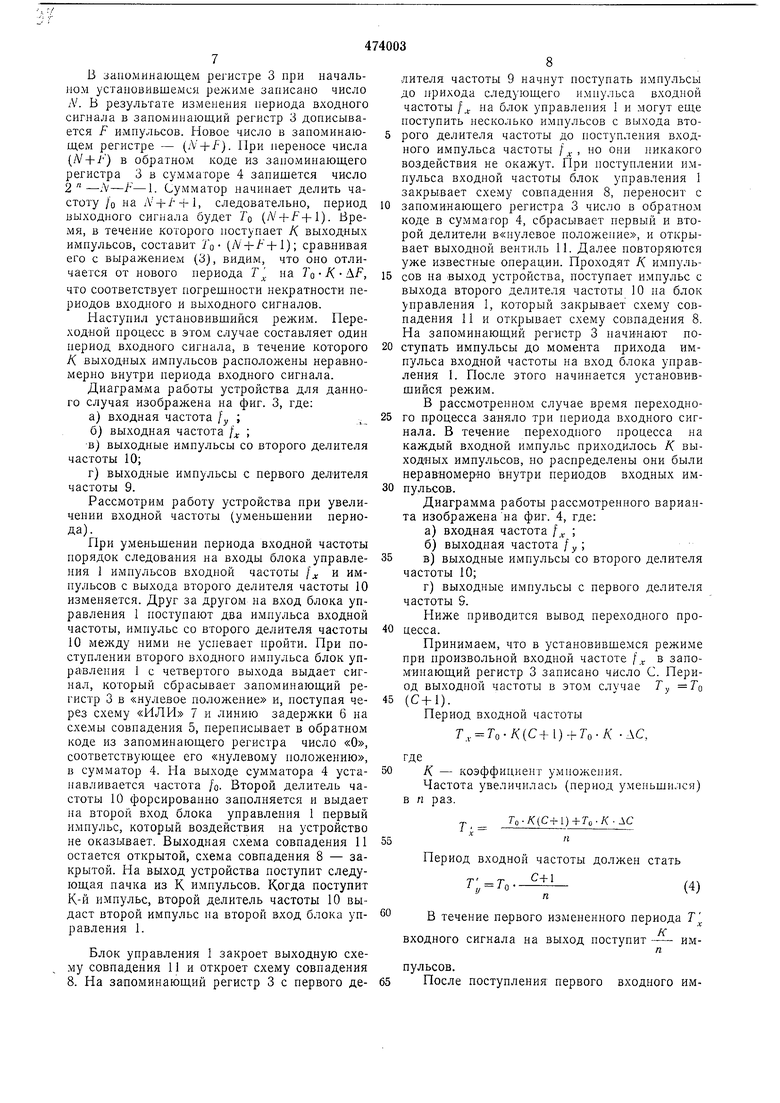

В рассмотренном случае время переходного процесса заняло три периода входного сигпала. В течение переходного процесса на каждый входной импульс приходи.тось /С выходных импульсов, но распределены они были нерав-номеряо внутри периодов входных импульсов.

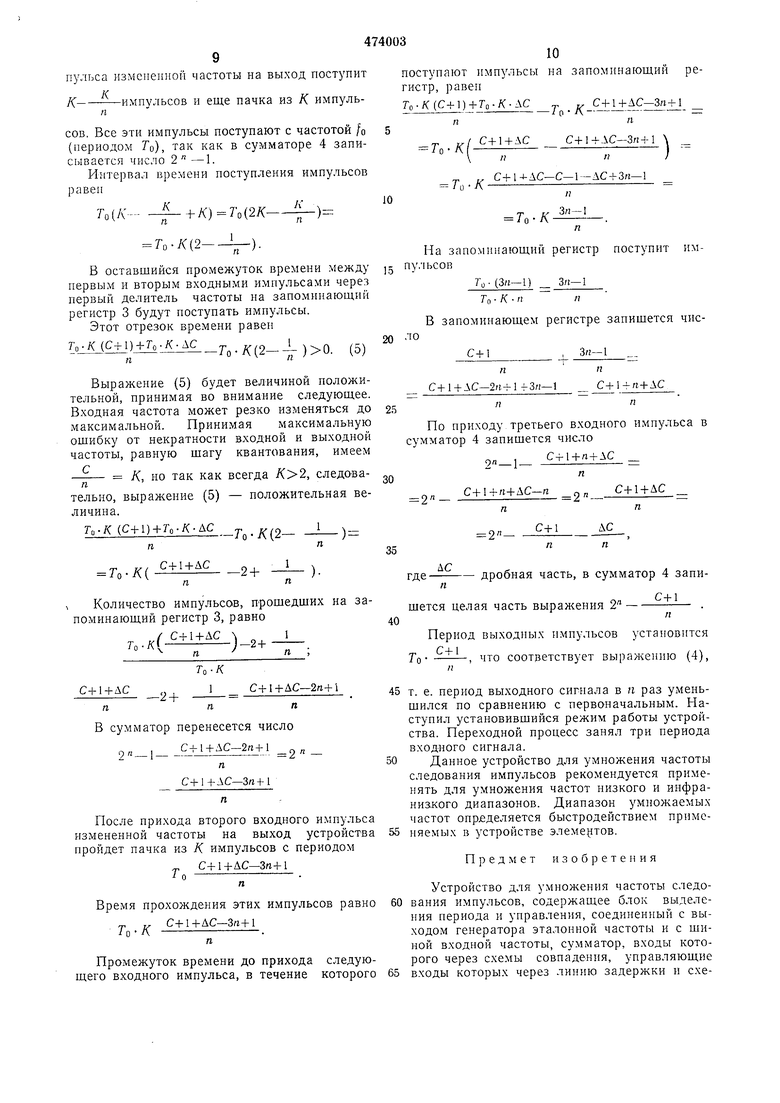

Диаграмма работы рассмотренного варианта изображена на фиг. 4, где:

а)входпая частота / ;

б)выходная частота /у ;

в) выходные импульсы со второго делителя частоты 10;

г) выходные импульсы с первого делителя частоты S.

Ниже приводится вывод переходного процесса.

Принимаем, что в установившемся режиме при произвольной входпой частоте f. в запоминающий регистр 3 записано число С. Период выходной частоты в этом случае Ту То (С+1).

Период входной частоты

Т,. То-К(С+{) + То.К -АС

где Д - коэффициеггг умножения.

Частота увеличилась (период уменьшился) в п раз.

„,Та-К(С+1)+То-К АС

Период входной частоты должен стать

С+1

,.(4)

В течение первого измененного периода Т

гг

входного сигнала на выход поступит имп

пульсов. После поступления первого входного импульса измснениой частоты на выход поступит

Д

/симпульсов и еще пачка из К импульп

сов. Все эти импульсы поступают с частотой /о (периодом Го), так как в сумматоре 4 записывается число 2 -1.

Интервал времени поступления импульсов равен

4-+К} Г,(2Кf

7-0 ( Го-/((2-В оставщийся промежуток времени между 5 первым и вторым входными импульсами через первый делитель частоты на запоминающий регистр 3 будут поступать импульсы. Этот отрезок времени равен TO К. (С+1) +Го К ЛС jt/f) --.п ,jlo-J(Z-- . Выражение (5) будет величиной положительной, принимая во внимание следующее. Входная частота может резко изменяться до максимальной. Принимая максимальную ошибку от некратности входной и выходной частоты, равную шагу квантования, имеем К, но так как всегда , следовательно, выражение (5) - положительная величина. Та-К (с-ы)-ьго-л:-дс г. i -7o.X{2С+1+ДС То-К( Количество импульсов, прошедших на запоминающий регистр 3, равно .„.()2+-L-. и« С+1+ДС-2fi+i С+1+ДС ппп В сумматор перенесется число с+1+м:-2/1+1 9 пj± i L;zr 2 - С+1+ДС-З/г+1 п После прихода второго входпого импульса измененной частоты на выход устройства пройдет пачка из К импульсов с периодом „ С+1+ДС-3rt+l 1 о .

Время прохождения этих импульсов равно 60 вания импульсов, содержащее блок выделеС+1+ДС-З/г+1Промежуток времени до прихода следую-рого через схемы совпадения, управляющие щего входного импульса, в течение которого 65 входы которых через линию задержки и схепоступают нмпульсы на запоминающий

регистр, равен

С+1+ДС-Зя+1

То-К(С+)+То-К-- С

Т ftт --o/t-r 1

Л ..

с+и-лс-Зги-:

С+1+ДС

То-К

ла

С+14-АС-С-1-АС + Зп-1

Го

К

II 3/1-1

7- г ол - 1 J О А

п

На запоминающий регистр поступит имУстройство для умнолсения частоты следония периода и управления, соединенный с выходом генератора эталонной частоты и с шиной входной частоты, сумматор, входы котольсов7о- () Зп-1 То-К-п п В запоминающем регистре запишется чисc+ n+ cС-Ц + ЛС-2rt l-b3/;-1 По приходу третьего входного импульса в сумматор 4 запишется число Ст-1-ьп+ЛС С+1-1-ДС C+l+rt-fAC-п - дробная часть, в сумматор 4 запиtiщется делая часть выражения . Период выходных импульсов установится Го- --, что соответствует выраженшо (4), т. е. период выходного сигнала в и раз уменьшился по сравнению с первоначальным. Наступил установившийся режим работы устройства. Переходной процесс занял три периода входного сигнала. Данное устройство для умножения частоты следования импульсов рекомендуется применять для умножения частот низкого и внфраНИЗ.КОГО диапазонов. Диапазон умножаемых частот опр деляется быстродействием применяемых в устройстве элементов, Предмет изобретения

му «ИЛИ соединены с выходом сумматора и с первым и вторым выходами блока выделения периода и управления, подключены к выходам запоминающего регистра, выходную схему совпадения, входы которой соединены соответственно с выходом сумматора и вторым выходом блока выделения периода и управления, четвертый выход которого соединен со счетным входом сумматора, отличающееся тем, что, с целью расширения класса решаемых задач, в него дополнительно введены схема совпадения и два делителя частоты.

f)(

первый из которых включен между выходом дополнительной схемы совпадения и входом запоминающего регистра, вход второго делителя частоты подключен к выходу сумматора,

а его выход - к третьему входу блока выделения периода и управления, второй выход которого соединен со входом установки нуля обоих делителей частоты, а третий выход подключен к первому входу дополнительной схемы совпадения, второй вход которой соединен со счетным входом сумматора.

(Риг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Калибратор фазы | 1988 |

|

SU1652938A1 |

| Устройство для умножения частоты следования периодических импульсов | 1981 |

|

SU1005285A2 |

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты | 1983 |

|

SU1151959A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1064477A1 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Фазочастотный преобразователь | 1979 |

|

SU873150A1 |

III

Фиг. 4

Авторы

Даты

1975-06-15—Публикация

1972-11-20—Подача