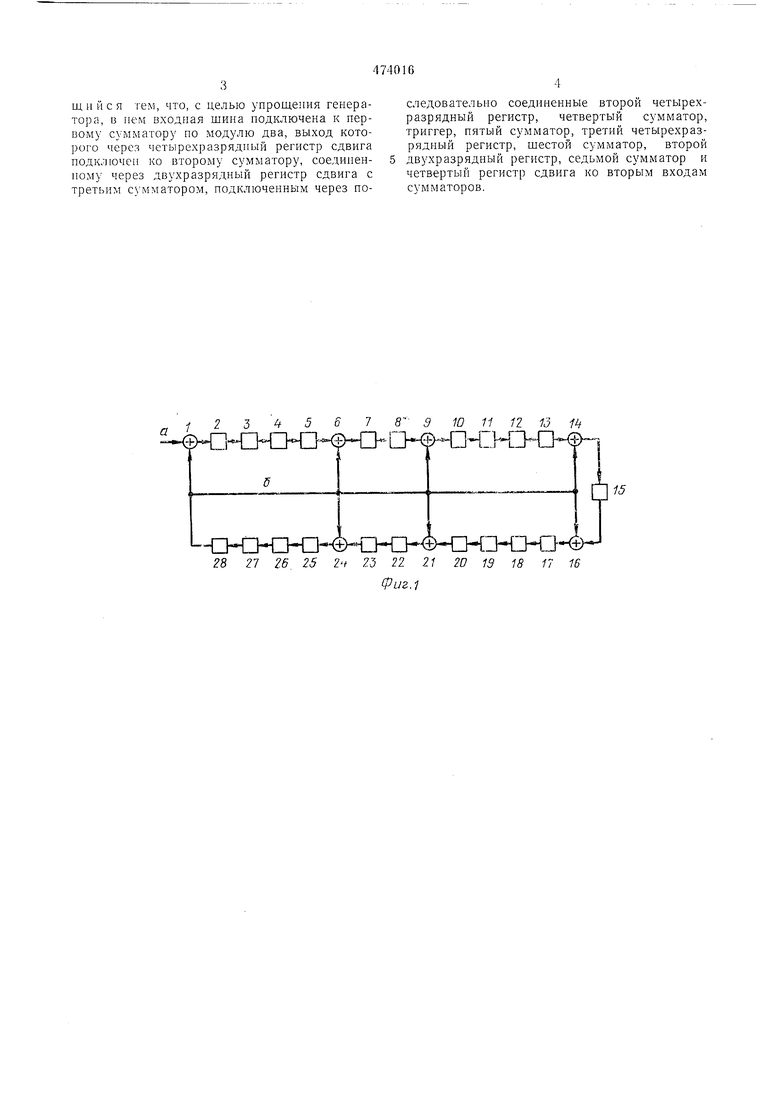

щ и и с я тем, что, с целью упрощения генератора, в нем входная шина подключена к первому сумматору но модулю два, выход которого через четырехразрядный регистр сдвига подключен ко второму сумматору, соединенному через двухразрядный регистр сдвига с третьим сумматором, подключенным через последовательно соединенные второй четырехразрядный регистр, четвертый сумматор, триггер, пятый сумматор, третий четырехразрядный регистр, шестой сумматор, второй двухразрядный регистр, седьмой сумматор и четвертый регистр сдвига ко вторым входам сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочного кода | 1985 |

|

SU1358098A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Устройство для моделирования нейрона | 1991 |

|

SU1831715A3 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Цифровой интерполятор | 1976 |

|

SU651317A1 |

| Преобразователь двоично-десятичныхчиСЕл B дВОичНыЕ C МАСшТАбиРОВАНиЕМ | 1979 |

|

SU822173A1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Многофункциональная логическая схема | 1973 |

|

SU490119A1 |

28 27 26 25 2f 2Ъ 22 21 20 19 18 17 16

Фиг.1

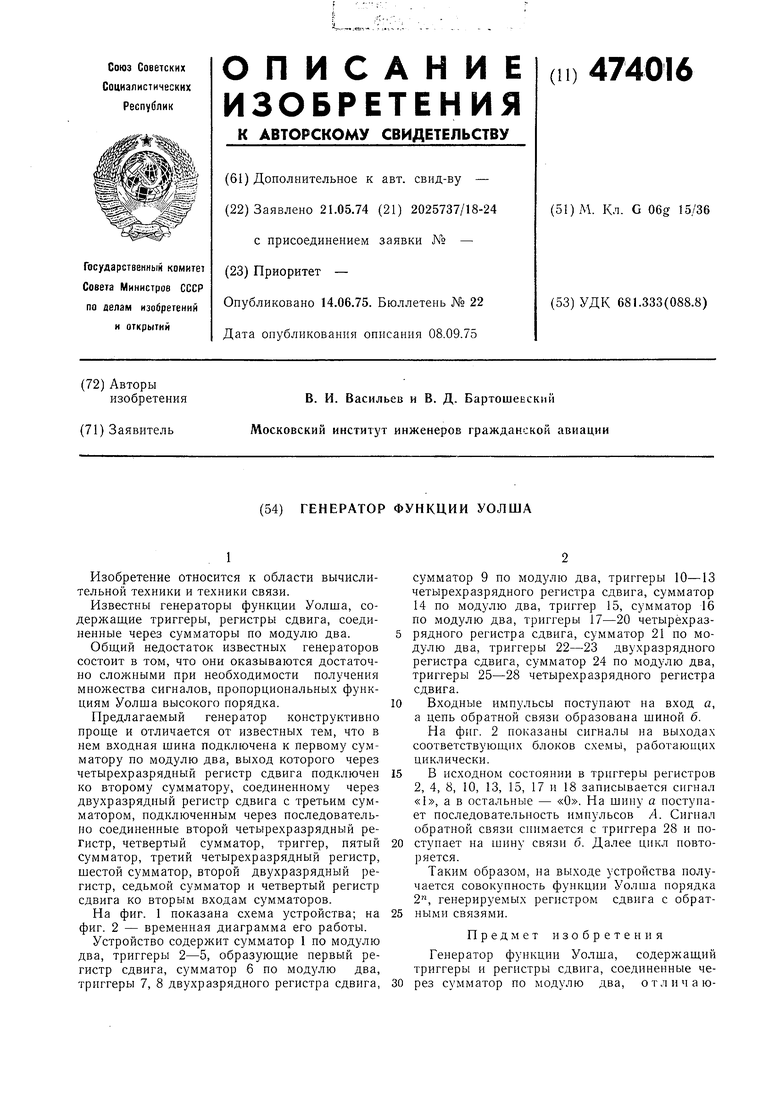

I I I I I I I I i I И I I I

&иг

1

.rL п.,.. .run.

2 J

5

6

7

8

9

10

11

12

/J

///

/5

16

17

18

19

20

21

1Г

22

23

24

25 26 27 28

I и и I I I I

.

Авторы

Даты

1975-06-15—Публикация

1974-05-21—Подача