1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении двоичнодесятичных преобразователей с введением масштабного коэффициента.

Известен преобразователь кодов с масштабирование:-, содержащий преоразователи весов разрядов и блоки сумгиирования l ,

Недостаток этого преобразователя состоит в низком быстродействии и большом объеме аппаратуры.

Наиболее близким к изобретению по технической сущности и схемному решению является преобразователь двоично-десятичных чисел в двоичные с масштабированием, содержащий сумматоры, причем входы преобразовател разделены на тетрады ..

Недостаток известного преобраз-ователя состоит в большом объеме аппаратуры, необходимом при реализации дцзобных масштабных коэффициентов с высокой точностью.

Цель изобретения - упрсвдение преобразователя .

Поставленная цель достигается тем, что преобразователь содержит шесть четырехразрядных сумматоров, два двухразряадных сумматора и три

элемента -ИЛИ, причем входы третьего и четвертого разрядов первой тетрады входов преобразователя соединены со входами первого элемента ИЛИ, выход которого подключен к входам первого и третьего разрядов первой группы входов первого сумматора,входы второго и четвертого разрядов первой тетрады входов преобразователя

0 соединены со,входами второго элемента ИЛИ, выход которого подключен к входу четвертого разряда первой группы входов первого сумматора, входы третьего и четвертого разрядов вто5рой тетрад : входов преобразователя соединены со входами третьего элемента ИЛИ, выход которого подключен к входу первого разряда первой группы входов второго и третьего суммато0ров, к входу четвертого разряда первой группы входов четнертого сумматора и к входу третьего разряда первой группы входов пятого сумматора, выходы первых разрядов второй и треть5ей тетрад входов преобразователя соединены с входами первого разряда первого двухразрядного сумматора, выход первого разряда ,cyм которого подключен ко входу четвертого

0 разряда второй группы входов первого сумматора и к входам переноса первого, четвертого и шестого сумматоров, входы вторых разрядов второй и третьей тетрад входов преобразователя соединены с входами второго разряда первого двухразрядного сумматора, выход второго разряда суммы ко-. Торого подключен ко входу переноса третьего сумматора, к входам первого и третьего разрядов первой группы входов четвертого сумматора и первого разряда первой группы входов шестого сумматора, а выход переноса первого двухразрядного сумматора подключен к входу второго разряда первой группы входов третьего сумматора, к входам третьего и четвертого разрядов первой группы входов четвертого сумматора, ко входу первого разряда пятого сумматора, а выходы переноса первого и второго сумматоров соединены с входами четвертого разряда третьего сумматора, выходы трех младших разрядов суммы которого подключены к выходам трех младших разрядов преобразователя, выход переноса третьего сумматора соединен с входом второго разряда второй группы входов четвертого сумматора, выходы переноса четвертого и пятого сумматоров соединены с входами четвертого разряда шестогосумматора, выход переноса которого соединен с входом переноса второго двухразрядного сумматора, выходы суммы которого и выходы суммы шестого сумматора подключены к- выходам соответствующих разрядов преобразователя, вход первого разряда первой тетрады входов преобразователя соединен с входами второго разряда первой группы и трет его разряда второй группы входов первого сумматора, вход второго разряда первой тетрады входов преобразователя соединен с входами первого и второго разрядов второй группы входов первого сумматора, вход третьего разряда первой тетрады входов преобразователя соединен с входами второго и четвертого разрядов первой группы входов второго сумматора и с входом третьего разряда первой группы входов третьего сумматора, входы четвертого разряда первой и третьего разряда второй тетрад входов jipeo6разователя соединены с входами вторых разрядов первой группы входов пятого и второй группы входов четвертого сумматоров соответственно,вход четвертого разряда второй тетрады входов преобразователя соединен с входом третьего разряда первой группы входов второго сумматора, с входом четвертого разряда первой группы входов пятого сумматора и третьего разряда шестого сумматора, входы двух младших разрядов третьей тетрады входов преобразователя соединены с соответствуювдами входами первой

группы входов второго двухразрядиого сумматора, входы второй группы которого соединены с входом логического нуля, вход переноса первого двухразрядного сумматора и вход второго разряда первой группы входов шестого сумматора соединены с входом логического нуля, разрядные выходы суммь первого и четвертого сумматоров соединены с входами соответствующих разрядов второй группы второго и пятого сумматоров соответственно, выходы трех старших разрядов суммы второго и пятого сумматоров соединены с входами трех младших разрядов второй, группы входов третьего и шестого сумматоров соответственно, вход переноса второго сумматора роединен с входом логической единицы, выход четвертого разряда третьего сумматора соединен с входом первого разряда второй группы входов четвертого сумматора, выход первого разряда пятого сумматора соединен с выходом четвертого разряда преобразователя.

В основе работы предлагаемого устройства лежит следующий принцип.

Преобразование осуществляется путем суммирования с учетом возникающих переносов значений тех разрядов входного числа, произведение веса которых на масштабный коэффициент,представленное в виде суммы степеней числа 2, содержит члены с одинаковыми степенями числа 2. Учитывая, что масштабный коэффициент может иметь дробную величину, погрешности округления величин произведений выбирают такими чтобы сумма погрешностей одного знака в наихудшем случае не превышала половины веса младшего разряда входного числа. ,

При этом исключается аппаратурная реализация операции умножения преобразованного числа на масштабный коэффициент К, что позволяет значительно упростить реализацию при дробньих значениях коэффициента К и увеличить быстродействие. Погрешность масштабирования не ухудшается, хотя погрешности округления произведенийвесов разрядов входного числа на масштабный коэффициент значительно больше, чем погрешность округления коэффициента К при реализации преобразования сочетающего преобразование чисел с умножением на масштабный коэффициент Действительно, если погрешность масштабирования недолжна превышать /2 веса младшего разряда кода входного числа, то Пограиность округления отдельного произведения Sn должна быть в п раз меньше, где п-число разрядов входного числа. Так как погрешности округления произведений могут иметь разные знаки, погрешность бП в наихудшем случае должна быть лишь в п/2 раз меньше веса младшего разряда. Если вес младшего разряда

код.) ихолпого числа равен 1, то погришнсхггь

Ясно, что эта величина значительно больше погрешности округления коэффициента К при аппаратурной реализации операции умножения

R -JL

,

Q.2

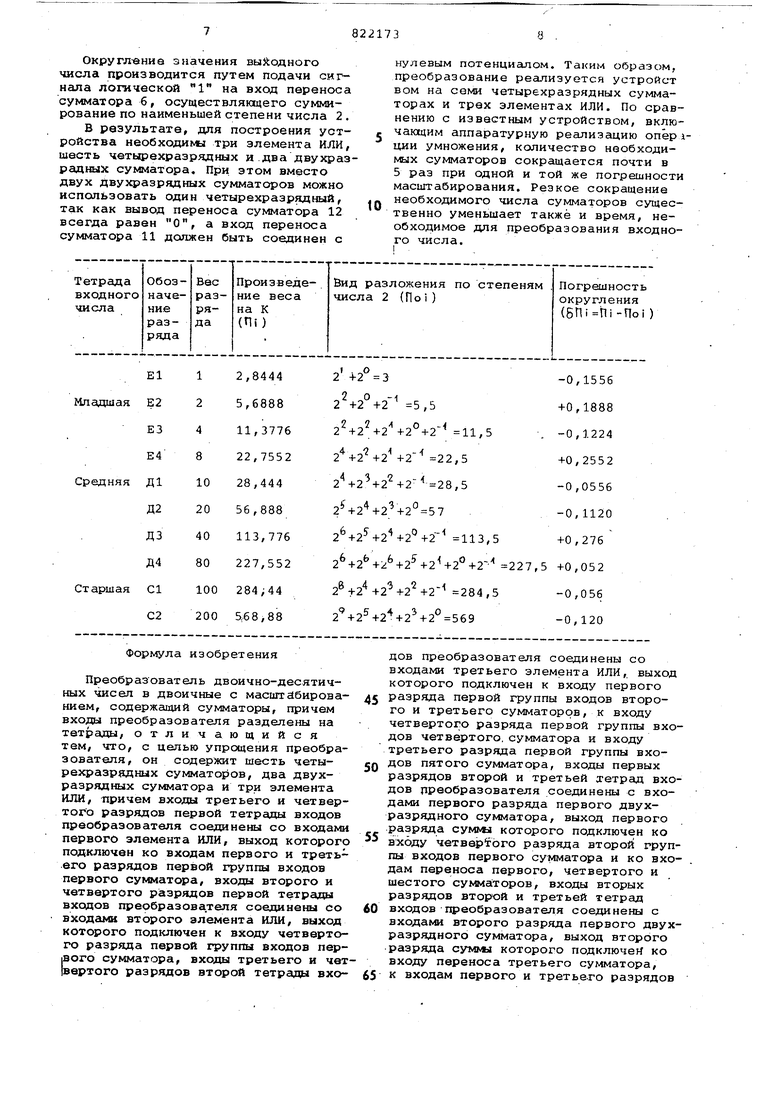

а следовательно, для представления произведения веса разряда входного числа на коэффициент К в виде суммы степеней числа 2 требуется значительно меньшее число членов. При этом построение cxeML-j устройства включает следующие этапы: составление таблицы произведений весов разрядов входного числа на известный масштабный коэффициент, представление произведений в виде суммы различных степеней числа 2 с учетом допустимой погрешности округления, составление схеми устройства в соответствии с полученными разложениями так, чтобы значения разрядов входного числа, в разложении произведения которых на коэффициент К есть одинаковые степени числа 2, суммировались в порядке возрастания степени числа 2 и с учетом переносов

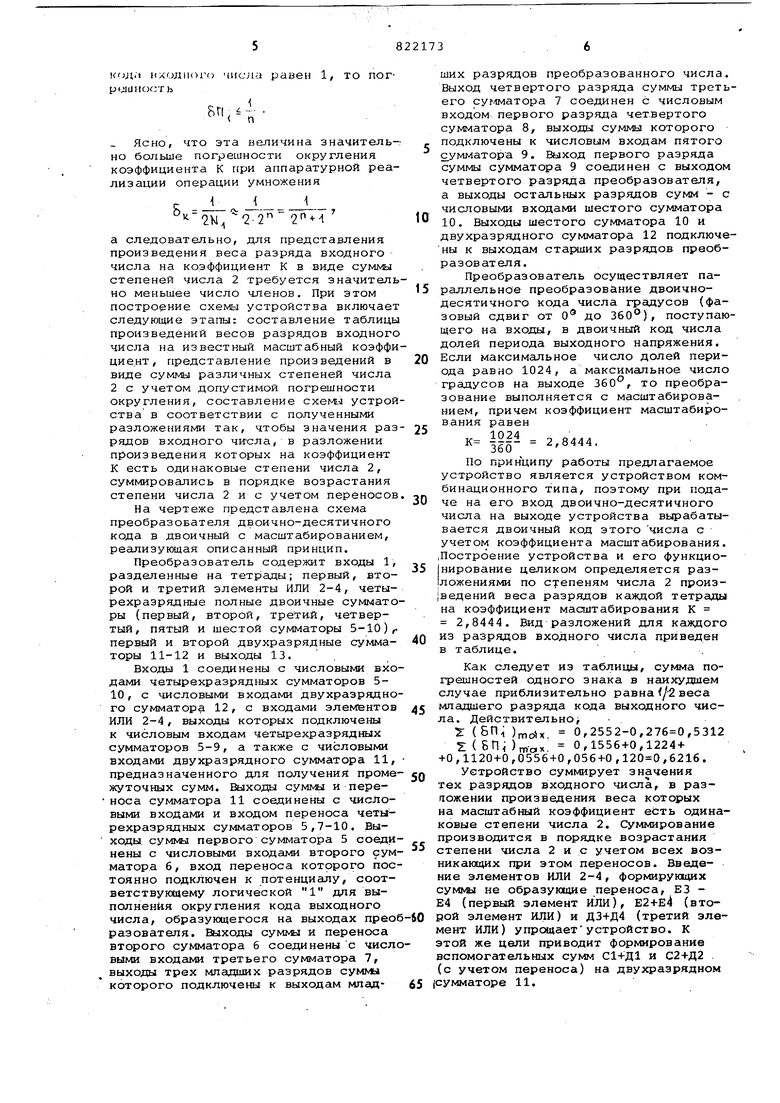

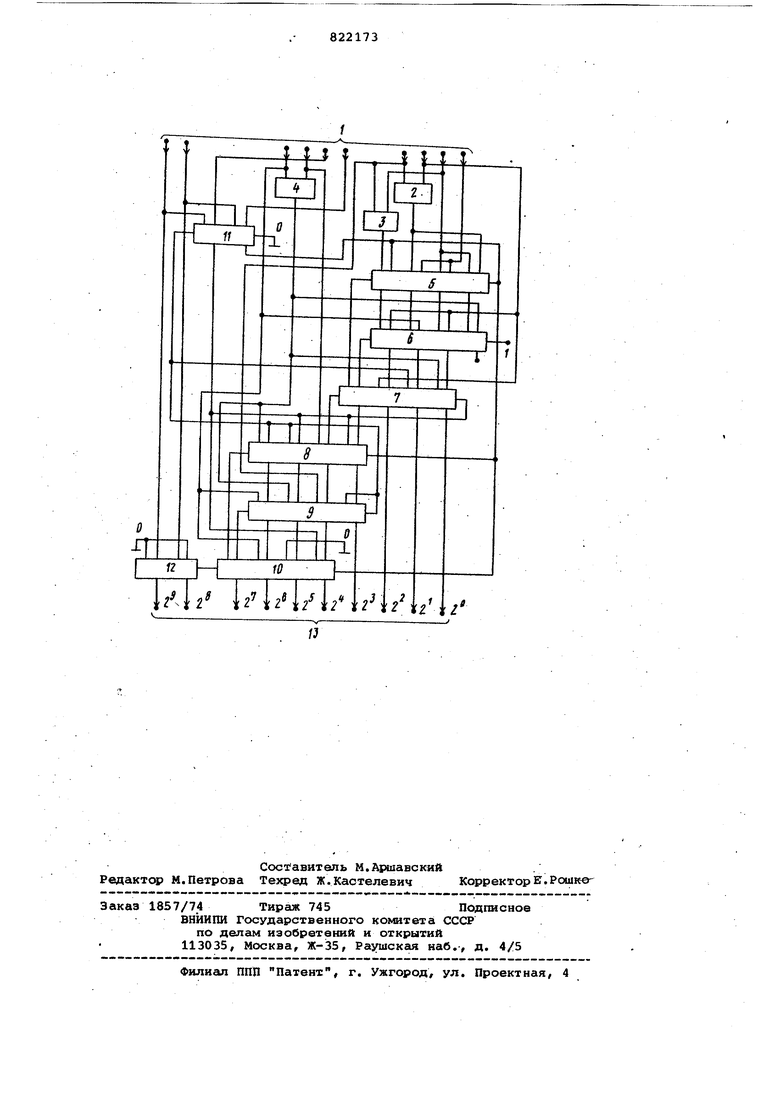

На чертеже представлена схема преобразователя двоично-десятичного кода в двоичный с масштабированием, реализующая описанный принцип.

Преобразователь содержит входы 1, разделенные на тетрады; первый, второй и третий элементы ИЛИ 2-4, четырехразрядные полные двоичные сумматоры (первый, второй, третий, четвертый, пятый и шестой сумматоры 5-10),. первый и второй двухразрядные сумматоры 11-12 и выходы 13.

Входы 1 соединены с числовыми входами четырехразрядных сумматоров 510, с числовыми входами двухраэрядного сумматора 12, с входами элементов ИЛИ 2-4, выходы которых подключены к числовым входам четырехразрядных сумматоров 5-9, а также с числовыми входами двухразрядного сумматора 11, предназначенного для получения промежуточных сумм. Выходы суммы и переноса сумматора 11 соединены с числовыми входами и входом переноса четырехразрядных сумматоров 5,7-10. Выходы суммы первого сумматора 5 соединены с числовыми входами второго сумматора 6, вход переноса которого постоянно подключен к потенциалу, соответствующему логической 1 для выполнения округления кода выходного числа, образующегося на выходах преобразователя. Выходы суммы и переноса второго сумматора б соединены с числовыми входами третьего сумматора 7, выходы трех младших разрядов сумма которого подключены к выходам младших разрядов преобразованного числа. Выход четвертого разряда суммы третьего су 1матора 7 соединен с числовым входом первого разряда четвертого сумматора 8, выходы суммы которого подключены к числовым входам пятого с умматора 9. Выход первого разряда суммы сумматора 9 соединен с выходом четвертого разряда преобразователя, а выходы остальных разрядов сумм - с числовыми входами шестого сумматора

0 10. Выходы шестого сумматора 10 и двухразрядного сумматора 12 подключены к выходам старших разрядов преобразователя.

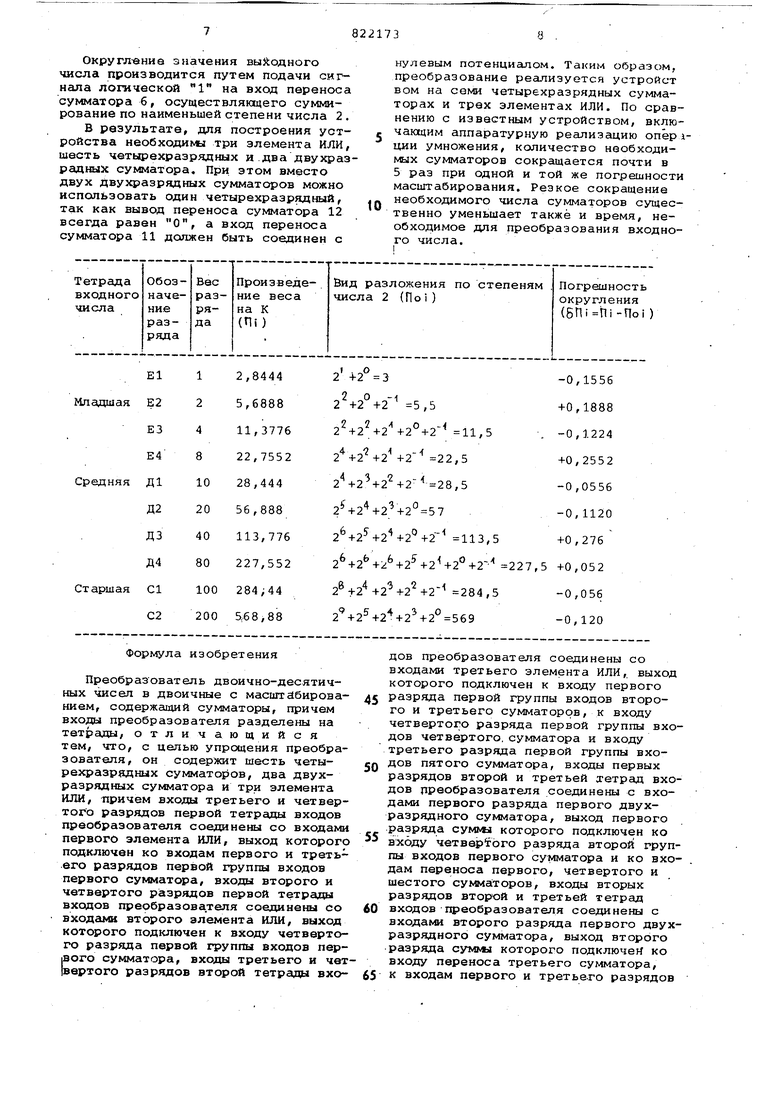

Преобразователь осуществляет па5раллельное преобразование двоичнодесятичного кода числа градусов (фазовый сдвиг от О® до 360°), поступающего на входы, в двоичный код числа долей периода выходного напряжения. Если максимальное число долей пери0ода равно 1024, а максимальное число градусов на выходе 360°, то преобразование выполняется с масштабированием, причем коэффициент масштабирования равен

5

ir 2. принципу работы предлагаемое устройство является устройством комбинационного типа, поэтому при пода0че на его вход двоично-десятичного числа на выходе устройства вырабатывается двоичный код этого числа с учетом коэффициента масштабирования. .Построение устройства и его функцио5нирование целиком определяется разложениями по степеням числа 2 произведений веса разрядов каждой тетрады на коэффициент масштабирования К 2,8444. Вид разложений для каждого из разрядов входного числа приведен

0 в таблице..

Как следует из таблицы, сумма погрешностей одного знака в наихудшем случае приблизительно равна /-2 веса

младшего разряда кода выходного числа. Действительноj

2: (5П, ) 0,2552-0,,5312 5:(бПч)„,ах 0,1556+0,1224 + +0,1120+0,0556+0,056+0,,6216.

Устройство суммирует значения

тех разрядов входного числа, в разцожении произведения веса которых на масштабный коэффициент есть одинаковые степени числа 2. Суммирование производится в порядке возрастания

степени числа 2 и с учетом всех возникающих при этом переносов. Введение элементов ИЛИ 2-4, формирующих cyMNSJ не образующие переноса, БЗ Е4 (первый элемент ИЛИ), Е2+Е4 (второй элемент ИЛИ) и ДЗ+Д4 (третий элемент ИЛИ) упрсицаетустройство. К этой же цели приводит формирование вспомогательных сумм С1+Д1 и С2+Д2 . (с учетом переноса) на двухразрядном

(сумматоре 11.

Округление значения вы&одного числа производится путем подачи сигнала логической 1 на вход переноса сумматора б, осуществлягацего суммирование по наименьшей степени числа 2 .

В результате, для построения устройства необходил« три элемента ИЛИ, шесть четырехразрядных и два двухразрадных сумматора. При этом вместо двух Двухразрядных сумматоров можно использовать один четырехразрядный, так как вывод переноса сумматора 12 всегда равен О, а вход переноса сумматора 11 должен быть соединен с

нулевым потенциалом. Таким образом, преобразование реашизуется устройст вом на семи четырехразрядных сумматорах и трех элементах ИЛИ. По сравнению с известным устройством, включающим аппаратурную реализацию оперции умножения, количество необходимых сумматоров сокращается почти в 5 раз при одной и той же погрешности масштабирования. Резкое сокращение необходимого числа сумматоров существенно уменьшает также и время, необходимое для преобразования входного числа, I .,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1979 |

|

SU911505A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1277402A1 |

Формула изобретения

Преобразователь двоичио-десятичных чисел в двоичные с масштабированием, содержаний сумматоры, причем входы преобразователя разделены на тетрады, отличающийся тем, что, с целью упрощения преобразователя, он содержит шесть четырехразрядных сумматоров, два двухразрядных сумматора и три элемента ИЛИ, -причем входы третьего и четвертого разрядов первой тетрады входов преобразователя соединены со входами первого элемента ИЛИ, выход которого подключен ко входам первого и треть.его разрядов первой группы входов первого сумматора, входы второго и четвертого разрядов первой тетрады входов прербразова.теля соединены со входами второго элемента ИЛИ, выход которого подключен к входу четвертого разряда первой группы входов пер|Вого сумматора, входы третьего и чвт вертого разрядов второй тетрады входов преобразователя соединены со входами третьего элемента ИЛИ, выход которого подключен к входу первого

разряда первой группы входов второго и третьего сумматоров, к входу четвертого разряда первой группы входов четвертого, сумматора и входу третьего разряда первой группы входов пятого сумматора, входы первых разрядов второй и третьей тетрад входов преобразователя соединены с входами первого разр5ша первого двухразрядного сумматора, выход первого разряда суммы которого подключен ко

входу четвертого разряда второй группы входов первого сумматора и ко входам переноса первого, четвертого и шестого сумма:торов, входы вторых разр5щов второй и третьей тетрад

входов преобразователя соединены с входами второго разряда первого двухразрядного сумматора, выход второго разряда суммы которого подключен ко входу переноса третьего сумматора,

к входам первого и третьего разрядов

первой группы входов четвертого сумматора и первого разряда первой группы входов шестого сумматора, а выход переноса первого двухразрядного сумматора подключен к входу второго разряда первой группы входов третьего сумматора, к входам третьего и четвертого разрядов первой группы входов четвертого сумматора, ко входу первого разряда пятого сумматора и ко входу переноса пятого сумматора, выходы переноса первого и второ.го сумматоров соединены с входами четвертого разряда третьего сумматора, выходы трех младших разрядов сумкы которого подключены к .выходам трех младших разрядов преобразователя, выход переноса третьего сумматора со€)динен с входом второго разряда второй группы входов четвертого сумматора, выходы переноса четвертого и пятого сумматоров соединеныс входами четвертого разряда шестого сумматора, выход переноса которого соединен с входом переноса второго двухразрядного сумматора, выходы сумкса которого и выходы сумлы шестого сумматора подключены к выходам соответствукхцих разр5здов преобразователя, вхсщ первого разряда первой тетрады входов преобразователя соединен с входами второго разряда первой группы и третьего разряда второй группы входов первого сумматора, вход второго разряда первЬй тетрады входов преобразователя соединен с входами первого и второго разрядов второй группы входов первого сумматора, вход третьего разряда первой тетрады входов преобразователя соединен с входами второго и четвертого разрядов первой группы входов второго сумматора и с входом третьего разряда первой группы входов третьего сумматора, входы четвертого разряда первой и третьего разряда второй тетрад входов преобразователя соединены с входами вторых разрядов первой группы входов пятого и второй группы входов четвертого сумматоров соответственно, вход ч.етвертого разряда второй тетрады входов преобразователя соединен с входом tpeTbero разряда первой группы входов второго сумматора, с входом четвертого разряда первой группы входов пятого сумматора и третьего разряда шестого сумматора, входы двух

0 младших разрядов третьей тетрады -входов преобразователя соединены с соответствующими входами первой группы входов второго двухразрядного сумматора, входы второй группы которого

5 соединены с входом логического нуля, вход переноса первого двухразрядного сум1латора и вход второго разряда первой группы входов шестого сумматора соединены с входом логического нуля/

0 разрядные выходы суммы первого и четвертого сумматоров соединены с входами соответствуюсцих разрядов второй группы второго и пятого сумматоров соответственно, выходы трех старших разрядов суммы второго и пятого сум5маторов соединены с входами трех младших разрядов второй группы входов третьего и шестого сумматоров соответственно, вход переноса второго сумматора соединен с входом логической едиDницы, выход четвертого разряда треть его сумматора соединен с входом первого разряда второй группы входов четвертого сумматора, выход первого разряда пятого сумматора соединен с вы5ходом четвертого разряда преобразователя.

Источники информации, принятые во внимание при экспертизе

1,Авторскоесвидетельство СССР

0 № 436345, кл. G Об ,F 5/02,15.07.72.

/v-

гг|-I / .г- ТГ |Л71/Т/;

r

Авторы

Даты

1981-04-15—Публикация

1979-06-18—Подача