Изобретение относится к вычислительной технике и, в частности, к устройствам управления центральных процессоров.

Известны устройства для передачи управления подпрограммам, в которых применяются регистры-указатели для записи в них базовых адресов различных участков памяти. Эти регистры образуют быструю память, имеющую матрицу выборки регистра по его адресу, а также оборудование управления. Аппаратные затраты при этом весьма значительны.

Известны также устройства, содержащие аппаратуру для выполнения функций индексрегистров. Количество индекс-регистров, реализованных аппаратно, обычно не превыщает 16. Поэтому необходимы специальные программные средства для перезапоминания содержимого индекс-регистров в память и из памяти при прерываниях и переходах к подпрограммам.

Это уменьшает эффективность использования процессоров.

В процессорах, где применяются в качестве индекс-регистров произвольные ячейки ОЗУ, проблема сохранения содержимого индекс-регистров решается за счет аппаратного выделения нового участка ОЗУ под индексрегистры при переходе к подпрограммам. Это свойство обеспечивает повышение эффективности работы процессоров за счет ликвидации издержек на вспомогательные программы перезапоминания. Цель изобретения - сокращение оборудования. При этом незначительно снижается быстродействие, так как для вхождения в подпрограмму необходимы два обращения к индикаторному регистру. Исполнение подпрограммы требует значительно большего (на несколько порядков) числа обращений к ЗУ. Таким бразом, в процентном отношении потери времени из-за обращения к индикаторному регистру весьма незначительны.

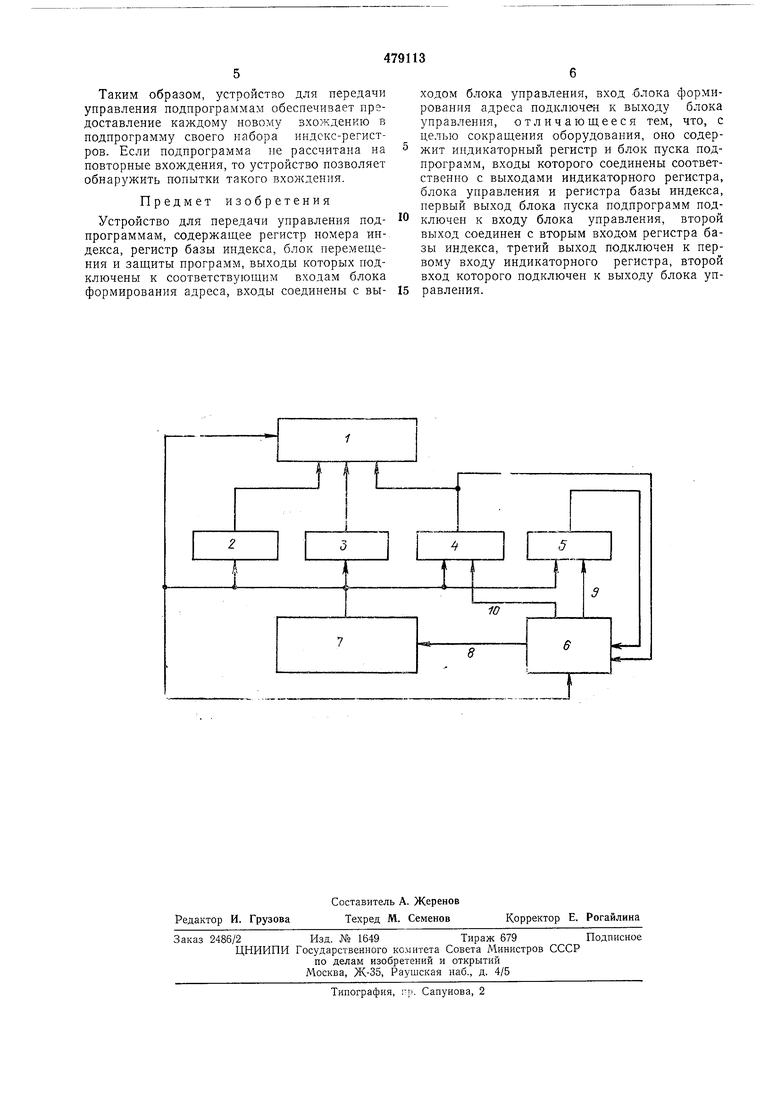

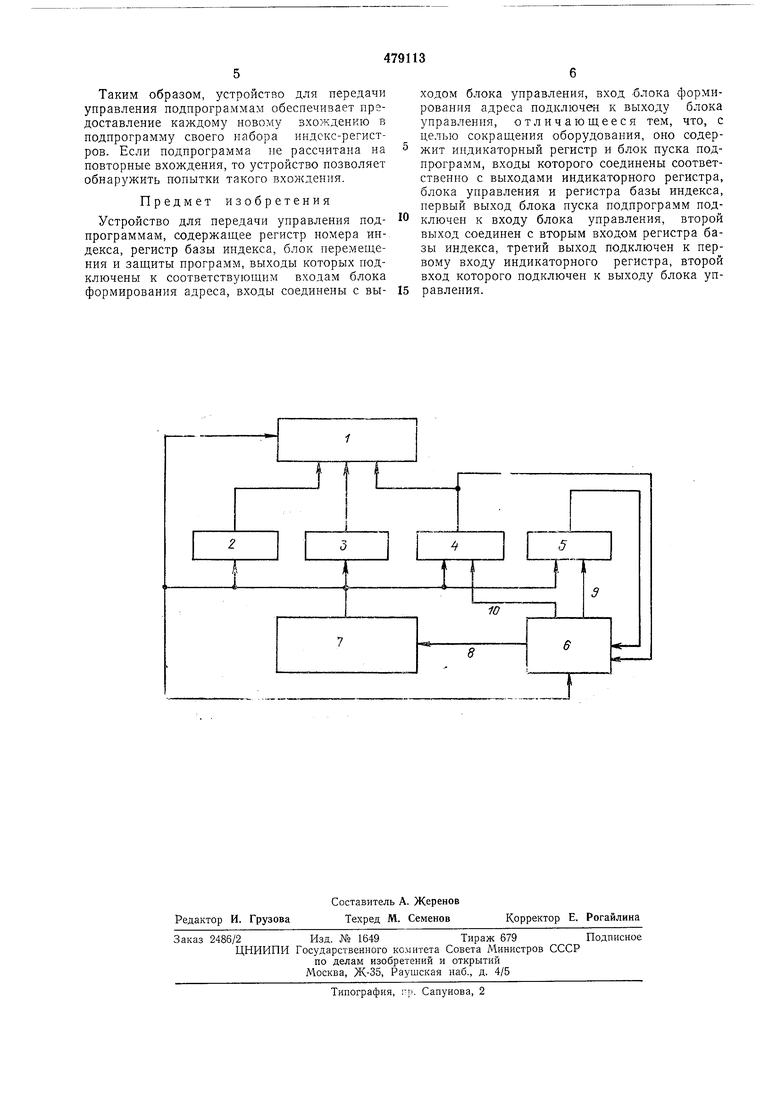

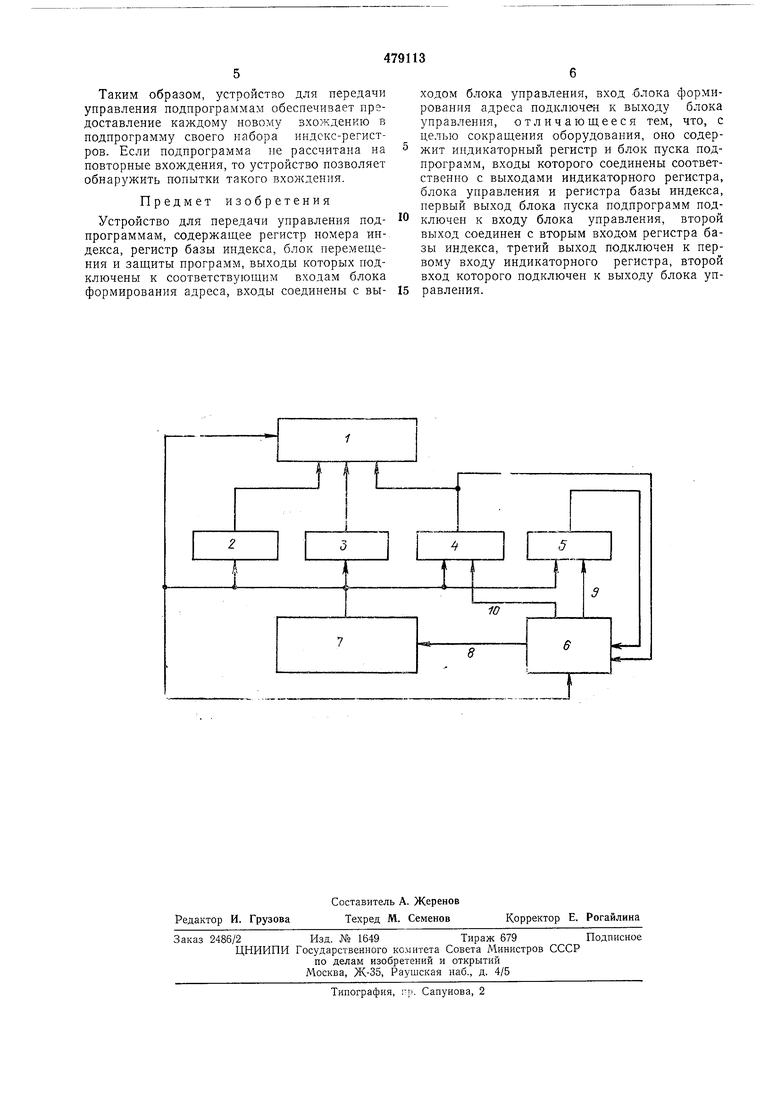

В предлагаемое устройство введены индикаторный регистр и блок пуска подпрограмм, входы которого соединены соответственно с выходами индикаторного регистра, блока управления и регистра базы индекса. Первый

выход блока пуска подпрограмм подключен к входу блока управления, второй выход - к второму входу регистра базы индекса, третий выход - к первому входу индикаторного регистра, второй вход которого соединен с выходом блока управления.

На чертеже представлена схема устройства.

Она содержит блок 1 формирования адреса;

блок 2 перемещения и защиты программ;

регистр 3 номера индекса; регистр 4 базы индекса; индикаторный регистр 5; блок 6 пуска подпрограмм; блок 7 управления; шину 8 переполнения; шину 9 занятия уровня; шину 10 номера уровня. При построении многопрограммных вычислительных машин, особенно многолроцессорных вычислительных комплексов, возникает проблема передачи управления общим подпрограммам, т. е. таким подпрограммам, которые используются совместно с несколькими задачами многопрограммной системы, выполняюш,имися, возможно, на нескольких процессорах. При этом возникают ситуации, когда общая подпрограмма, будучи незаконченной, прерывается, а затем происходит новое обраш,ение к ней из другой задачи. Возможна также ситуация, когда два процессора почти одновременно могут обратиться к обшей подпрограмме и далее выполнять ее со сдвигом на одну или несколько команд. В первом случае следует выполнить обшую подпрограмму, выйти из нее и в будущем довыполнить ее с прерванного места и выйти из подпрограммы в точку обращения. Во втором случае необходимы независимое исполнение общей подпрограммы двумя или более процессорами и по окончании подпрограммы выход из нее каждого процессора в точку обращения. Для того- чтобы подпрограмма обладала такими свойствами, нужно выполнить несколько условий. В частности, подпрограмма должна быть закодирована так, чтобы она не содержала в своем теле переменных команд и рабочих ячеек. В противном случае повторное вхождение в обшую подпрограмму до окончания ее работы по первому вхождению должно быть запрещено. Вторым необходимым условием рентабельности общей подпрограммы является предоставление каждому вхождению в общую подпрограмму своей группы индекс-регистров и рабочих ячеек. Обеспечение требуемой формы кодирования возлагается на программиста. Второе же условие может быть реализовано аппаратно. Особенно это удобно, если индекс-регистры .физически размещаются в оперативной памяти и адрес их начала тем или иным образом связан с адресом начала общей подпрограммы. Предлагаемое устройство решает эту заКаждая подпрограмма, расположенная в .оперативном запоминающем устройстве, начинается со служебной группы ячеек, назы.ваемых программным уровнем. Эти ячейки используются в качестве индекс-регистров. Одна из этих ячеек отведена для хранения содержимого индикаторного регистра 5. Если подпрограмма рассчитана на несколько вхождений, то в ее начале отводится несколько групп служебных ячеек - программных уровней. .Разряды регистра 5 пронумерованы слева направо и первый разряд регистра соответствует первому уровню, второй разряд - второ / уровню,и т. д. Если значение разряда регистра 5 равно единице, это означает, что соответствующий уровень занят вхождением в подпрограмму, т. е. подпрограмма выполняется или, по крайней мере, начала выполняться каким-либо процессором с использованием данного программного уровня. Если значение разряда регистра 5 равно нулю, это значит, что соответствующий уровень свободен. При выполнении процедуры входа в подпрограмму, блок 6 пуска подпрограмм просматривает слева направо регистр 5 данной подпрограммы для того, чтобы найти ближайший нулевой разряд. Если нулевой разряд найден, то блок 6 пуска подпрограмм через шину 9 занятия уровня устанавливает в этом разряде единицу, а на щине 10 номера уровня - номер этого разряда в регистре 5. Номер уровня с щины 10 поступает на регистр 4 базы индекса и в дальнейшем используется при определении физических адресов ячеек памяти, используемых в качестве индекс-регистров. Если при просмотре блоком 6 пуска подпрограмм регистра 5 нулевого разряда не обнаружено, то блок 6 через шину 8 переполнения сообщает об этом блоку 7 управления, который прекращает выполнение передачи управления подпрограмме. Таким образом, если подпрограмма рассчитана на одно вхождение, то индикаторный регистр 5 должен вначале содержать только один нулевой разряд. Все остальные разряды должны быть единичными. В случае выполнения процедуры выхода из подпрограммы блок 6 пуска подпрограмм, по номеру уровня, поступающему на его вход из регистра 4 базы индекса, устанавливает в нуль по шине 9 занятия уровня разряд индикаторного регистра, соответствующий номеру освобождаемого уровня. При исполнении подпрограммы на любом из уровней вхождения физические адреса индексрегистров образуются следующим образом. Блок 2 перемещения и защиты программ предназначен для преобразования относительных адресов программ и групп программ в физические адреса оперативной памяти. При этом преобразовании блок 2 перемещения и защиты программ проверяет не выходит ли полученный адрес за диапазон адресов, допустимых для данной группы протрамм, осуществляя тем самым функцию защиты программ. При образовании физического адреса индекс-регистра, блок 2 передает в блок 1 формирования адреса физический адрес начала подпрограммы в оперативной памяти. Этот адрес должен содержать в младших разрядах нули. Регистр 4 базы индекса передает в блок 1 формирования адреса номер уровня вхождения в подпрограмму, образуя следующую, более младшую группу разрядов физического адреса индекс-регистра. Младшие разряды физического адреса индекс-регистра берутся из регистра 3 номера индекса, откуда они поступают в блок 1 формирования адреса,

Таким образом, устройство для передачи управления подпрограммам обеспечивает предоставление каждому новому вхождению в подпрограмму своего набора индекс-регистров. Если подпрограмма не рассчитана на повторные вхождения, то устройство нозволяет обнаружить попытки такого вхожден 1я.

Предмет изобретения

Устройство для передачи управления подпрограммам, содержащее регистр номера индекса, регистр базы индекса, блок перемещения и защиты программ, выходы которых подключены к соответствующим входам блока формирования адреса, входы соединены с выходом блока управления, вход -блока формирования адреса подключен к выходу блока управления, отличающееся тем, что, с целью сокращения оборудования, оно содержит индикаторный регистр и блок пуска подпрограмм, входы которого соединены соответственно с выходами индикаторного регистра, блока управления и регистра базы индекса, первый выход блока пуска подпрограмм подключен к входу блока управления, второй выход соединен с вторым входом регистра базы индекса, третий выход подключен к первому входу индикаторного регистра, второй вход которого подключен к выходу блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| СПОСОБ ПЕРЕКЛЮЧЕНИЯ КОНТЕКСТА ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ПРИ ПРЕРЫВАНИИ ПРОГРАММЫ ИЛИ ПЕРЕХОДЕ К ПОДПРОГРАММЕ | 2006 |

|

RU2340933C2 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Многопроцессорная вычислительная система с изменяемой конфигурацией | 1974 |

|

SU525953A1 |

..„ и

Авторы

Даты

1975-07-30—Публикация

1972-04-06—Подача