1

Изобретение относится к аналогоцифровым преобразователям и может быть использовано в области связи, .вычислительной и измерительной техники , а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований..

По основному авт.св. 799129 . известе.и. следящий аналого-цифровой преобразователь, содержащий блок сравнения, аналоговый запоминающий блок, цифро-аналоговый преобразователь, реверсивный счетчик, первый логический блок, вторюй логический блок распределитель импульсов, блок поиска поддиапазона, третий логический блок, генератор тактовых импульсов, первый, второй и третий триггеры, причем первый вход блока сравнения соединен с выходом аналогового Запоминающего блока, вход которого соединен с источником входного сигнала;-второй вход блока сравнения соединен с выходом цифро-аналогового преобразователя, цифровые входы которого соединены с выходами разрядов реверсивного счетчика, выход блока сравнения соединен с первым входом первого логического блока, второй

вход которого соединен с единичным выходом триггера переполнения ревер сивного счетчика, выхо.цы разрядов реверсивного счетчика соединены с первой группой входов второго логического блока, вторая группа входов которой соединена с выходами соответствуюищх разрядов распределителя импульсов, первая группа вы10ходов второго логического блока соединена со счетными входами соответствующих разрядов реверсивного счетчика, первый выход первого логического блока соединен с третьим

15 входом блока поиска по.цциапазона и со ВТО1МЛМ входом третьего логического блока, второй и третий выходя первого логического блока соединены со входами установки режима ревер20сивного счетчика, первый вход блока поиска поддиапазона соединен с первым входом третьего логического блока и с единичным выходом последнего (младшего) разряда распределителя импульсов, второй вход соеди25нен с первым выходом второго логического блока, четвертый вход соединен с третьим входом третьего логического блока и с выходом генератора тактовых импульсов, пятый вход

30

соединен с единичным выходом первого триггера, первый выход соединен со вторым входом второго логического блока, второй выход соединен с единичным входом второго триггера и с первым входом второго логического блока, третий выход соединен с четвертым входом второго логического блока, четвертый выход соединен с единичным входом третьего триггера, пятый ыход соединен с нулевым входом.первого триггера, четвертый вход третьего логического блока соединен с единичным выходом второго триггера, первый и второй выходы третьего логического блока соединены соответственно с третьим и пятым входами второго логического блока, а третий выход третьего логического блока соединен с нулевым входом второго триггера и с единичным -входом третьего триггера, нулевой вход которого соединен с шиной Сброс флага , а единичный выход соединен с шиной Готовность, второй и третий выходы второго логического блока соединены соответственно со входами сдвига вправо и влевораспределителя импульсов,единичный вход первого триггера соединен с управляющим входом аналогового эапсминающего блока ис шиной Запуск

Сущность работы известного устройства заключается в том, что в начале каждого преобразования проверяется, не находится ли сигнал в верхнем или нижнем кванте, примыкающем к образцовому уровню, зафиксированному на преобразователе. Для этог.о осуществляется переход на соседний образцовый уровень (верхний или нижний в зависимости от сигнала блока сравнения). Если ответ блока сравнения после этого меняется на противоположный, то это означает, что сигнал найден, и преобразование заканчивается, тем самым значительно сокращается время преобразования Если же ответ блока сравнения не меняется, то следовательно, выходной сигнал не находится данном кванте, и продолжается поиск, поддиапазона нахождения входного сигнала Для этого до смены ответа блока сравнения происходит удвоение шага квантования, но при условии, что разряды числового Эквивалента,более младггме чем измен яемый , находятся в состоянии О . После смены ответа блока сравнения преобразователь переходит к поразрядному поиску сигнала внутри найденного поддиапазона. Все действия, связанные g поиском поддиапазона и.с поразрядным преобразованием выполняются блоком поиска поддиапазона и вторым логическим блоком.

Недостатком преобразователя является низкая достоверность выдаваемых кодов и большая погрешность преобразования.

Если новое значение сигнала отличается от рбразцого уровня, зафиксированного на преобразователе в J Везультате предыдущего цикла преоб-; разования, менее чем на квант, то в результате чередования ответов блока сравнения мы мэжем утверждать, что достоверность ( т.е.вероятность

Q правильного ответа) вновь полученного значения числового эквивалента равна единице.

Если же для определения нового значения сигнала требуется поиск поддиапазона с последующим поразрядным

5 преобразованием внутри найденного

поддиапазона, то достоверность половины получаемых кодов равна единице, достоверность же другой половины получаемых кодов может быть значительно ниже единицы. Пусть, например, в процессе поразрядного преобразования проверочная единица установлена в предпоследний разряд, т.е. хх...х10(где или 1). В резульg тате проверки мы можем получить либо код Х...ХИ, либо код Х...Х01. Очевидно, если значение сигнала находится между уровнями Х...Х10 и Х...ХП, либо между уровнями Х...Х10 и Х.Х01, то ответы блока сравнения чередуют, и мы получим коды, достоверность которых близка к единице, т.е. поразрядный метод обеспечивает проверку достоверности части кодбв. Если же значение сигнала вьоше уровня х,..ХП или ниже уровня Х....Х01, то ответы блока сравнения повторяются, и мы не можем быть уверены в достоверности полученного кода, т.е. преобразователь указывать не

0. некоторый квант, в то время, как сигнала в этом кванте нет, следовательно, повышается погрешность преобразования .

Цель изобретения - повышение достоверности выдаваемого кода и уменьшение погрешности преобразования.

Поставленная цель достигается тем, что в следящий аналого-цифровой преобразователь, содержащий блок сравQ нения, аналоговый запоминающий блок, цифро-аналоговый преобразователь, реверсивный счетчик, распределитель импульсов, блок поиска поддиапазона, генератор тактовых импульсов, три

логических блока , три триггера, причем первый вход которого соединен с выходом аналогового запоминающего блока, вход которого соединен с источником входного сигнала, второй вход блока сравнения соединен с выходом цифро-аналогового преобразотеля, цифровые входы которого соединены с выходами разрядов реверсивного счетчика, выход блока сравнения соединен с первым входом первого логического блока, второй вход которого

соединен с единичным выходом триггера переполнения реверсивного счетчика, выходы разрядов реверсивного счетчика соединены с первой группой входов второго логического блока, Вторая группа входов которого соедииена с выходами соответствующих разрядов распределителя импульсов, д первая группа выходов соединена со счетными входами соответствующих разрядов реверсивного счетчика, при этом первый выход первогологическог блока соединен с первыми входами блока поиска и поддиапазона третьего логического блока, второй и третий выходы первого логического блока соединены со входами установки режима реверсивного счетчика, второй вход блока поиска поддиапазона соединен со вторым входом третьего логического блока и с единичным выходом последнего (глладщего) разряда распре делителя импульсов, третий вход соединен с первым выходом второго логического блока, четвертый вход соединен с третьим входом третьего логического блока и с выходом генератора тактовых импульсов, пятый вхо соединен с единичным выходом первого триггера, при этом первый выход соединен со .вторым входом второго логического блока, второй выход соединен с единичным входом триггера и с первым входом второго логическог блока, третий выход соединен с четвертым входом второй логической схемы, четвертый выход соединен с единичным входом третьего триггера, пятый выход соединен с нулевым входом первого триггера, четвертый вход третьего логического блока соедаснен с единичным выходом второго триггера, первый и второй выходы третьего логического блока соединены соответственно с третьим и пятым входами второго логического блока, а третий выход третьего логического блока соединен с нулевым входом второго триггера и с единичным входом третьего триггера, нулевой вход которого соединен с шиной Сброс флага , а единичный выход соединен с шиной Готовность, второй и третий выходы второго логического блока соединены сортветственно со входами сдвига вправо и влево распределителя импульсов, единичный вход первогчэ триггера соединен с управляющим входом аналогового запоминающего устройства и с проводом Запуск, выход предпоследнего разряда реверси ного счетчика со единен с пятым входом третьего логического блока, а четвертый выход третьего логического блока соединен с шестым входом блока поиска поддиапазона со вторым единичным входом первого триггера и вторым нулевым входом Btopprcf триггера.

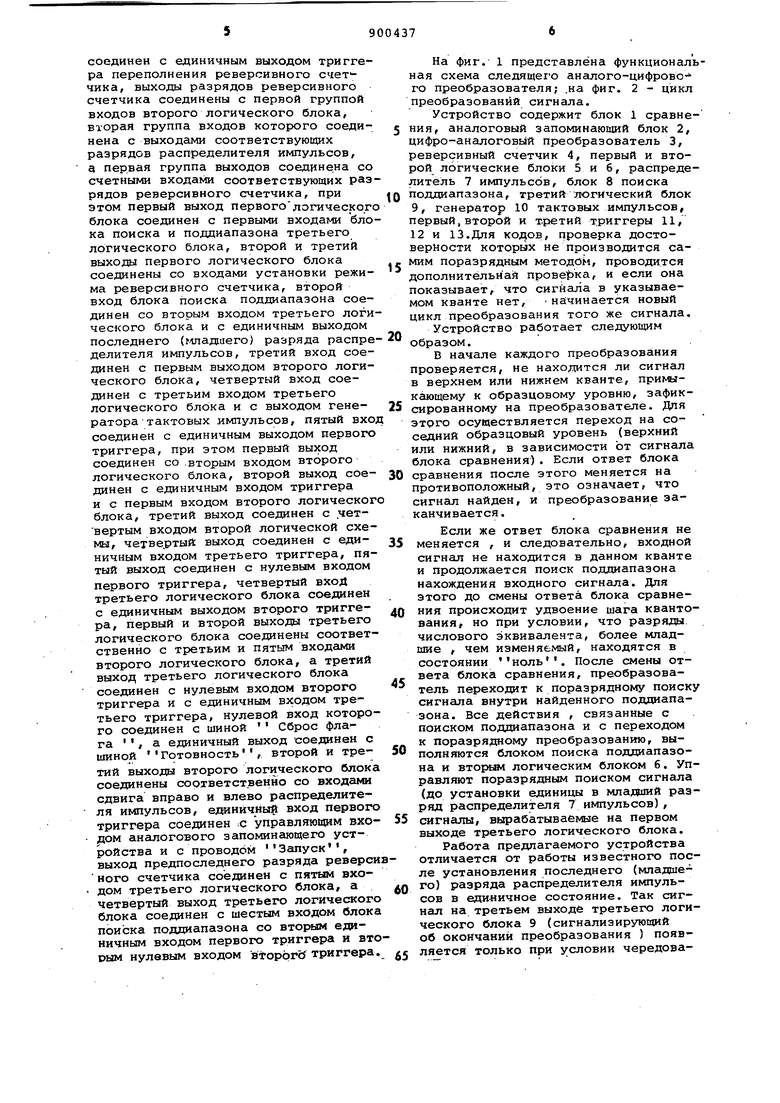

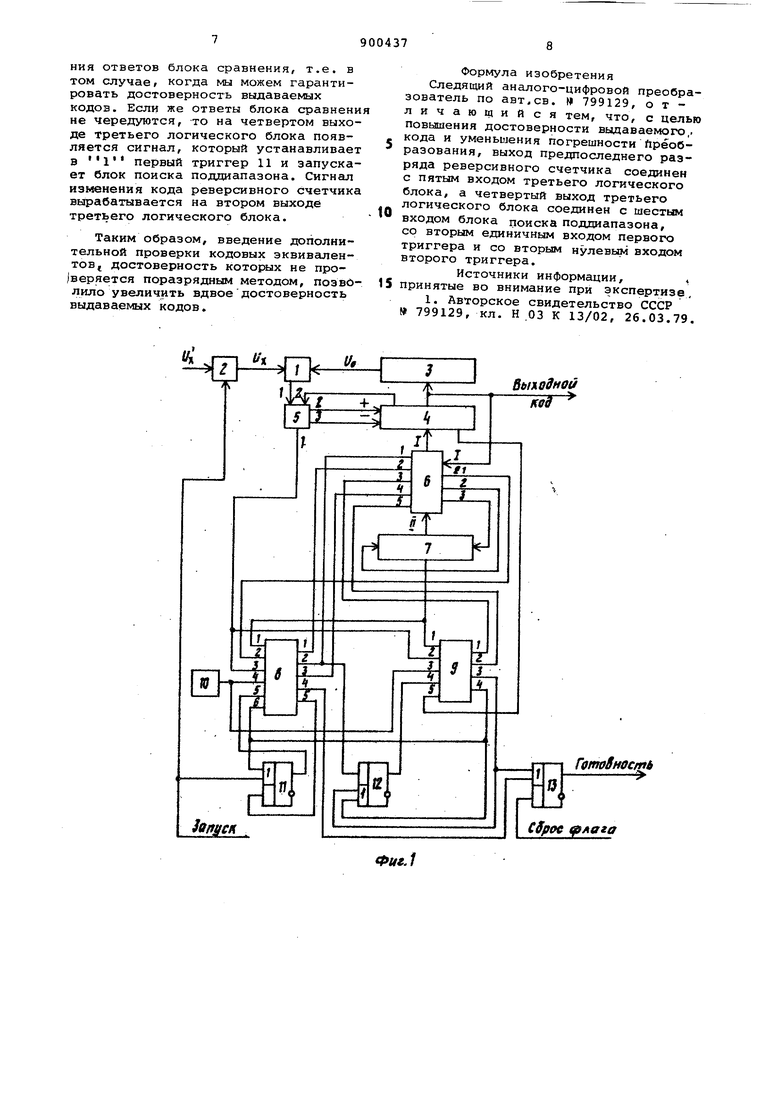

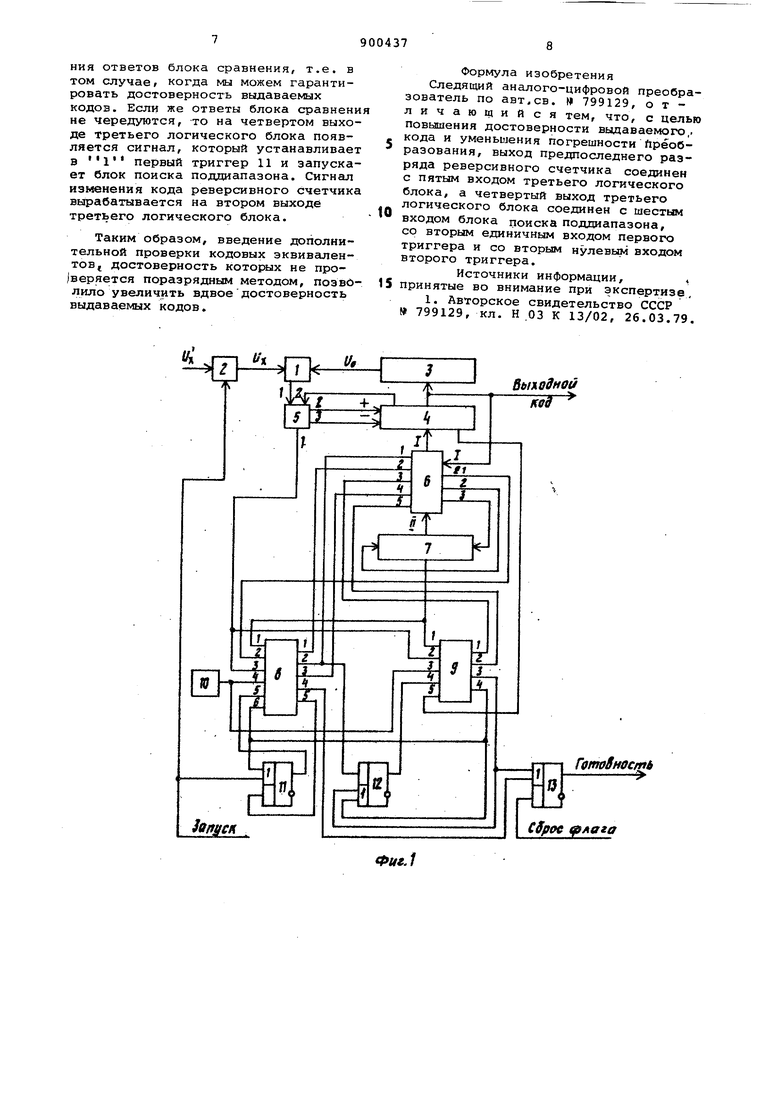

На фиг. 1 представлена функционалная схема следящего аналого-цифрового преобразователя; .на фиг. 2 - цикл преобразований сигнаша.

Устройство содержит блок 1 сравнения, аналоговый запоминающий блок 2, цифро-аналоговый преобразователь 3, реверсивный счетчик 4, первый и второй логические блоки 5 и б, распределитель 7 импульсов, блок 8 поиска поддиапазона, третий логический блок 9, генератор 10 тактовых импульсов, первый,второй и третий триггеры 11, 12 и 13.Для , проверка достоверности которых не производится самим поразрядным методой, проводится дополнительна пройе эка, и если она показывает, что сигнала в указываемом кванте нет, начинается новый цикл преобразования того же сигнала.

Устройство работает следующим образом.

В начале каждого преобразова.ния проверяется, не находится ли сигнал в верхнем или нижнем кванте, примыкающему к образцовому уровню, зафиксированному на преобразователе. Для этого осуществляется переход на соседний образцовый уровень (верхний или нижний, в зависимости от сигнала блока сравнения). Если ответ блока сравнения после этого меняется на противоположный, это означает, что сигнал найден, и преобразование заканчивается.

Если же ответ блока сравнения не меняется , и следовательно, входной сигнал не находится в данном кванте и продолжается поиск поддиапазона нахождения входного сигнала. Для этого до смены ответа блока сравнения происходит удвоение шага квантования, но при условии, что разряды, числового эквивалента, более младшие , чем изменяемый, находятся в состоянии ноль. После смены ответа блока сравнения, преобразователь переходит к поразрядному поиску сигнала внутри найденного поддаапазона. Все действия , связанные с поиском поддиапазона и с переходом к поразрядному преобразованию, выполняются блоком поиска поддиапазона и вторым логическим блоком б. Управляют поразрядным поиском сигнала (до установки единицы в младашй разряд распределителя 7 импульсов), сигналы, вырабатываемые на первом выходе третьего логического блока.

Работа предлагаемого устройства отличается от работы известного после установления последнего (младшего) разряда распределителя импульсов в единичное состояние. Так сигнал на третьем выходе третьего логического блока 9 (сигнализирующий об окончаний преобразования ) появляется только при условии чередования ответов блока сравнения, т.е. в том случае, когда мы можем гарантировать достоверность выдаваемых кодов. Если же ответы блока сравнени не чередуются, -то на четвертом выходе третьего логического блока появляется сигнал, который устанавливает в Ч первый триггер 11 и запускает блок поиска поддиапазона. Сигнал изменения кода реверсивного счетчика вырабатывается на втором выходе третьего логического блока. Таким образом, введение дополнительной проверки кодовых эквивалентoв достоверность которых не про)веряется поразрядным методом, позвс лило увеличить вдвое достоверность выдаваемых кодов.

ВылоЗмой

Фиг,1 Формула изобретения Следящий аналого-цифровой преобразователь по авт.св. 799129, отличающийся тем, что, с целью Повышения достоверности выдаваемогх),. кода и уменьиления погрешности йрё образования, выход предпоследнего разряда реверсивного счетчика соединен с пятым входом третьего логического блока, а четвертый выход третьего логического блока соединен с шестым входом блока поиска поддиапазона, со вторым единичным входом первого триггера и со вторым нулевьа-i входом второго триггера. Источники информации, « принятые во внимание при экспертизе, 1. Авторское свидетельство СССР 799129, кл. Н 03 К 13/02, 26.03.79.

s

Д... xffn L-J... xg j

J--ii

ч

...

у... gq ... xflgf {

Нойый цикл

преобразований I

Xi

/

. .Д.ТГхш f

«... ХЮО I

... XfffJ 1

Д(Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1179538A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1003331A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU924852A1 |

| Преобразователь напряжения в код | 1980 |

|

SU917335A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

Авторы

Даты

1982-01-23—Публикация

1980-05-23—Подача