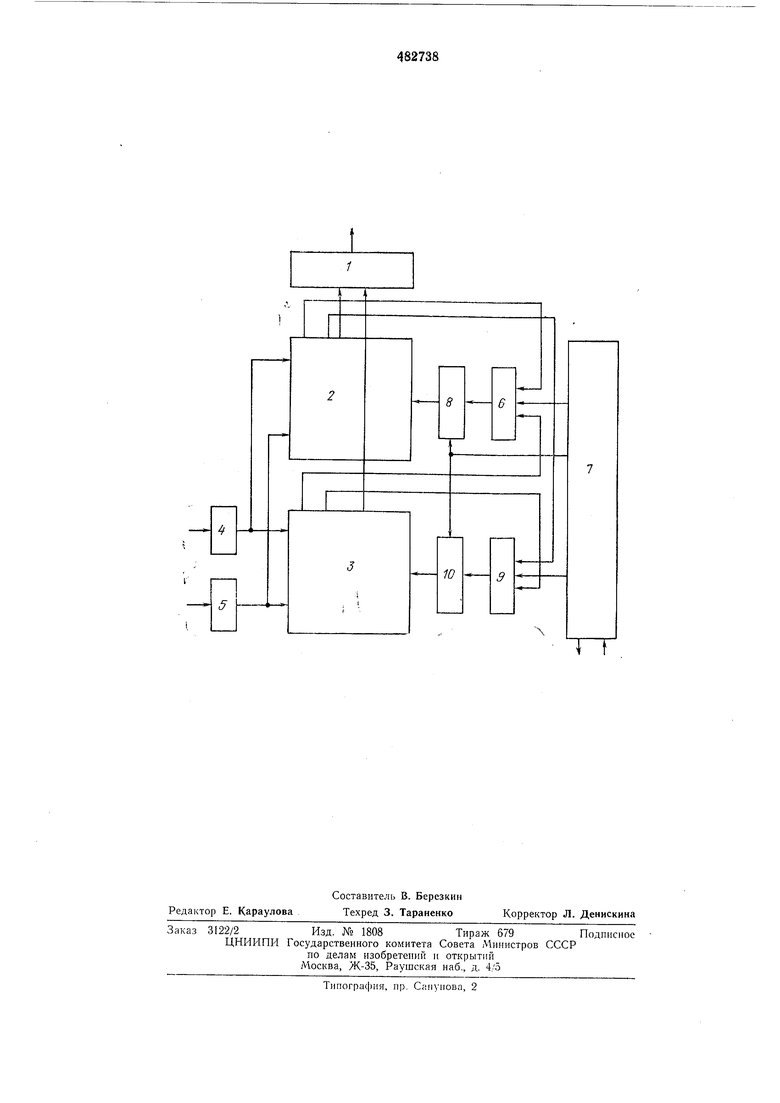

ка 3 - с вторым входом элемента «ИЛИ 6, третий вход которого соединен с нервым выходом блока местного унравления 7, а выход - с первым входом элемента «И 8. Третий выход блока 2 связан с первым входом элемента «ИЛИ 9, второй дополнительный выход блока 3 - с вторым входом элемента «ИЛИ 9, третий вход которого соединен с вторым выходом блока местного управления 7, а выход - с первым входом элемента «И 10. Второй вход элемента «И 10 подключен к третьему выходу блока местного управления 7 и к второму входу элемента «И 8, выход которого связан с третьим входом блока 2. Выход элемента «И 10 присоединен к третьему входу блока 3. Устройство работает следующим образом. При выполнении операций типа сложение или вычитание числа или их части заносятся в координатно-адресные регистры 4 и 5. При этом в зависимости от длины разрядной сетки чисел возможны следующие случаи.

1. Разрядная сетка первого и второго слагаемых меньше или равна разрядной сетке коордннатно-адресных регистров 4 и 5.

В этом случае числа заносятся в координатно-адресные регистры 4 и 5. С третьего выхода блока местного управления 7 на управляющий вход элемента «И 10 выдается разрешающий сигнал, а с второго выхода блока 7 вырабатывается сигнал спроса, который проходит последовательно соединенные элемент «ИЛИ 9 и элемент «И 10 и поступает на третий вход постоянного запоминающего блока 3. Результат сложения в виде суммы снимается с первого выхода постоянного запоминающего блока 3 и записывается в регистр результатов 1.

2. Разрядная сетка первого и второго слагаемых больще разрядной сетки координатиоадресных регистров 4 и 5.

В этом случае младщая часть первого и второго слагаемых заносится в коордгиштно-адресные регистры 4 и 5. С третьего выхода блока местного управления 7 на управляющий вход элементов «И 8 и 10 выдается разрещающий сигнал, а с второго выхода блока

7вырабатывается сигнал опроса, который, аналогично случаю 1, проходит последовательно соединенные элемент «ИЛИ 9 и элемент «И 10 и поступает иа третий вход постоянного запоминающего блока 3.

Результат сложения младшей части слагаемых в виде суммы снимается с первого выхода постоянного запоминающего блока 3, заносится в регистр результатов 1 и снимается с выхода последнего. При этом, в зависимости от.значения результата сложения, на первом или втором дополнительных выходах постоянного запоминающего блока 3 вырабатывается сигнал. Появление сигнала на первом дополнительном выходе означает наличие переноса, появление сигнала на втором дополнительном выходе - отсутствие переноса.

8следующем такте очередная часть первого

и второго слагаемых заносится в координатно-адресные регистры 4 и 5, а в зависимости от наличия сигналов на первом или втором дополнительном выходах иостояиного запоми5 иающего блока 3 через элемент «ИЛИ 6 или 9 происходит опрос блока 2 или 3.

Аналогичным образом в зависимости от наличия сигнала на втором или третьем выходе блока 2, в случае обращения к последнему,

будет выработан сигнал опроса для элемента «ИЛИ 6 или 9, и в соответствии с выбранной схемой произойдет последующее обращение к блоку 2 или 3. Таким образом, процесс становится циклическим и иродолжается до тех

IS пор, пока с третьего выхода блока местного управления 7 не будет выработан запрещающий сигнал.

Промежуточные результаты последовательно снимаются с выхода регистра результа0 тов 1.

Выполнение операций типа вычитание ири подготовлепном (иивертированном) одном из слагаемых сводится к выполнению операции сложения. В этом случае процесс начинается

5 с подачи разрешающего сигнала с третьего выхода блока местного управления 7 на вход элементов «И 8 и 10 н выработки сигнала опроса, поступающего на третий вход элемента «ИЛИ 6.

0гг

Предмет изобретения

Арифметическое устройство, содержащее регистр результата, вход которого соединен с выходом постоянного запоминающего блока,

5 первый вход которого соединен с выходом первого координатно-адресного регистра, а второй вход - с выходом второго координатно-адресного регистра, и блок местного управления, отличающееся тем, что, с целью

0 увеличения быстродействия, оно содержит дополнительный постояниый запоминающий блок, первый вход которого соединен с выходом первого координатно-адресного регистра, второй вход - с выходом второго координат5 но-адресного регистра, первый выход - с дополнительным входом регистра результата, второй выход - с первым входом первого элемента «ИЛИ, второй вход которого соединен с первым дополнительным выходом иостоян0 ного запоминающего блока, третий вход - с первым выходом блока местного управления, а выход - с нервым входом первого элемента «И, третий выход - с иервым входо.м: второго элемента «ИЛИ, второй вход которого соединен с вторым дополнительным выходом постоянного запоминающего блока, третий вход - с вторым выходом блока местного управления, а выход - с первым входом второго элемента «И, выход которого

0 соединен с третьим входом постоянного запоминающего блока, а второй вход - с третьим выходом блока местного управления и вторым входом первого элемента «И, выход которого соединен с третьим входом дополнительиого постоянного запоминающего блока.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU588561A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Запоминающее устройство | 1977 |

|

SU631990A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Устройство для поворота системы координат | 1987 |

|

SU1444876A1 |

| Устройство для определения среднего арифметического значения | 1989 |

|

SU1658169A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

Авторы

Даты

1975-08-30—Публикация

1974-02-26—Подача