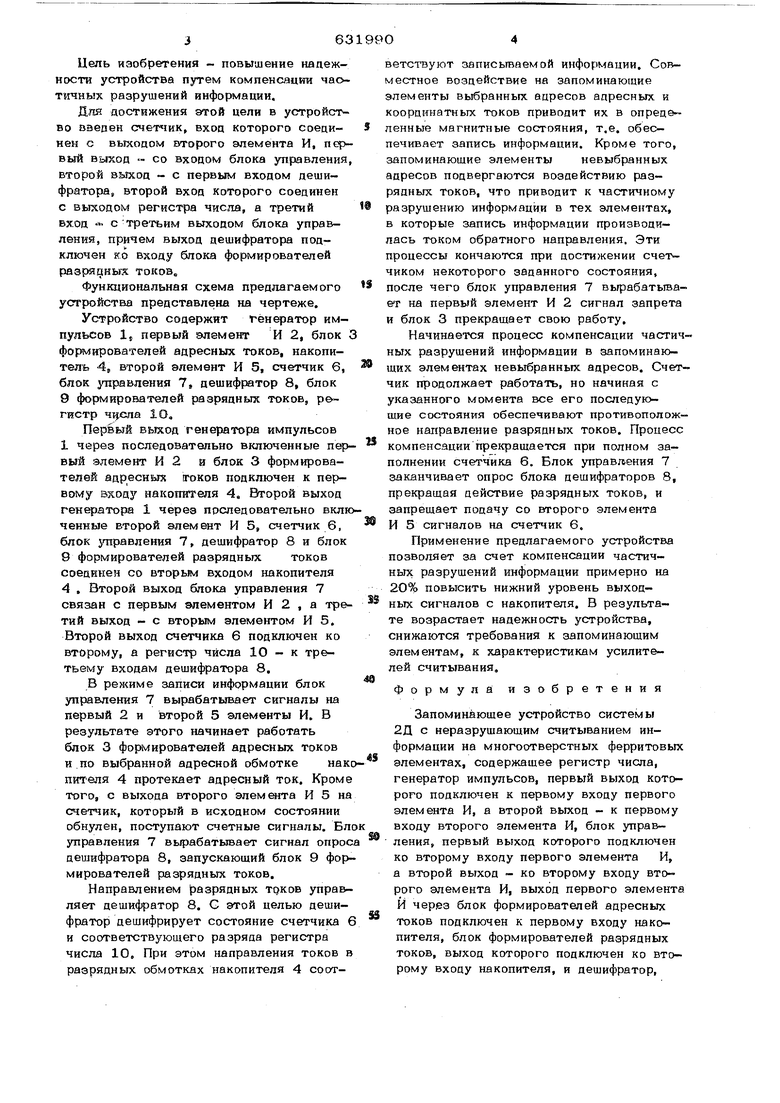

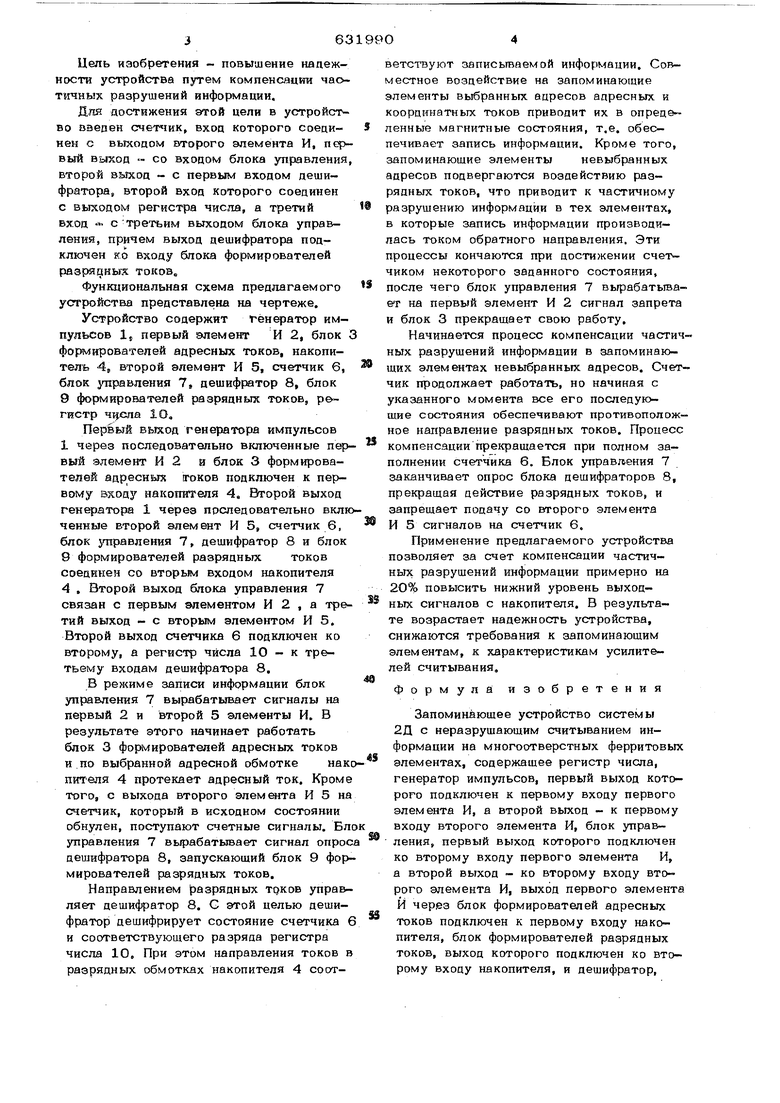

Цель изобретения - повышение надежности устройства путем компенсации чао разрушений информации, Для достижения этой цели в устройство оаевен счетчик, вход которого соецииен с выходом второго элемента И, nq вый выход со входом блока управления второй выход - с первым входом дешифратора, второй вход которого соединен с выходом регистра числа, а третий вход с-третьим выходом блока управления, причем выход дешифратора подключен ко входу блока формирователей разрядных токов, Функциональная схема предлагаемого устройства представлена на чертеже. Устройство содержит тёнератор импульсов Ij первый элемент И 2, блок формирователей адресных токов, накопитель -4, второй элемент И 5, счетчик 6, блок управления 7, дешифратор 8, блок 9 формирователей разрядных токов, регистр чцспа Ю, Первый выход генератора импульсов 1 через последовательно включенные пер вый элемент И 2 а блок 3 формирователей адресных токов подключен к первому входу накопителя 4. Второй выход генератора 1 через последовательно вкл ченные второй элемент И 5, счетчик 6, блок управления 7, дешифратор 8 и блок 9 формирователей разрядных токов соединен со вторым входом накопителя 4 . Второй выход блока управления 7 связан с первым элементом И 2 , а тре тий выход - с вторым элементом И 5. Второй выход счетчика 6 подключен ко второму, а регистр числа 10 - к третьему входам дешифратора 8. В режиме записи информации блок управления 7 вырабатывает сигналы на первый 2 и второй 5 элементы И. В результате этого начинает работать блок 3 формирователей адресных токов и по выбранной адресной обмотке нак пителя 4 протекает адресный ток. Кром того, с выхода второго элемогга И 5 н счетчик, который в исходном Состоянии обнулен, поступают счетные сигналы. Бл управления 7 вырабатьгоает сигнал опро дешифратора 8, запускающий блок 9 фор мирователей разрядных токов. Направлением разрядных трков управ ляет дешифратор 8. G этой целью дешифратор дешифрирует состояние счетчика и соответствующего разряда регистра числа 10, При этом направления токов разрядных обмотках накопителя 4 соответствуют звписьтаемой информации. Совместное воздействие на запоминающие элементы выбранных адресов адресных и координатных токов приводит их в определенные магнитные состояния, т.е. обеспечивает запись информации. Кроме того, запоминающие элементы невыбранных адресов подвергаются воздействию разрядных токов, что приводит к частичному разрушению информации в тех элементах, в которые запись информации производилась током обратного направления. Эти процессы кончаются при достижении счетчиком некоторого заданного состояния, после чего блок управления 7 вьфабатьгоает на первый элемент И 2 сигнал запрета и блок 3 прекращает свою работу. Начинается процесс компенсации частичных разрушений информации в запоминающих элементах иевыбранных адресов. Счетчик продолжает работать, но начиная с указанного момента все его последующие состояния обеспечивают противоположное направление разрядных токов. Процесс компенсации прекращается при полном заполнении счетчика 6. Блок управления 7 заканчивает опрос блока дешифраторов 8, прекращая действие разрядных токов, и запрещает подачу со второго элемента И 5 сигналов на счетчик 6. Применение предлагаемого устройства позволяет за счет компенсации частичных разрушений информации примерно на 20% повысить нижний уровень выходных сигналов с накопителя. В результате возрастает надежность устройства, снижаются требования к запоминающим элементам, к характеристикам усилителей считывания. Формула изобретения Запоминающее устройство системы 2Д с неразрушающим считыванием информации на многоотверстных ферритовых элементах, содержащее регистр числа, генератор импульсов, первый выход которого подключен к первому входу первого элемента И, а второй выход - к первому входу второго элемента И, блок управления, первый выход которого подключен ко второму входу первого элемента И, а второй выход - ко второму входу второго элемента И, выход первого элемента И через блок формирователей адресных токов подключен к первому входу накопителя, блок формирователей разрядных токов, выход которого подключен ко второму входу накопителя, и дешифратор.

бтличающееся тем, что, с целью повышения надежности устройства путем компенсации частичных разрушений информции, оно содержит счетчик, вход которого соединен с выходом второго элемента И, первый выход - со вхоцоМ блока управления, второй выход - с первым входом дешифратора, второй вход которого соединен с выходом регистра числа, а третий вход - с третьим выходом блока

управления, пыхпц пешифрптора 11оаклк. чен ко входу блока формирователей разрядных токов.

Источники информации, принятые во внимание при экспертизе;

1.Патент США Nib 3435426, кл. 340-174, 1969.

2.Генкин В, Л. Запоминающие устроства. Тонкие магнитные пленки М

Наука, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство со считыванием без разрушения информации | 1979 |

|

SU773724A1 |

| Запоминающее устройство без разрушения информации | 1978 |

|

SU750563A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

Авторы

Даты

1978-11-05—Публикация

1977-03-11—Подача