1

Изобретение относится к области автоматики и вычислительной техники и предназначено для деления последовательности входных импульсов на 5.

Известен делитель на 5, содержащий 3 ячейки, каждая из которых состоит из логического элемента «И-НЕ, выход которого подключен к первому входу элемента памяти и коммутационного триггера, единичный вход которого соединен с выходом элемента памяти и с одним из входов логического элемента «И- НЕ, единичный выход - с другим входом логического элемента «И-НЕ, а нулевой выход - с единичным входом элемента памяти.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в первую ячейку введен вспомогательный логический элемент «И-НЕ, первый вход которого соединен с выходом логического элемента «И-НЕ, второй вход - с нулевым входом коммутационного триггера, со вторыми входами элементов памяти порвой и второй ячеек, а выход - с третьим и вторым входами элементов памяти второй и третьей ячеек соответственно, во вторую ячейку введены дополнительный элемент памяти, и вспомогательный логический элемент «И-НЕ, выход которого соединен со

входом дополнительного элемента памяти, первый вход - с выходом логического элемента «И-НЕ, а второй вход - с выходом дополнительного элемента памяти, при этом четвертый вход элемента памяти второй ячейки соединен с единичным выходом коммутацийнного триггера третьей ячейки.

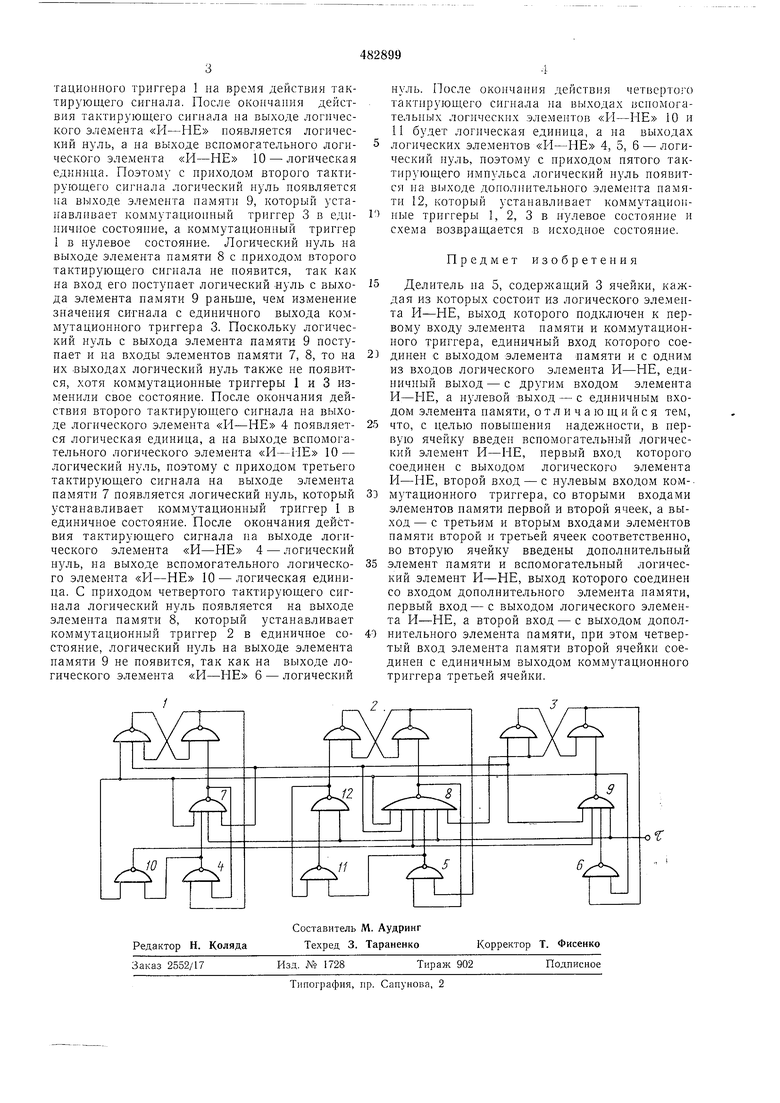

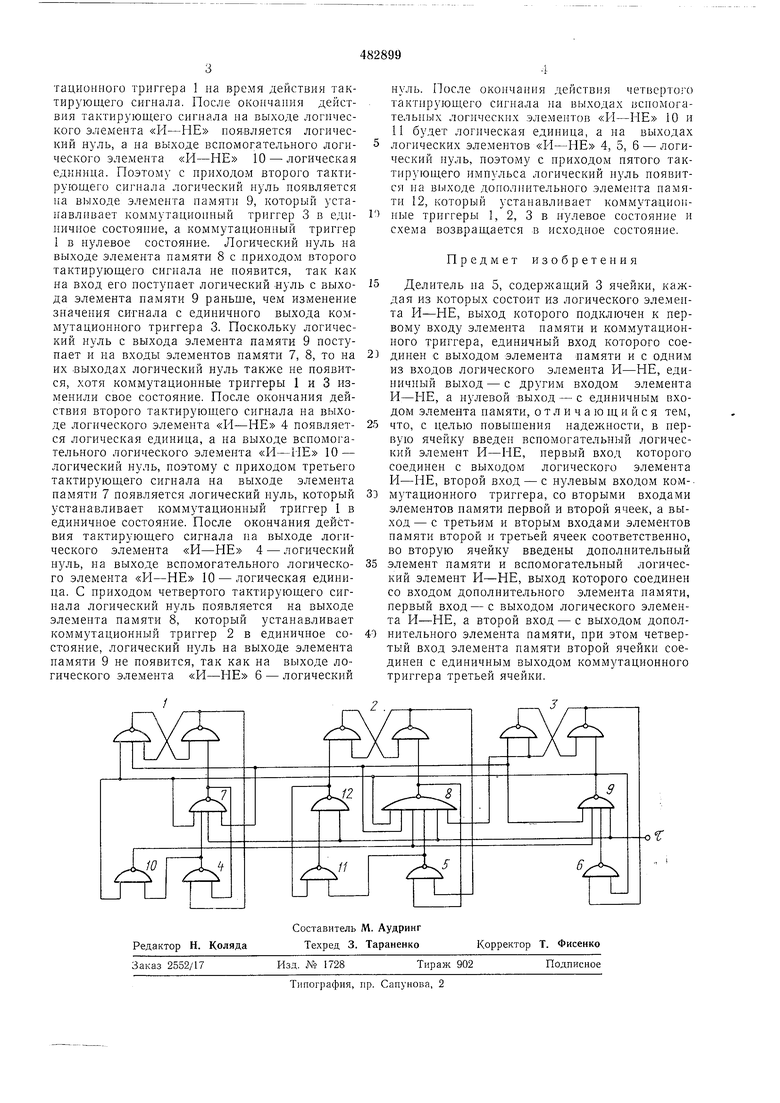

На чертеже изображена схема делителя на 5.

В состав делителя на 5 входят коммутационные триггеры 1-3, логические элементы «И-НЕ 4-6, элементы памяти 7-9, вспомогательные логические элементы «И-НЕ 10, 11, дополнительный элемент памяти 12.

В исходном состоянии все коммутационные триггеры 1-3 находятся в нулевом состоянии. При отсутствии тактирующего сигнала т, равного логическому нулю, на выходах логических элементов «И-НЕ 4-6, элементов памяти 7-9, дополнительного элемента памяти 12 - логическая единица, па выходе вспомогательных логических элементов «Н-НЕ 10, 11 - логический нуль. С приходом первого тактирующего импульса т на выходе элемента памяти 7 появляется логический нуль, который устанавливает коммутационный триггер в единичное состояние. Связь с выхода элемента памяти 7 на вход логического элемента «И-НЕ 4 служит для

запоминания предыдуплего состояния комму

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1975 |

|

SU552638A1 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Регистр сдвига | 1980 |

|

SU877618A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты на 1,5 | 1976 |

|

SU566359A1 |

| Делитель частоты на 4,5 | 1977 |

|

SU677106A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

Авторы

Даты

1975-08-30—Публикация

1972-08-25—Подача