Изобретение отноомтся к автоматике и вычислительной технике и может быть исполыювано в устройствах измерения временных интервалов, а также в устройствах оиреле.юиия координат.

В основном авт. св. Хй 418982 онисано устройство, содержан1ее четыре разряда, каждый из которых содержит триггер памяти, ком.мутациоиный триггер и элемент И-НЕ, причем единичный выход триггера намяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен с входом элемента И-НЕ, а нулевой выход соединен с едикичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти всех предыдущих разрядов и с входом элемента И-НЕ предыдущего разряда, выходы элементов И-НЕ первого и второго разрядов соединены с обоими входами коммутационных триггеров соответственно второго и третьего разрядов, выход элемента И-НЕ третьего разряда соединен с нулевым входом коммутационного триггера четвертого разряда, выход элемента И-НЕ четвертого разряда соединен с

входом дополнительного элемента И-НЕ, выход которого соединен с входом элемента И-НЕ четвертого разряда и с нулевыми входами всех триггеров памяти и коммутационных триггеров делителя 1. Однако известное устройство недостаточно надежно.

Цель изобретения - повышение надежности устройства в работе.

Это достигается тем, что в двоичном счетчике, содержащем четыре разряда, каждый из которых содержит триггер памяти, коммутационный триггер и элемент И - НЕ, выход элемента И-НЕ второго разряда подключен к единичному входу коммутационного триггера четвертого разряда.

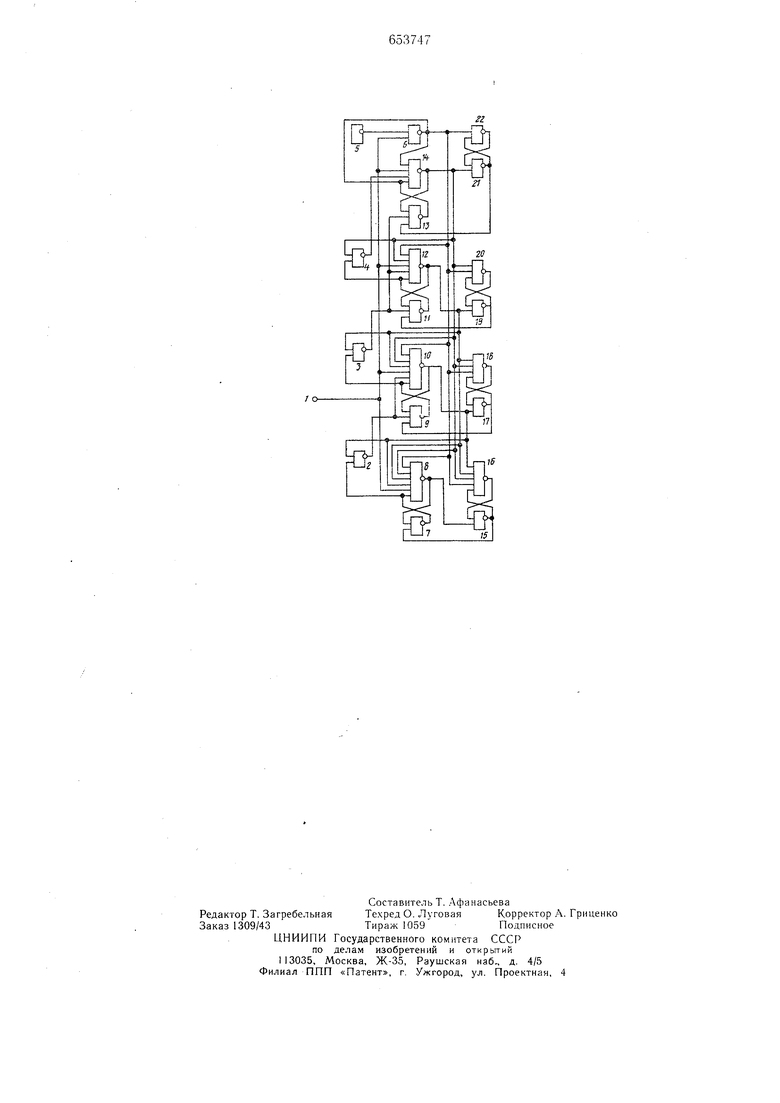

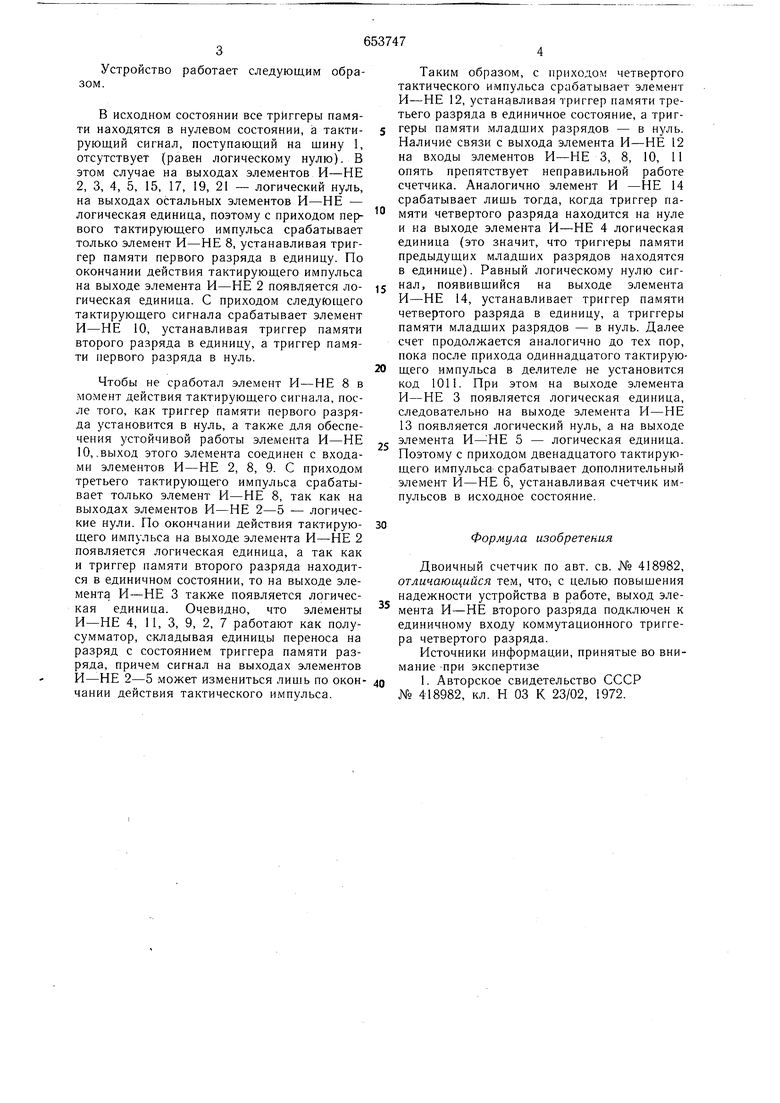

На чертеже изображена структурная электрическая схема двоичного счетчика.

Двоичный счетчик содержит тину 1 тактируемого сигнала, элементы И-НЕ 2-5 cootBeTCTBCHHo первого-четвертого разрядов, дополнительный элемент И - НЕ 6, элементы И-НЕ 7-14, попарно образующие коммутационные триггеры соответственного первого-четвертого разрядов, элементы И-НЕ 15-22, попарно образующие триггеры памяти соответственно первого-четвертого разрядов. Устройство работает следующим образом. В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а тактирующий сигнал, поступающий на шину 1, отсутствует (равен логическому нулю). В этом случае на выходах элементов И-НЕ 2, 3, 4, 5, 15, 17, 19, 21 - логический нуль, на выходах остальных элементов И-НЕ - логическая единица, поэтому с приходом первого тактирующего импульса срабатывает только элемент И-НЕ 8, устанавливая триггер памяти первого разряда в единицу. По окончании действия тактирующего импульса на выходе элемента И-НЕ 2 появляется логическая единица. С приходом следующего тактирующего сигнала срабатывает элемент И-НЕ 10, устанавливая триггер памяти второго разряда в единицу, а триггер памяти первого разряда в нуль. Чтобы не сработал элемент И-НЕ 8 в момент действия тактирующего сигнала, после того, как триггер памяти первого разряда установится в нуль, а также для обеспечения устойчивой работы элемента И-НЕ 10, .выход этого элемента соединен с входами элементов И-НЕ 2, 8, 9. С приходом третьего тактирующего импульса срабатывает только элемент И-НЕ 8, так как на выходах элементов И-НЕ 2-5 - логические нули. По окончании действия тактирующего импульса на выходе элемента И-НЕ 2 появляется логическая единица, а так как и триггер памяти второго разряда находится в единичном состоянии, то на выходе элемента И-НЕ 3 также появляется логическая единица. Очевидно, что элементы И-НЕ 4, 11, 3, 9, 2, 7 работают как полусумматор, складывая единицы переноса на разряд с состоянием триггера памяти разряда, причем сигнал на выходах элементов И-НЕ 2-5 может измениться лишь по окончании действия тактического импульса. Таким образом, с приходом четвертого тактического импульса срабатывает элемент И-НЕ 12, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти .младщих разрядов - в нуль. Наличие связи с выхода элемента И-НЕ 12 на входы элементов И-НЕ 3, 8, 10, 11 опять препятствует неправильной работе счетчика. Аналогично элемент И -НЕ 14 срабатывает лишь тогда, когда триггер памяти четвертого разряда находится на нуле и на выходе элемента И-НЕ 4 логическая единица (это значит, что триггеры памяти предыдущих младших разрядов находятся в единице). Равный логическому нулю сигнал, появившийся на выходе элемента И-НЕ 14, устанавливает триггер памяти четвертого разряда в единицу, а триггеры памяти младших разрядов - в нуль. Далее счет продолжается аналогично до тех пор, пока после прихода одиннадцатого тактирующего импульса в делителе не установится код 1011. При этом на выходе элемента И-НЕ 3 появляется логическая единица, следовательно на выходе элемента И-НЕ 13 появляется логический нуль, а на выходе элемента 5 - логическая единица. Поэтому с приходом двенадцатого тактирующего импульса срабатывает дополнительный элемент И-НЕ 6, устанавливая счетчик импульсов в исходное состояние. Формула изобретения Двоичный счетчик по авт. св. № 418982, отличающийся тем, что-, с целью повыщения надежности устройства в работе, выход элемента И-НЕ второго разряда подключен к единичному входу коммутационного триггера четвертого разряда. Источники информации, принятые во внимание -при экспертизе 1. Авторское свидетельство СССР № 418982, кл. Н 03 К 23/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на шесть | 1976 |

|

SU617846A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Двоично-десятичный счетчик | 1974 |

|

SU506131A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Быстродействующий счетчик | 1977 |

|

SU677107A2 |

Авторы

Даты

1979-03-25—Публикация

1976-12-03—Подача