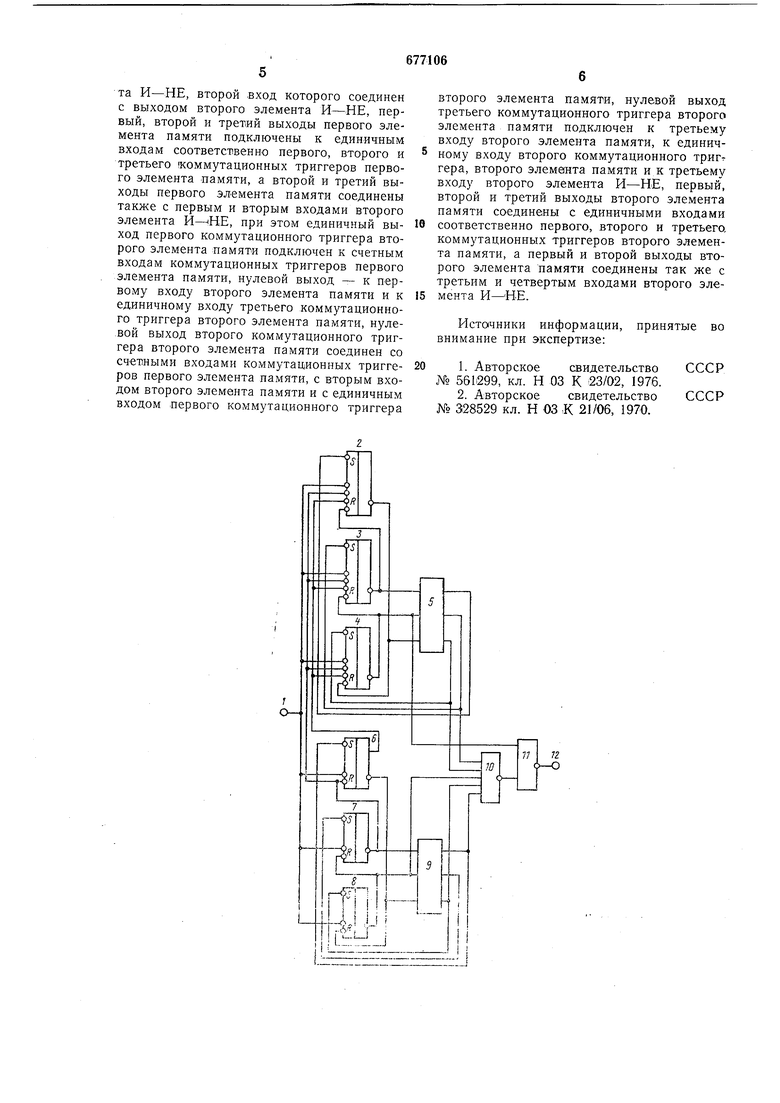

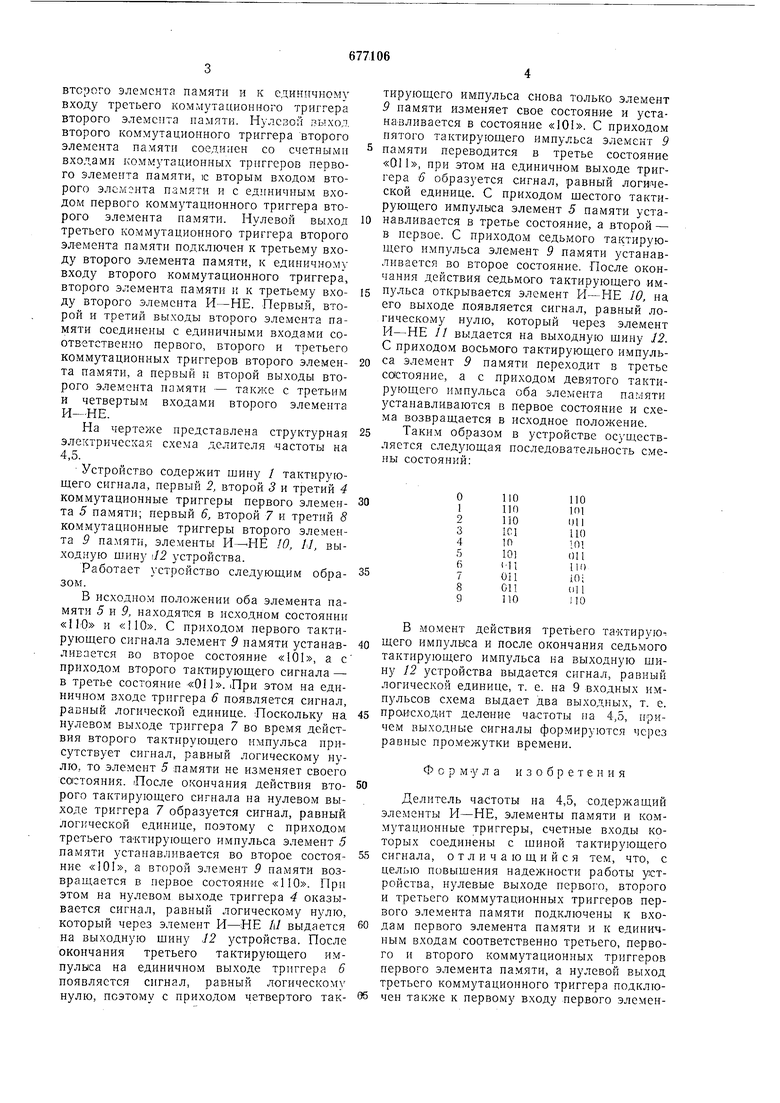

втсрого элемента памяти и к единпч юму входу третьего коммутационного триггера второго элемента памяти. Нулезо второго коммутационного триггера второго элемента памяти соединен со счетными входами коммутационных триггеров первого элемента памяти, ю вторым входом второго элемента памяти и с единичным входом первого коммутационного триггера второго элемента памяти. Нулевой выход третьего коммутационного триггера второго элемента памяти подключен к третьему входу второго элемента памяти, к единичному входу второго коммутационного триггера, второго элемента памяти и к третьему входу второго элемента И-НЕ. Первый, второй и третий выходы второго элемента памяти соединены с единичными входами соответственно первого, второго и третьего коммутационных триггеров второго элемента памяти, а первый и второй выходы второго элемента памяти - также с третьим и четвертым входами второго элемента И-НЕ. На чертеже представлена структурная электрическая схема делителя частоты на 4,5. Устройство содержит шину / тактирующего сигнала, первый 2, второй 3 и третий 4 коммутационные триггеры первого элемента 5 памяти; первый 6, второй 7 и третий 8 коммутационные триггеры второго элемента 9 памяти, элементы 10, 11, выходную шину 12 устройства. Работает устройство следующим образом. В исходном положении оба элемента памяти 5 и Я находятся в исходном состоянии «110 и «110. С приходом первого тактирующего сигнала элемент 9 памяти устанавливается во второе состояние «101, а с приходом второго тактирующего сигнала - в третье состояние «01 Ь. Лри этом на единичном входе триггера 6 появляется сигнал, равный логической единице. Поскольку на нулевом выходе триггера 7 во время действия второго тактирующего импульса присутствует сигнал, равный логическому иулю, то элемент 5 памяти не изменяет своего состояния. После окончания действия второго тактирующего сигнала на нулевом выходе триггера 7 образуется сигнал, равный лопгческой единице, поэтому с приходом третьего тактирующего импульса элемент 5 памяти устанавливается во второе состояние «101, а второй элемент 9 памяти возвращается в первое состояние «ПО. При этом на нулевом выходе триггера 4 оказывается сигнал, равный логическому нулю который через элемент И-НЕ выдается на выходную щину ,12 устройства. После окончания третьего тактирующего им пульса на единичном выходе триггера 6 появляется сигнал, равный логическому нулю, поэтому с приходом четвертого так ирующего импульса снова только элемент памяти изменяет свое состояние и устаавливается в состояние «101. С приходом ятого тактирующего импульса элемент 9 амяти переводится в третье состояние 011, при этом на единичном выходе тригера 6 образуется сигнал, равный логи1ческой единице. С приходом щестого тактиующего импулыса элемент 5 памяти устанавливается в третье состояние, а второй - в первое. С приходом седьмого тактирующего импульса элемент 9 памяти устанавливается во второе состояние. После окончания действия седьмого тактирующего импульеа открывается элемент 10, на его выходе появляется сигнал, равный логическому нулю, который через элемент И-НЕ // выдается на выходную щину 12. С приходом восьмого тактирующего импульса элемент 9 памяти переходит в третье состояние, а с приходом девятого тактирурощего импульса оба элемента памяти устапавливаются в первое состояние и схема возвращается в исходное положение. Таким образом в устройстве осуществляется следзаощая последовательность смены состояний: В момент действия третьего тактирующего импулыса и после окончания седьмого тактирующего импульса ка выходную итну 12 устройства выдается сигнал, равный логической единице, т. е. на 9 входных импульсов схема выдает два выходных, т. е. происходит деление ча|Стоты на 4,5, причем выходные сигналы формируются через равные промежутки времени. Формула изобретения Делитель частоты на 4,5, содержащий элементы И-НЕ, элементы памяти и коммутационные триггеры, счетные входы которых соединены с шиной тактирующего сигнала, отличающийся тем, что, с целью повышения надежности работы устройства, нулевые выходе первого, второго и третьего коммутационных триггеров первого элемента памяти подключены к входам первого элемента памяти и к единичным входам соответственно третьего, первого и второго коммутационных триггеров первого элемента памяти, а нулевой выход третьего коммутационного триггера подключен также к первому входу первого элемен

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Быстродействующий счетчик | 1977 |

|

SU677107A2 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель частоты на 1,5 | 1976 |

|

SU566359A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель частоты на девять | 1977 |

|

SU687603A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

Авторы

Даты

1979-07-30—Публикация

1977-04-01—Подача