1

Изобретение относится к цифровой вычислительной технике.

Устройство может быть иснользовано в цифровых вычислительных машинах и системах автоматического управления, имеющих средства аппаратного контроля.

Известно устройство контроля сумматора по модулю, содержащее регистр результата, первые три группы входов которого подключены соответственно к выходным шинам коптролируемого сумматора результатов операций поразрядного сложения, логического сложения и умножения, а выходы регистра результата соединены со входами первого узла свертки по модулю, выходы которого подключены к первой группе входов узла сравнения, вторая группа входов которого связана с выходами сумматора контрольных характеристик, первая группа входов которого соединена со входами устройства, и второй узел свертки по модулю.

В данном устройстве для контроля логической операции выполняемой на сумматоре, необходимо первоначально выполнять вспомогательную логическую операцию и получить от ее результата свертку по модулю, необходимую для получения в сумматоре контрольных характеристик ожидаемой контрольной характеристики .основной логической операции. В следующем такте выполняется основная логическая операция, вычисляются свертки ее результата по модулю, которая сравнивается с результатом сумматора контрольных характеристик.

Следовательно, выполнение логической Операции с контролем осуществляется в два такта.

Цель предлагаемого устройства - повысить быстродействие.

Это достигается тем, что устройство содержит блок сдвига, выходы которого соединены со второй группой входов сумматора коптрольных характеристик, при этом первая группа входов блока сдвига соединена с выходами второго узла свертки по модулю, а вторая группа входов -с дополнительными входами устройства, со второй группой входов регистра результата и с первой группой входов блока переключения, вторые две группы входов которого соединены соответственно с выходными шинами контролируемого сумматора результатов операции логического сложения и умножения, а выходы со входами контрольного регистра, выходы которого подключены ко входам второго узла свертки по модулю.

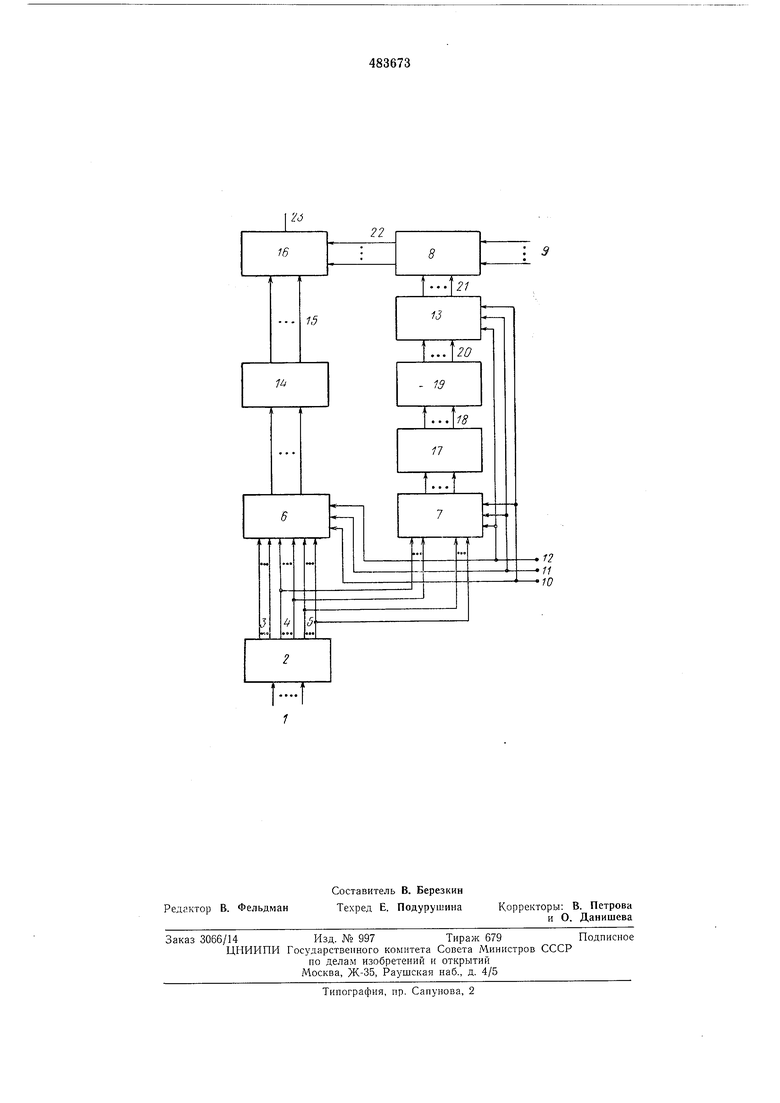

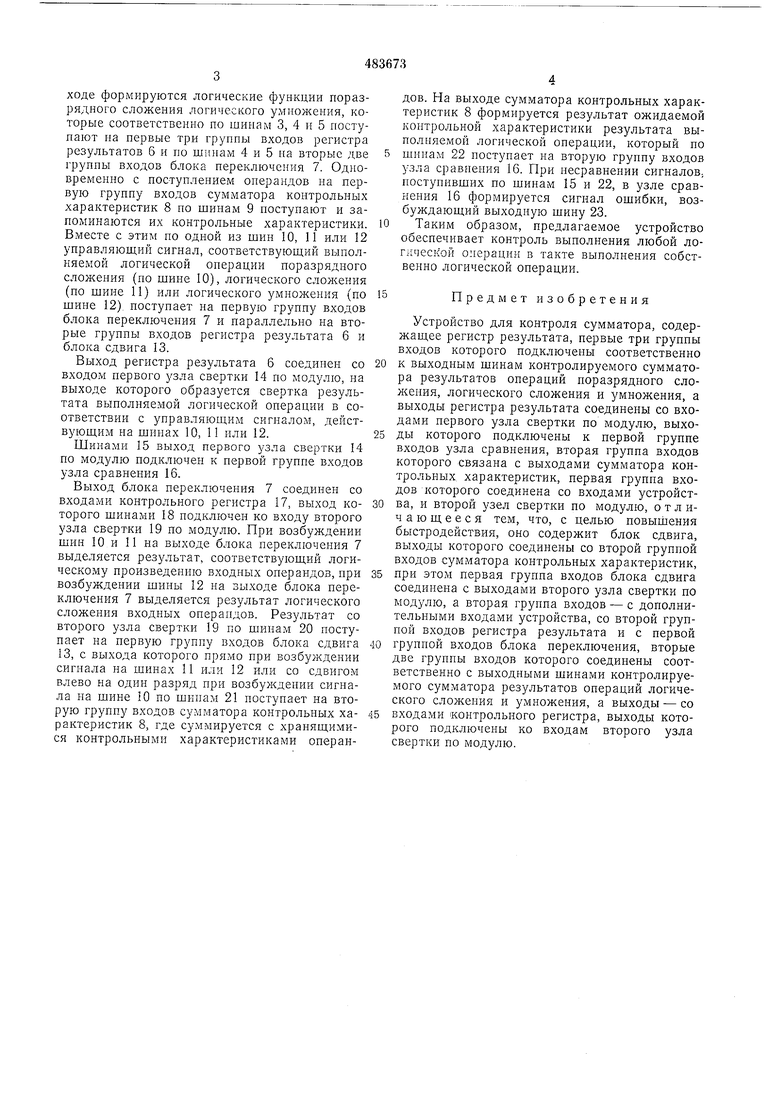

На чертеже представлена блок-схема предлагаемого устройства.

При поступлении по шинам 1 операндов на вход контролируемого сумматора 2 на его выходе формируются логические функции поразрядного сложения логического умножения, которые соответственно по шииам 3, 4 и 5 поступают на первые три группы входов регистра результатов 6 и по шпнам 4 и 5 иа вторые две группы входов блока переключения 7. Одновременно с поступлением операндов на первую группу входов сумматора контрольных характеристик 8 по шинам 9 поступают и запоминаются их контрольные характеристики. Вместе с этим по одпой из шип 10, 11 или 12 управляющий сигнал, соответствующий выполняемой логической операции поразрядного сложения (по шипе 10), логического сложения (по шине 11) или логического умножения (по шипе 12). поступает на первую группу входов блока переключения 7 и параллельно иа вторые группы входов регистра результата 6 и блока сдвига 13.

Выход регистра результата 6 соединеи со входом первого узла свертки 14 по модулю, на выходе которого образуется свертка результата выполняемой логической операции в соответствии с управляющим сигналом, действующим на шинах 10, 11 или 12.

Шинами 15 выход первого узла свертки 14 по модулю подключен к первой группе входов узла сравнеиия 16.

Выход блока переключепия 7 соединен со входами контрольного регистра 17, выход которого шинами 18 подключен ко входу второго узла свертки 19 по модулю. При возбуждении шин 10 и 11 иа выходе блока переключения 7 выделяется результат, соответствующий логическому произведению входных операндов, при возбуждении шины 12 на выходе блока переключения 7 выделяется результат логического сложепия входных операндов. Результат со второго узла свертки 19 по шииам 20 поступает на первую группу входов блока сдвига 13, с выхода которого прямо при возбуждении сигнала на шииах II или 12 или со сдвигом влево на один разряд при возбуждении сигнала на шине 0 по шипам 21 поступает на вторую группу входов сумматора контрольных характеристик 8, где суммируется с хранящимися контрольными характеристиками операндов. На выходе сумматора контрольных характеристик 8 формируется результат ожидаемой контрольной характеристики результата выполняемой логической операции, который по шпнам 22 поступает на вторую группу входов узла сравнеиия 16. При несравнении сигналов., поступивших по шинам 15 и 22, в узле сравнения 16 формируется сигнал ошибки, возбуждающий выходную шииу 23.

Таким образом, предлагаемое устройство обеспечивает контроль выполнения любой лоГ11ческой операции в такте выполнения собственно логической операции.

Предмет изобретения

Устройство для контроля сумматора, содержащее регистр результата, первые три группы входов которого подключены соответственно к выходным щинам контролируемого сумматора результатов операций поразрядного слол ения, логического сложения и умножения, а выходы регистра результата соединены со входами первого узла свертки по модулю, выходы которого подключены к первой группе входов узла сравнения, вторая группа входов которого связана с выходами сумматора контрольных характеристик, первая группа входов которого соединена со входами устройства, и второй узел свертки по модулю, отличающееся тем, что, с целью повыЩення быстродействия, оно содержит блок сдвига, выходы которого соединены со второй группой входов сумматора контрольных характеристик, при этом первая группа входов блока сдвига соединена с выходами второго узла свертки по модулю, а вторая группа входов - с дополнительными входами устройства, со второй группой входов регистра результата и с первой группой входов блока переключения, вторые две группы входов которого соединены соответственно с выходными шинами контролируемого сумматора результатов операций логического сложения и умножения, а выходы - со входами контрольиого регистра, выходы которого подключены ко входам второго узла свертки по модулю.

: 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для диагностики группы типовых элементов замены | 1977 |

|

SU857996A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Матричный сумматор | 1987 |

|

SU1582187A1 |

| Микропроцессор | 1977 |

|

SU717772A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Авторы

Даты

1975-09-05—Публикация

1972-12-15—Подача