симального и минимального значении коорди-наты у, Первый и второй выходы KOToiporo соеди1не«ы с соответствующими входам;и входного блока, а третий 1И четвертый выход С первыми двумя входами блока формиро)ван:ия приращения произведения переменных интегрирования, первый выход которого соединен с другим входом блока умножения, второй выход - со входом регистра текущего значения координаты у, выход которого соединен с третьим .входом блока формирования произведения иере,мвнных интегрирования, четвертый /вход которого соединен с выходом бло:ка сра|В|НеиИЯ, один вход которого соединен с выходом регн-стра текущего з«аче 111Я координаты х, прнчем вход этого регистра, пятый вход блока форм;ироваиия приращения переменных интегрирования и вход функционального блока вычисления лрярап гния - подынтегральной функции и максимального и минимального значения коо1р|Динаты у подсоединены к нерзому входу устройства, другой вход блока сравнения подсоединен ко второму входу устройства, а щестой вход блока форм ирования приращения проиэведеиия переменных ий-тегрирования - к третьему входу устройства.

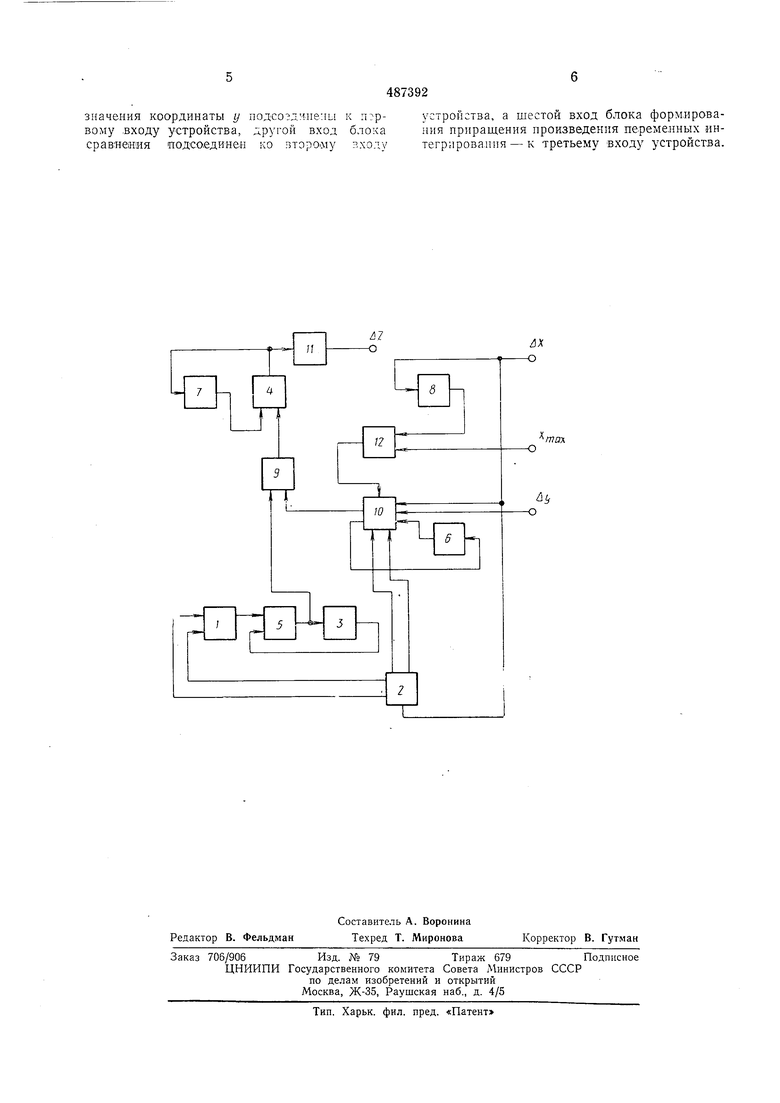

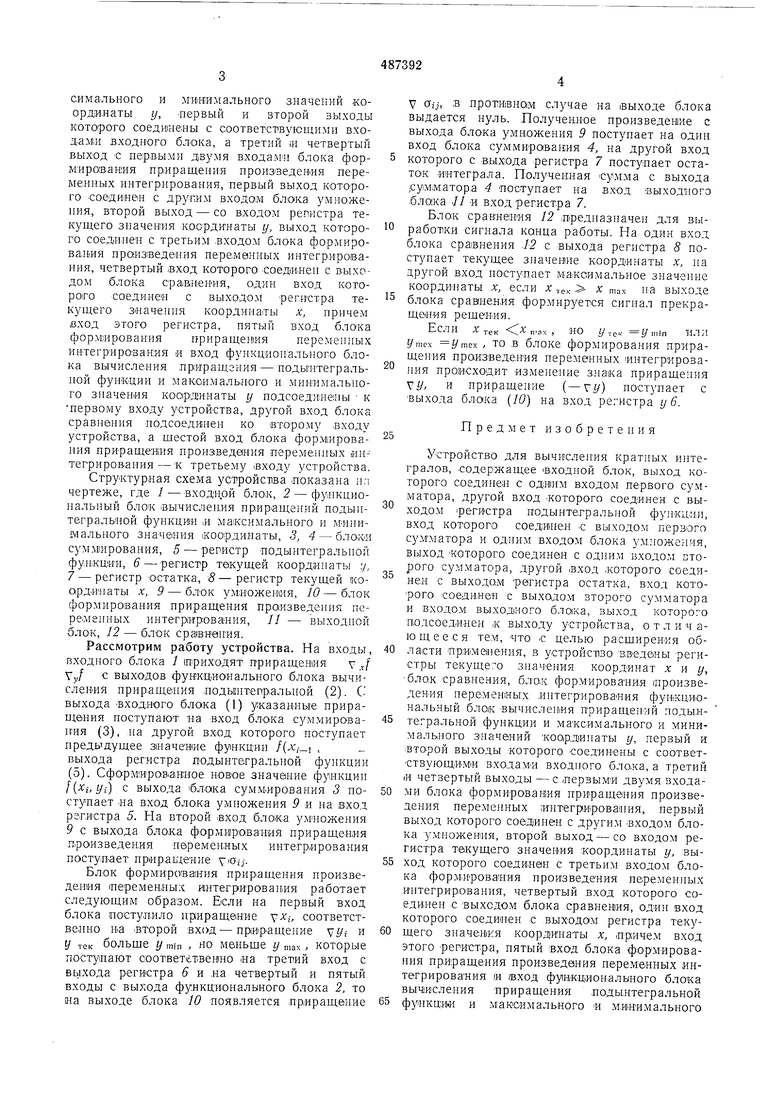

Структурная схема устройст1ва показана нп чертеже, где /-входной блок, 2 - функциональный блок вычисления пр1иращений подынтегральной функции я ма ксимальиого и минимального зна-чения координаты, 3, 4 - блож-i суммирования, 5 - регистр подынтегральной фун1КЦ ии, 6 - регистр текущей координаты у, 7 - регистр остатка, 8 - регистр текущей координаты X, 9 - блок ум:ножен1ия, 10 - блок формирования приращения произведения переменных интегра-грования, // - выходной блок, 12 - блок сращнвния.

Рассмотрим работу устройства. На входы, входного блока / приходят приращения v ,vf Vy/ с выходов функционального блока вычисления прираще-ния лодьш1телр|алы10Й (2). С выхода ВХОДНОГО блока (1) указанные приращения поступают на вход блока суммирования (3), на другой вход которого поступает нредыдущее значение функции /(А ,., , выхода регистра подынтегральной функции (5). Сформиров авное новое значение функции l(Xi,yi с выхода блока суммирования 3 поступает на вход блока умножения 9 и на вход регистра 5. На второй 1вход блока умножения 9 с выхода блока формирования приращения произведения неременных интегрирования поступает приращение VC OБлок формироваиия приращения произведения переменных интегрирования работает следующим образом. Если на первый вход блока поступило приращение Xi, соответственно на :второй вход - приращение и

у тек больше у min , НО МбНЬШе у max , KOTOipbie

поступают соответственно на третий вход с вь,1хода perHiCTpa 6 и .на четвертый и пятый входы с выхода функционалыного блока 2, то на выходе блока 10 появляется приращение

V 0ij, ;в противном случае на выходе блока выдается нуль. .Полученное произведение с выхода блока умножения 9 поступает на один вход блока суммирования 4, на другой вход

которого с выхода регистра 7 поступает остаток интеграла. Полученная -сумма с выхода сум;матора 4 поступает на вход выходного бло:ка Л и вход регистра 7.

Блок сравнения 12 предназначен для выработки сигнала конца работы. На один вход блока сравнения .12 с выхода регистра 8 поступает текущее значение координаты х, на другой вход поступает м-аксимальное значение координаты X, если х х шах на выходе

блока сраннения формируется сигнал прекращения рещения.

Если J: тек Л: п.эх , но У то-- i/min ИЛ;1

/mcx г/тех . ТО .В блоке формирования приращения произведения переменных интегрирования происходит изменение знака приращения у, и приращен:ие (-Vi/) поступает с выхода блока (10) на вход регистра у 6.

Предмет изобретения

Устройство для вычисления кратных интегралов, содержащее входной блок, выход которого соединен с одним входом первого сумматора, другой вход которого соединен с выходом фегистра подынтегральной функции, вход которого соединен с выходом первого сумматора и одним входом блока ум.ножения, выход которого соединен с одним входом второго сумматора, другой вход которого соедине.н с ВЫХОДО.М регистра остатка, вход которого соединен с выходом второго сумматора и входом выходного блака, выход которого подсоеди.нен ,к выходу устройства, отличающееся те:«, ЧТО с целью расщирения области при.ме1нення, в устройство в.ведены регистры текуще:О значения координат х и у, блок сравнения, блок формирования /произведения переменных .интегрирования функциональный блок вычисления приращеНИЙ нодынтегральной функции и максимального и минимального значений координаты у, первый и второй выходы которого соединены с соответствующими входами входного бло.ка, а третий и четвертый выходы -с первыми двумя входами блока формирования приращения произведения перемен.ных интегрирования, первый выход которого соединен с другим входом блока умножения, второй выход - со входом регистра текущего значения координаты у, выход которого соединен с третьим входом блока формирования произведения переменных интегрирования, четвертый вход которого соединен с выходо.м блока сравнения, один вход которого соединен с выходом регистра текущего значения координаты х, причем вход этого регистра, пятый вход блока формирования приращения произведения переменных интегрирования 1И явход функционалиного блока выч1исления приращения .по.ды.нтегралы-юй

функций и максимального и м.ини.мального

значения координаты у подсоздмпелы к первому входу устройства, другой вход блока сравнения подсоединен ко второ му ,ходу

устройства, а шестой вход блока формирования приращения произведения переменных интегрирования-к третьему входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления кратных интегралов | 1974 |

|

SU547792A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU650085A2 |

| Детерминированно-вероятностный интегратор | 1979 |

|

SU857990A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

/77 ДЛ

Авторы

Даты

1975-10-05—Публикация

1973-08-07—Подача