(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КРАТНЫХ ИНТЕГРАЛОВ

рзгиотра остатка,, вход которого соу.о:;,л:а;/: с. ..л:;:.ом5М ьторогю сумматора 2j,

Кэпоо-лтко ; указанного устройства является то, что при отыскании интеграла Hcnoribауется ст.упан:-1а- -ая аппроксимация функции iiX-.Y; и гршниды области. Это приводит к большим погрешностям при интегрировании.

Цель изобретения - повысить точность интегрирования кратных интегралов.

Поставленная цель достигается тем, что Б устройсолзо введены блок формирования до- полнктельного кода, третий сумматор и блок интегрирования граничной области, причем вход блока формирования дополнительного ко да соединен с выходом входного регистра, а выход блока формирования дополнительного кода соединен с первым входом третьего cyiv:MaTOpa, второй вход которого соединен с выходом второго сумматора, а выход - со зторьцу: входом блока умножения, входы блокв кнтег-риэования граничной области соединены сс-ответственно с третьим выходом блоха (Ьормирования прирашенкй произведения )1ере:-Лев:ны: :, четвертым входом устройства и тэетьим втяходом блока вычисления прира- шенпй :;эдьшгеграпьнэй функции и максимального к минимального значений координаты У, а выход С седьмым входом блока формирования приращений произведений переменных

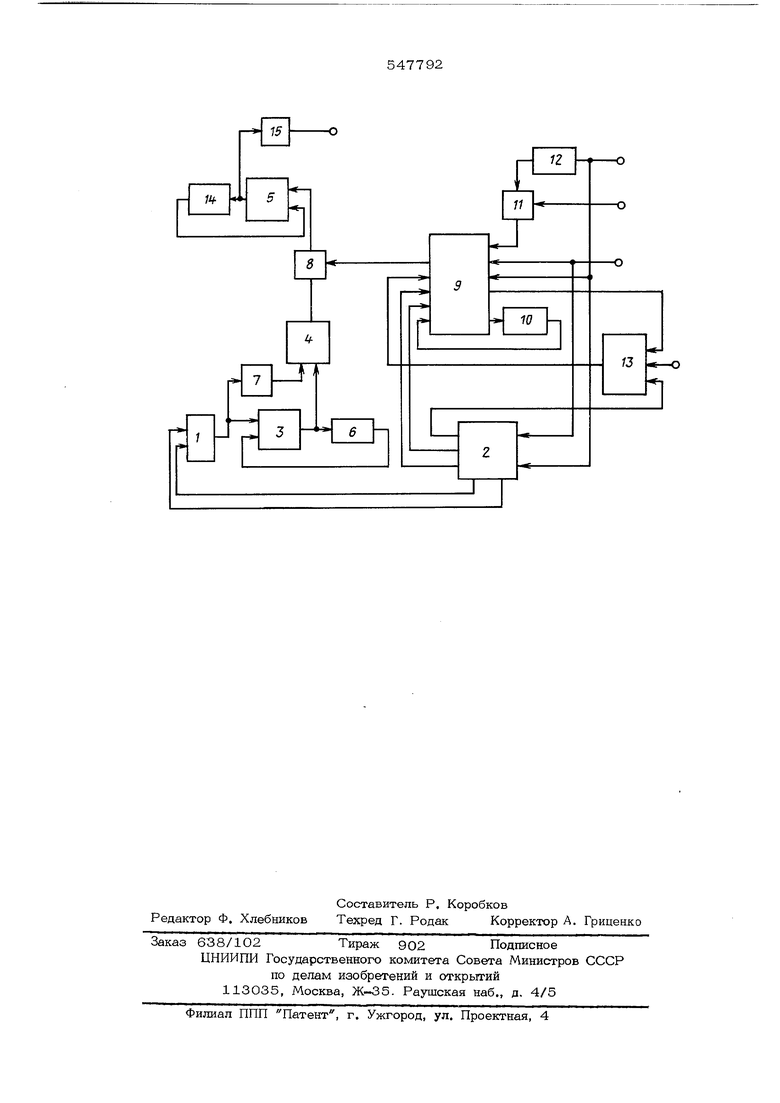

Ма чертеже показана структурная схема устройства д.яя интегрирования кратных интегралов.

Устройство содержит входной регистр 1, блок 2 вычисления приращений подынтегральной функции 1л максимального и минимально- ГС злачеаий У, сумматоры 3, 4, 5, регистр G подынтегральной функции, блок 7 формировамня дополнительного кода, блок 8 умно- /;;е;1И5 ,, блок 9 |Ьормирования приращений про азведения переменных, регистр 10 текущего значения координаты У, схему 11 сравнения, регистр 12 текущего значения координаты X. блок 13 интегрлрования граничной сблас- T;I. регистр 14 остатка, блок 15 выработки ;::р ;ра ца;;и: й„

Приращения переменных с выхода блока 2 постуигнот на входы з;содного регистра 1. га зь:ходе сумматора 3 формируется новое значение подь чтегральной функции, которое aiiijocKTCH в регистр 6 и хранится до сле A:7;oiaero тага интегрирования. На выходе блока 7 образования дополнительного кода пюрмируется дополнительный код содержимо- го регистра 1, а на вьвсоде сумматора 4 - сумма предыдущего значения функции и прирсщэнкй; которая лостуиает на блок умножения 8 на второй вход которого поступает приращение преизведепня пэременш-згх из блока

13. Это приращение формируетсяследующим образом

Для формирования приращения используется блок 13, на один вход которого поступает значение функции с выхода блока 2, на второй вход поступает масштабированное приращение с коэффициентом К « 1. Такой выбор величины К обусловлен точностью интегрирования на границе. По сиг налу разрешения, поступающему с выхода блока формирования приращений произведения переменных, происходит интегрирование подфункции в пределах приращения однойкоординаты. Полученная площадь и есть знач&ние приращения произведения переменных на границе, которое с выхода блока 2 через блок 9 поступает на блок 8 умножения. Аналогично для следующего гфиращения и так до границы прямоугольной области, после чего выдается сигнал и формируется новое значение другой координаты. Затем производится интегрирование на новой прямой, В граничной области работает блок 13, и процесс интегрирования протекает аналогично описанному. Как только интегрирование начинает вестись внутри ступенчатой прямоугольной области, этот момент фиксируется в блоке 9, выключается блок 13 соответствутощим сигналом по шине управления и в блоке 9 формирования приращений произведения переменных начинают вырабатываться приращения произведения переменных, равные произведению соответствующих приращений координат.

На границе может быть выделено не два участка, на которых заданы граничные функции, а нескопько,причем независимая переменная может быть как X, гак и У. Числ о участков зависит от конфигурации границы. При этом переход с одной переменной на другую в граничном блоке совершенно не кэменяет его структуры и принципа работы. Это же относится и к другим узлам.

Полученное на выходе блока 9 приращение произведения переменных поступает на блок 8 умножения, на второй вход которого поступает сумма предыдущего значения функции и приращений переменных. Полученное произведение суммируется на сумматоре 5 с остатком предыдущих шагов интегрирования, поступающим из регистра 14, Результат квантуется в блоке 15 Приращение поступает на выход устройства а остаток квантования записывается в регистр 14.

Процесс протекает до тех пор, пока не выполняется неравенство X Х--у„ау. фиксируется на выходе схемы 11 сравнения на один вход которой поступает текущее значение координаты X из регистра 12, а на второй - со входа устройства. Сигна i выхода схемы 11 сравнения поступает на блок 9, и интегрирование заканчивается. Предлагаемое устройство позволяет существенно повысить точность вычисления кратных интегралов. Если методическая погрешность прототипа эквивалентна первому порядку малости Д , то в предлагаемом устройстве методическая погрешность эквивалентна втор ому порядку малости ( Д б ) т. е. точность решения в предлагаемом устройстве на порядок выше, чем в прототипе, а общий расход оборудования увеличивается незначительно. Формула изобретения Устройство для вычисления кратных интегралов, содержащее регистр текущего значения координаты X, вход которого соединен с первым входом устройства, а выход со входом схемы сравнения, другой вход ко торой подсоединен ко второму входу устро& ства, а выход - к первому входу блока формирования приращений произведения перемен ных, второй вход которого соединен с первым входом устройства, третий вход - с третьим входом устройства, первый выход блока формирования приращений произведени переменных соединен со входом регистра текущего значения координаты У, выход которого соединен с четвертым входом блока формирования приращений произведения переменных, пятый и шестой входы которого соединены соответственно с первым и вторым выходами блока вычисления приращений подынтегральной функции и максималь ного и минимального значений координаты У, первый и второй входы которого соедине ны соответственно с первым и вторым входами устройства, а третий и четвертый выходы блока вычисления приращений подынтегральной функции и максимального и минимального значений координаты У соедин& ны соответственно с первым и вторым вхоцами входного регистра выход которого соединен со входом первого сумматора, выход которого соединен со входом рагистра подынтегральной функции, выход которого соединен со входом первого сумматора, блок умножения, первый вход которого сойдннеи с выходом бпока формирования приращений произведения переменных, а вьгсод - с первым входом второго сумматора, выход которого соединен со входом блока выработки приращений, выход которого соединен с выходом устройства, второй вход второго сумматора соединен с выходом регистра остатка, вход которого соецинен с выходом второго сумматора, отличающееся тем, что, с целью повышения точности интегрирования кратных интегралез,, в него введены блок формирования дополнительного кода, третий сумматор и блок интегрирования граничной области, причеквход блока формирования дополнительного кода соединен с выходом входного регистра, а выход блока формирования дополнительно- го кода соединен с первым вxoдo третьего сумматора, второй вход которого соединен с выходом второго сумматора, а выход™ со вторым входом блока умножения, входы блока интегрирования граничной области соединены соответственно с третьим выходом блока формирования приращений произведения переменных, четвертым входом уст- ройства и третьим выходом блока вычисления приращений подынтегральной функции и максимального и минимального значений координаты У, а выход - с седьмым входом блока формирования приращений произведе ния переменных. Источники информации, принятые во внимание при экспертизе: 1.Авторское :видетепьстзо СССР № 317079 М.Кл. G 06 J 1/02, 30.1С,7С 2.Авторское свидетельство СССР № 487392 М.КлГ G 06 J 1/02 07.08.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления кратных интегралов | 1973 |

|

SU487392A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| Интегратор с воспроизведением вариаций интеграла | 1985 |

|

SU1335994A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

Авторы

Даты

1977-02-25—Публикация

1974-11-21—Подача