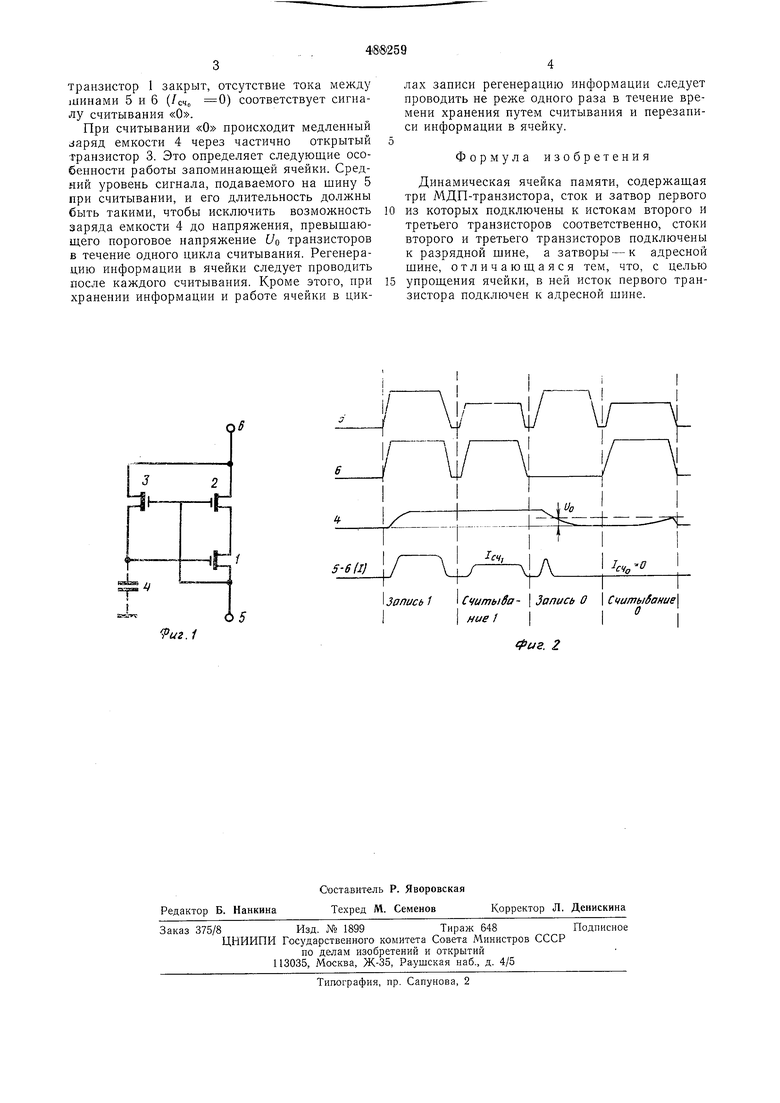

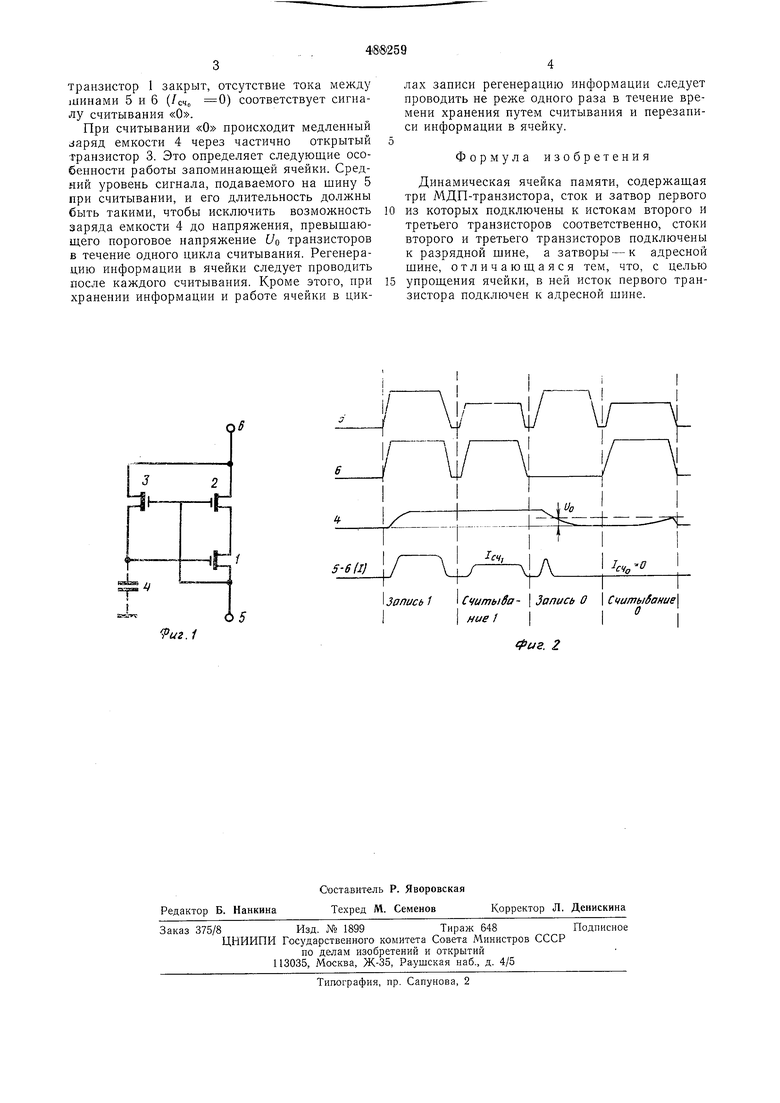

транзистор 1 закрыт, отсутствие тока между iUHHaMH 5 и 6 (/сч„ 0) соответствует сигналу считывания «О.

При считывании «О происходит медленный заряд емкости 4 через частично открытый транзистор 3. Это определяет следующие особенности работы запоминающей ячейки. Средний уровень сигнала, подаваемого на шину 5 при считывании, и его длительность должны быть такими, чтобы исключить возможность заряда емкости 4 до напряжения, превышающего пороговое напряжение t/o транзисторов в течение одного цикла считывания. Регенерацию информации в ячейки следует проводить после каждого считывания. Кроме этого, при хранении информации и работе ячейки в циклах записи регенерацию информации следует проводить не реже одного раза в течение времени хранения путем считывания и перезаписи информации в ячейку.

Формула изобретения

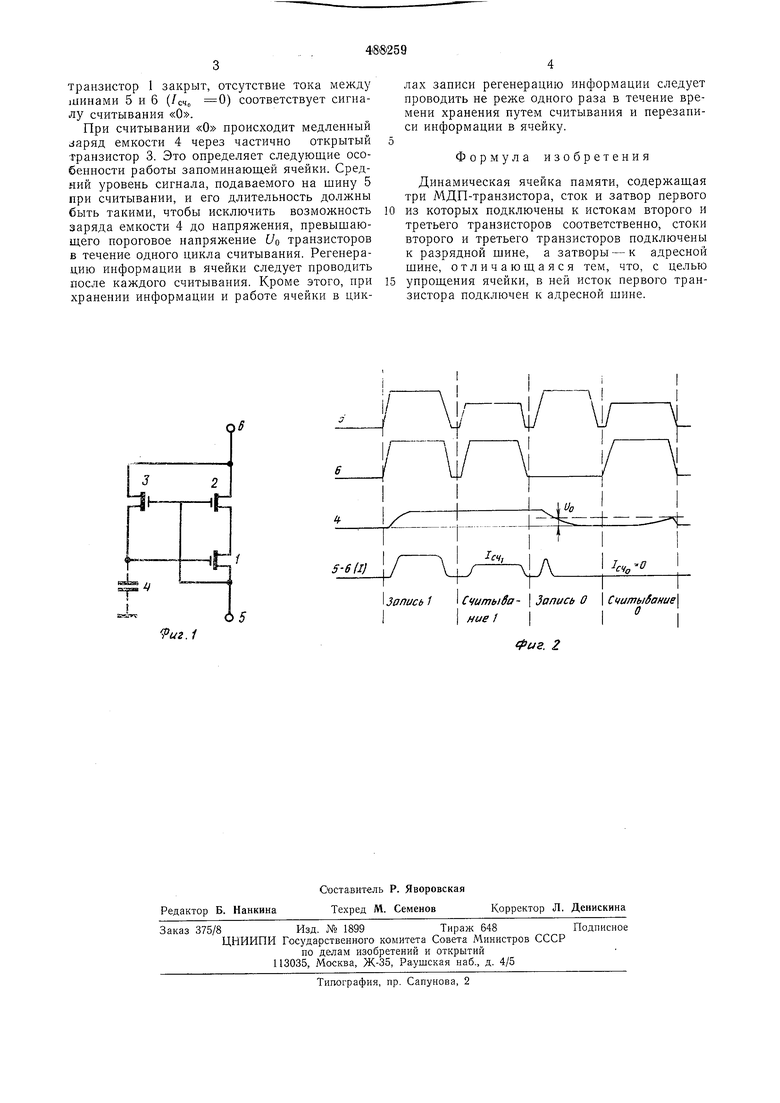

Динамическая ячейка памяти, содержащая три МДП-транзистора, сток и затвор первого

из которых подключены к истокам второго и третьего транзисторов соответственно, стоки второго и третьего транзисторов подключены к разрядной шине, а затворы -к адресной шине, отличающаяся тем, что, с целью

упрощения ячейки, в ней исток первого транзистора подключен к адресной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическая ячейка памяти | 1974 |

|

SU488258A1 |

| Динамическая ячейка памяти | 1974 |

|

SU529485A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

О

2

Ь5

иг.1

3anucb 1

Считыва- Запись О Считы5ание

нив

Фиг. 2

Авторы

Даты

1975-10-15—Публикация

1974-02-07—Подача