(54) ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ

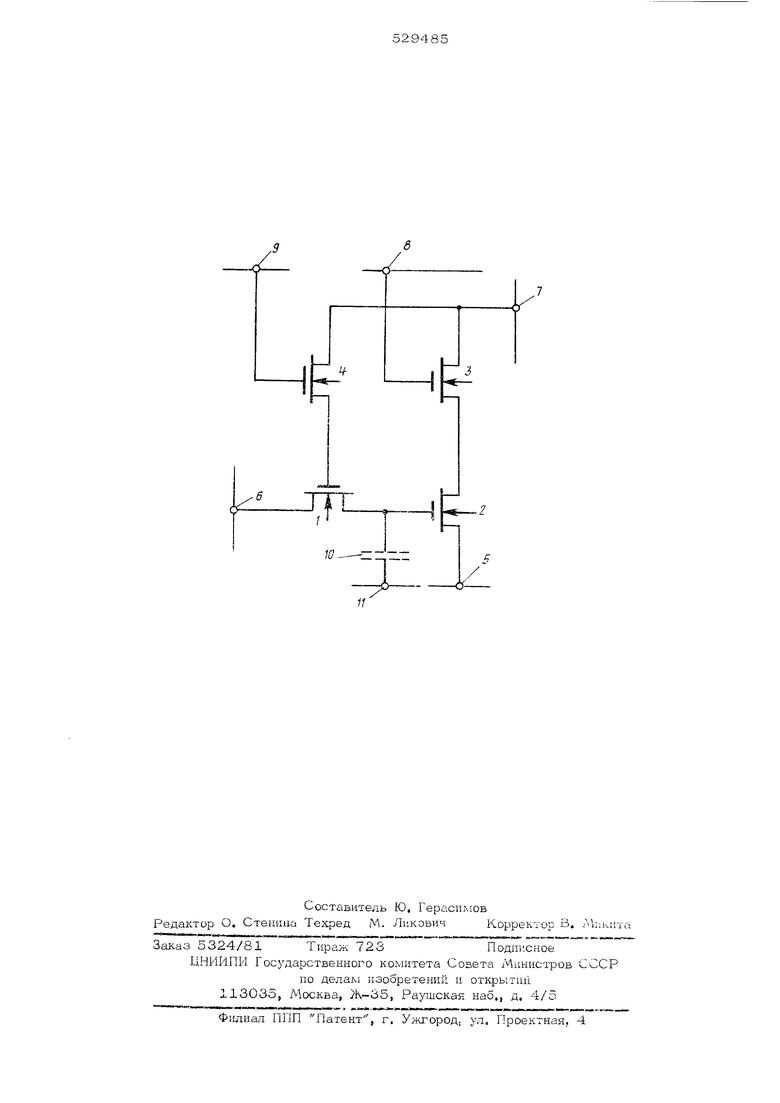

шину 9, запоминающий конденсатор 1О и полз проводниковую подлс)жку 11.

На подложку 11 подается либо нулевой потенциал, либо небольшое запирающее напряжение. Ячейка памяти может работать в режимах хранения, считывания, записи и. регенерации информации.

В режиме хранения на адресных шинах 8, 9 и на второй разрядной шине 7 напряжение соответствует логическому О на первой разрядной шине 6 - логической 1. Транзисторы 1, 3 и 4 закрыты. Транзистор 2 закрыт, если запоминающий конденсатор хранит логический О, и открыт, если хранит логическую 1.

В режиме считывания напряжения на первой адресной шине 8 повышается до логической 1 и третий транзистор 3 открывается. Вторая разрядная шина 7 заряжается

до уровня логической 1. Если ячейка памяти хранит 1, то разрядгшя шина 7 разряжается до уровня логического О через открытые транзисторы 2 и 3. Если ячейка хранит О то транзистор 2 закрьгт и на разрядной шине 7 сохраняется уровень логической 1.

В режиме записи уровень логической 1 подается на вторую адресную шину 9 и вгорукз разрядную шину 7, транзисторы 4 и 1 открыв.аются. Записываемая инфорхгяция подается иа первую разрядную шину 6 (логический О и л и 1).

После заряда или разряда запоминающего конденсатора 10 скачала понижается до логического О напряжение на второй разрядной шине 7 (чтобы транзистор 1 закрылся), а затем до логического О уменьшается напряжение на второй адресной шине 9. На первой адресной шине 8 в режиме записи напряжение соответствует логическому О,

Запоминающий конденсатор 10 со временем может разряжаться, поэтому требуется периодическая регенерация хранимой инфог мации.

Для регенерации информации иоследовательно выполняются две операции: считывание и записв.

В матрице памяти запоминающего устройства в режимах считывания и записи уровень логической 1 подается только на одну вторую разрядную шину 7, подключенную к выбранной ячейке, на остальных вторых разрядных шинах напряжение соответствует логическому О, В результате ток протекает только в одной ячейке, что yvieHbшает мощность, потребляемую запоминающим устройством.

Использование предлагаемой ячейки памяти позволяет на порядок уменьшить мощность, потребляемую матрицей памяти в интегральном запоминающем устройстве емкостью 1 кбит и более. Мощность, потребляемая динамическим запоминающих; устройством при обращении, во много раз превыщает мощность, потребляемую в режиме хранения. Поэтому уменьшение мощности, нотребляемой интегральным запоминающим устройством при обращении, позволяет уменьшить максимальную мощность, потребляемую модулем чапоминаюшего устройства.

обр

Ф о р м у л а

Динамическая ячейка памяти, содержащая МДП-траизисторы, исток первого из которых подключен к первой разрядной шине, а сток - к затвору второго транзистора, исток второго транзистора подключен к шине нулевого дЮтепциала, а сток - к истоку третьего транзистора, сток третьего транзистора подключен ко второй разрядной шине, а затаор - к первой адсесной шине, о т л и ч а ю ш а я с я тем, что, с целью уменьшения потребляемой ячейкой мощности, в ней исток четвертого транзистора подключен к затвору первого тракгзистора, сток ко второй разрядной шине, а затвор - ко второй адресной ujHHe.

Источ1 ики информации, принятые во внимание при экспертизе изобретения;

1.Патент США 3593037, кл. 307938, 1971.

2.Патент США 3585613, кл. 34О173, 1971.

3.Патент США N. 3685027, кл. 340.173, 1972.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическая ячейка памяти | 1974 |

|

SU488258A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

Авторы

Даты

1976-09-25—Публикация

1974-12-25—Подача