1

Изобретение относится к вычислительной технике и предназначено для построеиия сумматоров ЦВМ.

Известны логические ячейки, содержащие нагрузочный транзистор, затвором соединенный с -источником -смещения, истоком - с выходом ячейки и со стоками -первого и второго ключевых транзисторов, истоки которых соединены соответственно со стоками третьего и четвертого клк чевых транзисторов, истоками соединенных с шиной нулевого потенциала.

Цель изобретения - сокращение в логической ячейке площади подложки, количества компонентов и количества внещних выводов при обеспечении работы на общую магистраль, т. е. упрощение схемы.

Это достигается тем, что в предлагаемой ячейке между стоками третьего и четвертого ключевых транзисторов включен дополнительный ключевой транзистор, затвор третьего ключевого транзистора соединен с затвором второго ключевого транзистора, затворы первого, третьего, четвертого и дополнительного ключевых транзисторов соединены соответственно с четырьмя входами логической ячейки, подложки транзисторов соединены между собой и €О стробирующим входом логической ячейки.

За счет соединения внутри ячейки затворов двух транзисторов (в противоположных плечах моста) достигается сокращение числа ее выводов. Применение в ячейке мостикового включения МДП-транзистора, обеспечивающего в процессе функционирован-ия ячейки

протекание через него тока то в одном, то в противоположном направлении, позволяет увеличить функциональные возможности ячейки и сократить площадь кристалла полупроводника.

При наличии запрещающего потенциала на стробирующем входе ни один из транзисторов не -проводит и не шунтируется общая магистраль при объединении выходов нескольких элементов.

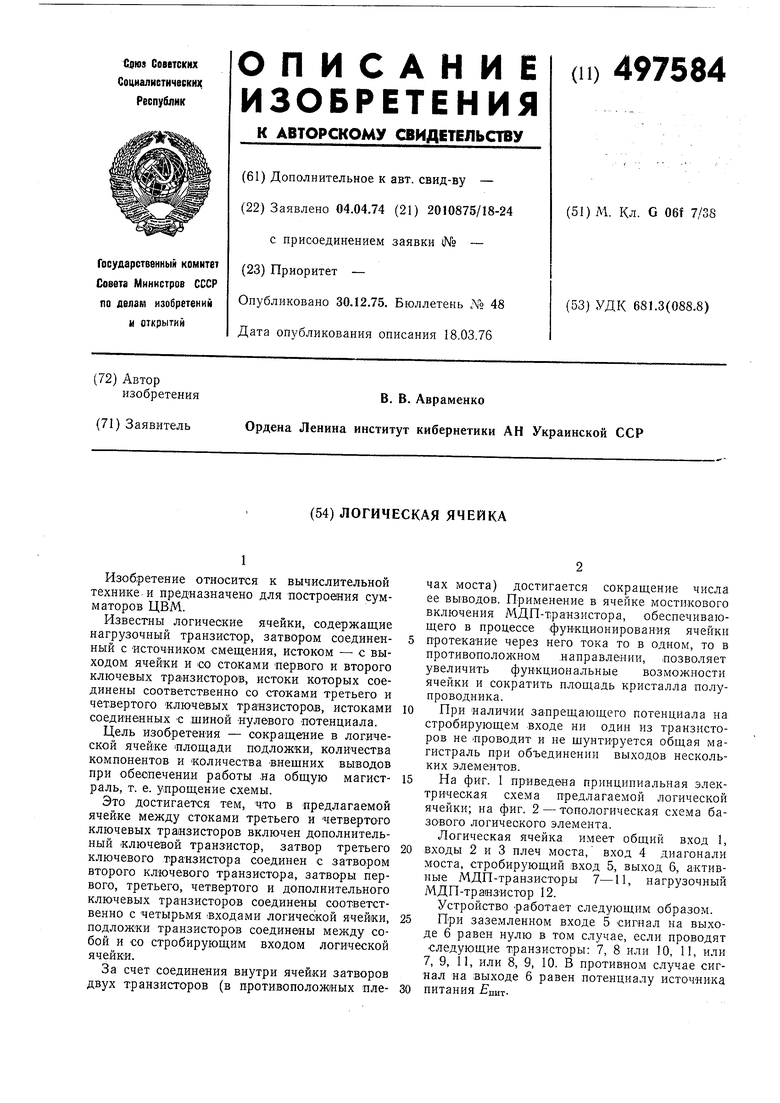

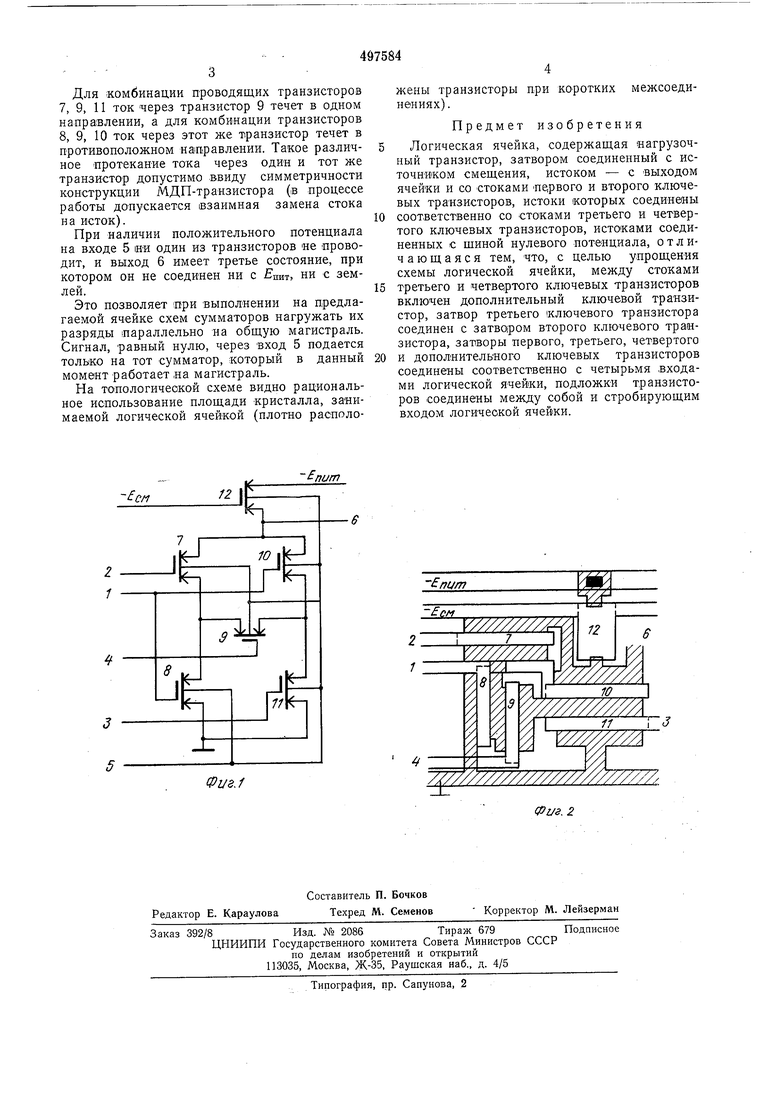

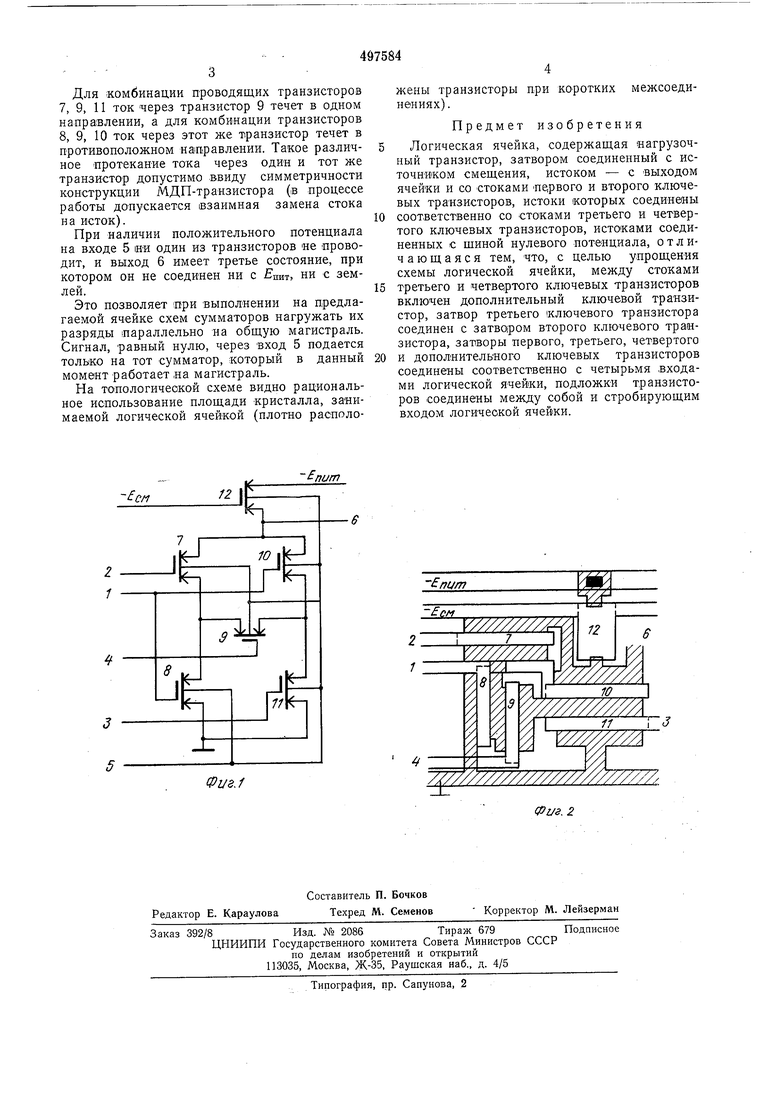

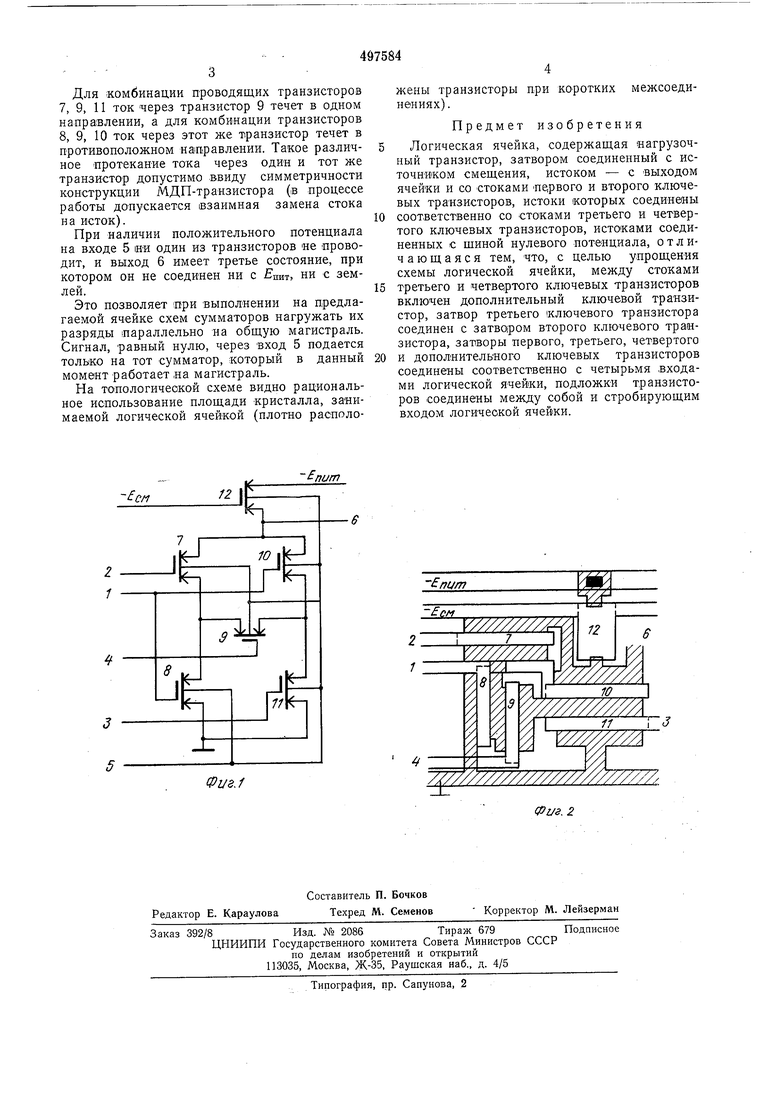

На фиг. 1 приведена принципиальная электрическая схема предлагаемой логической ячейки; на фиг. 2 - топологическая схема базового логического элемента. Логическая ячейка имеет общий вход 1,

входы 2 и 3 плеч моста, вход 4 диагонали моста, стробирующий вход 5, выход 6, активные МДП-транзисторы 7-II, нагрузочный МДП-траез-истор 12. Устройство работает следующим образом.

При заземленном входе 5 сигнал на выходе 6 равен нулю в том случае, если проводят следующие транзисторы: 7, 8 или 10, 11, или 7, 9, 11, или 8, 9, 10. В противном случае сигнал на выходе 6 равен потенциалу источника

питания пит.

Для комбинации проводящих транзисторов

7,9, 11 ток через транзистор 9 течет в одном направлении, а для комбинации транзисторов

8,9, 10 ток через этот же транзистор течет в противоположном наиравлении. Такое различное Протекание тока через один и тот же транзистор допустимо ввиду симметричности конструкции МДП-транзистора (в процессе работы допускается (взаимная замена стока на исток).

При наличии положительного потенциала на входе 5 ии один из транзисторов «е проводит, и выход 6 имеет третье состояние, при котором он не соединен ни с пит, ни с землей.

Это позволяет ири выполнении на предлагаемой ячейке схем сумматоров нагружать их разряды параллельно иа общую магистраль. Сигнал, равный нулю, через -вход 5 подается только на тот сумматор, который в данный момент работает на магистраль.

На топологической схеме видно рациональное использование площади кристалла, занимаемой логической ячейкой (плотно расположены транзисторы при коротких межсоединениях).

Предмет изобретения

Логическая ячейка, содержащая нагрузочный транзистор, затвором соединенный с источником смещения, истоком - с выходом ячейки и со стоками пе,рвого и второго ключевых транзисторов, истоки которых соединены

соответственно со стоками третьего и четвертого ключевых транзисторов, истоками соединенных с шиной нулевого потенциала, отличающаяся тем, что, с целью упрощения схемы логической ячейки, между стоками

третьего и четвертого ключевых транзисторов включен дополнительный ключевой транзистор, затвор третьего ключевого транзистора соединен с затво|ром второго ключевого транзистора, затворы первого, третьего, четвертого

и дополнительного ключевых транзисторов соединены соответственно с четырьмя входами логической ячейки, подложки транзисторов соединены между собой и стробирующим входом логической ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Параллельный асинхронный регистр на МДП-транзисторах | 1988 |

|

SU1615807A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

Фиг.1

пит

Авторы

Даты

1975-12-30—Публикация

1974-04-04—Подача