1

Изобретение относится к вычислительной: .технике, а именно к устройствам для обнаружения ошибок в сумматоре.

Контролируемый fl -разрядный сумматор, выход переноса каждого i -го -разряда которого соединен с входом переноса (l +1)го разряда, причем каждый I -и разряд содержит два полусумматора и элемент ИЛИ, входы первого, полусумматора соединены с шиндми соответствующих разрядов слагаемых,- выход суммы первого полусумматора соединен со входом суммы второго полусумматора, вход переноса которого соединен с выходом переноса элемента ИЛИ ( i -1)го разряда сумматора, выход переноса второго полусумматора соединен с первым входом элемента ИЛИ, ко второму входу которого подключен выход переноса первого полусумматора, элементы И и инверторы.

Однако для полного контроля известного контролируемого сумматора необходимо количество контрольного оборудования, равное количеству контролируемого оборудования.

Цель изобретения - уменьшение количества ко)гг|.о. оборудования.

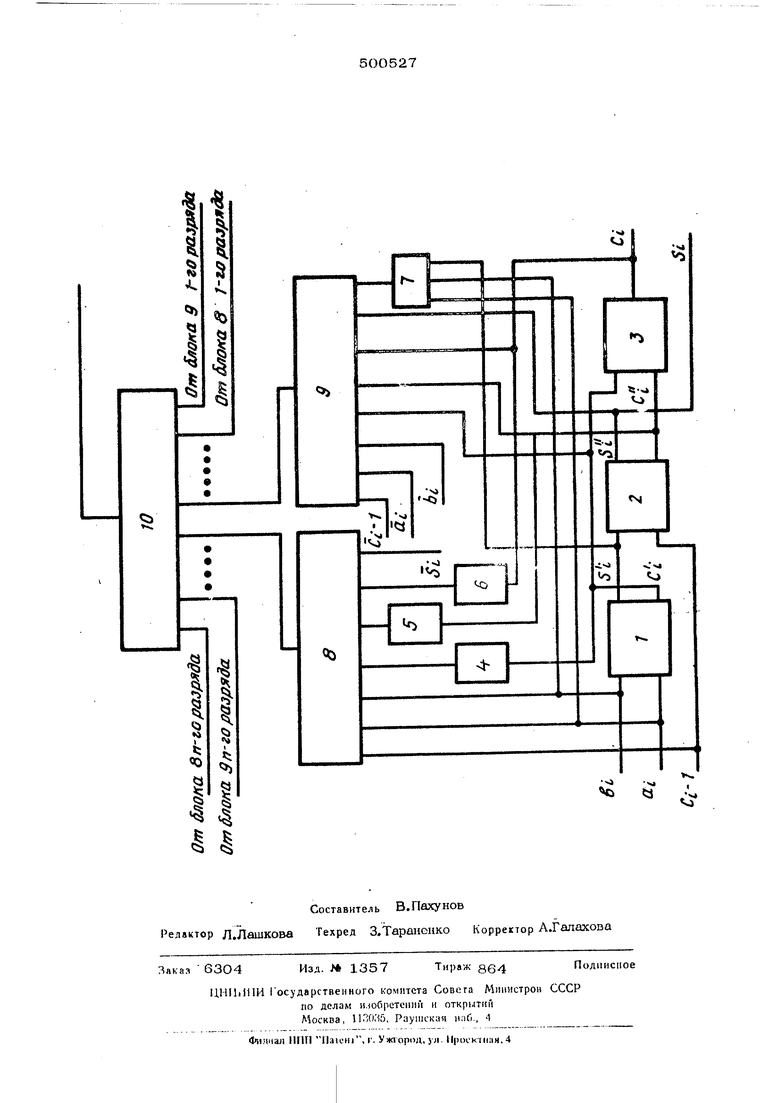

Это достигается тем, что в каждый I -К разряд введены семивходовой пороговый элемент с весами входов, равными 1 и порогом срабатывания, равным 5, входы которого соединены соответственно с вы|ХодЬМ переноса ( i -1)-го разряда, со входами слагаемых данного разряда и через инверторы с выходами переносов первс го и второго полусумматоров,с выходом переноса элемента ИЛИ и с выходом суммы второго полусумматора, восьмивходовой пороговый элеменс весами входов, равными 1Ти порогом срабатывания, равным 4Тпервый-пятый входы которого соединены соответственно с выходами переносов первого и второго полусумматоров, с выходом суммы второго полусумматора, с выходом элемента И, входы которого соединены со входами слагаемых данного разряда и с выходом суммы первого полусумматора, а шестой-восьмой входы соединены соответственно с выходом Обратного кода переноса ( i -1)-го разря да iT с входами обратного кода ела- гаемых данного разряда, причем вы,ходы пороговых элементов всех раз- рядов соединены с лвходами многовлю.дового апемента ИЛИ.. Устройство схематически приведено на HeptSKe, Контролируемый П -разрядный сумматор в каждом разряде содержит два полусумматора 3, и 2 и элемент ИЛИ 3, входы первого полусумматора 1 соединены с шинами соответствующих разрядов слагаемых 0-1 , i)l выход суммы 5; первого полусумматора 1 соединен с вхо, ДРМ ..суммы второго полусу1|)Шатора 2, вход переноса которого соединен с выходом переноса элемента ИЛИ 3 соседнего разря да сумматора. Выход переноса второго полусумматора 2 соединен с первым входо /элемента ИЛИ 3, ко второму входу которо подключен выход переноса первого полусум тора 1. Кроме того, каждый разряд сумматора содержит инверторы 4, 5, 6, элемент И 7 семивходовой пороговый элемент 8 с весами входов, равными 1 и порогом срабатывания, равным 5, входы которого соединены соответственно с выходом переноса соседнего разряда, со входами слагаемых 0 , 6 данного разряда, через инверторы 4, 5, 6 с выходами переносов С полусумма тороБ 1, 2 с выходом переноса С элемента ИЛИ 3 и с выходом суммы S( полусумматора 2. Входы восьмивходового порогового элемента 9 с весами входов, равными 1, и порогом фабатывания, равным 4, соединены соответствен но с выходами переносов С. , С/пЪлуIIIсумматоров 1, 2 с выходом суммы S: , полусумматора 2, с выходом элемента И 7 входы которого соединены со входами слагаемых и , 6 данного разряда и с выходом суммы S полусумматора 1, остальные входы порогового элемента 9 соединены соответственно с выходом обратного кода переноса элемента ИЛИ 3 соседнего разряда и с обратными кодами слагаемых и I bf данного разряда, причем выходы пороговых элементов 8, 9 всех разрядов соединены со входами многовходового элеме нта ИЛИ 1О. Устройство работает следующим образом Входы пороговых элементов 8 и 9 под-. ключеиы так, что при появлении ошибочного сигнала на вуутренних I шинах С, . , а сумматора или на его выходах Si CL сумма входных сигналов одного из пороговых элементов превышает его П0рог,т,е величняу 5 для элемента В if величину для злемента 9, в результате чего на выходе одного из пороговых появится сигнал ошибки. Для npHMCfia paccMmpHwiPTcji работа .cyMMOTOiia на входном lUiGoiio С О, (J, 1 Ь; 1 при неисправном полусумматоре 1. При правильной работе полусумматора 1 на шине . будет сигнал,соответствукяций О, на шине С 1. При ошибочном появлении на шине S сигнала входной набор кодов, подаваемых на входы порогового элемента 9,будет иметь вид 10О10111. Сумма входных кодов равна 5, что прей|1шает порог срабатывания порогового элемента 9 и на выходе иброгового элемента 9 появится ситная оййбки. П|рй появлении на шине С сигнала О вместо I срабатывает пороговый элемент 8. При одновременной неправильной работе и схемы формирования суммы, и схемы формирования переноса срабатывает пороговый элемент 8, В сум1 зторе обнаруживаются все одиночные ошибки, а также большинство двойных ошибок в одном из полусумматоров кроме одной, а именно навхо дном наборе С -1, и 1, fc; 1 лри неисправности полусумматора 2, заключак щейся в том, что $ 0, а О. Числологических уровней, через которые йроходит сигнал от входа к выходу в схеме контроля .предлагаемого сумматора равно 3 (инвертор - ПЭ - схема ИЛИ). Ф о р м j л а., и 3 9 б р е т 8 н и я Контролир5г.емый П -разрядный сумматор, выход переноса каждого i -го разряда которого соединен со входом переноса ( i +1)го разряда, причем каждый ( -и разряд содержит два полусумматора и элемент ИЛИ, входы первого полусумматора соединены с шинами соответствующих разрядов слагаемых, выход суммы первого полусумматора соединен со входом цуммы второго полусумматора, вход переноса которого соединен с выходом переноса элемента ИЛИ ( / -1)-го разряда сумматора, выход переноса второго полусумматора соединен с первым входом элемента ИЛИ, ко второму входу которого подключен выход переноса первого полусумматора, элементы И, инверторы, отличающийся тем, что, с целью уменьшения количества контрольного оборудования, а каждый I-tt разряд введенысемивходовой пороговый элемент с весами входов, равнь - ми 1 и порогом срабатывания, равным 5 входы которого соединены соответственно с выходом переноса ( 1 -1)-го разряда, со входами слагаемых данного разряда и через инверторы с выходами переносов первого и .второго полусумматоров, с выходом переноса элемента ИЛИ и с выходом суммы второго полусумматора, восьмипходовой пороговый элемент с весами входов, равными и порогом срабатывания, равным 4 первый-пятый входы когорого соеди|{еиы соотретственно с выходами переносов первого я второго полусумматоров, с выходом суммы второго полусумматора, с выходом элемента И, входы которого Соединены с входами елагаемых данного разряда и с выходом, суммы первого полусумматора, шестой-восьмой вхо6ы соединены соответственно с оыхоаом к ратного кода переноса ( I -1)-го разряде со входами обратного кода слагаемых данного разряда, причем .(хоиы поротных § элементов всех разрядоп сое.«и.;ены со входаги И многовходового элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычитающее у тройство с контролем | 1977 |

|

SU690481A1 |

| Контролируемый сумматор | 1978 |

|

SU811261A1 |

| Вычитающее устройство с контролем | 1978 |

|

SU807274A1 |

| Контролируемый двоично-десятичныйСуММАТОР | 1979 |

|

SU845156A1 |

| Сумматор с контролем | 1979 |

|

SU788108A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Двоичный счетчик импульсов с контролем ошибок | 1976 |

|

SU610306A1 |

| Обратимый п-разрядный сумматор | 1979 |

|

SU824204A1 |

Авторы

Даты

1976-01-25—Публикация

1973-10-15—Подача