Сумматора соединен с выходом переноса предыдущего разряда контролируемого сумматора н с входом первого порогового элемента, имеющим вес +1, два другпх входа первого порогового элемента, имеющего вес +1, соединены с входами соответствующих разрядов операндов, выход суммы одноразрядного сумматора каждого разряда контролируемого сумматора соединен с входом второго порогового элемента соответствующего разряда, имеющим -fl, выход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса из данного разряда, пороговые элементы имеют порог срабатывания +1, причем в каждом разряде контролируемого сумматора вход первого порогового элемента, имеющий вход с весом -1, соединен с выходом суммы соответствующего одноразрядного сумматора, выход переноса которого соединен с входом первого порогового элемента, имеющим вес -2, и с входом второго порогового элемента, имеющим вес +2, три входа второго порогового элемента, имеющие вес -1, соединены соответственно с выходом переноса предыдущего разряда контролируемого сумматора и с входами соответствующих разрядов операндов.

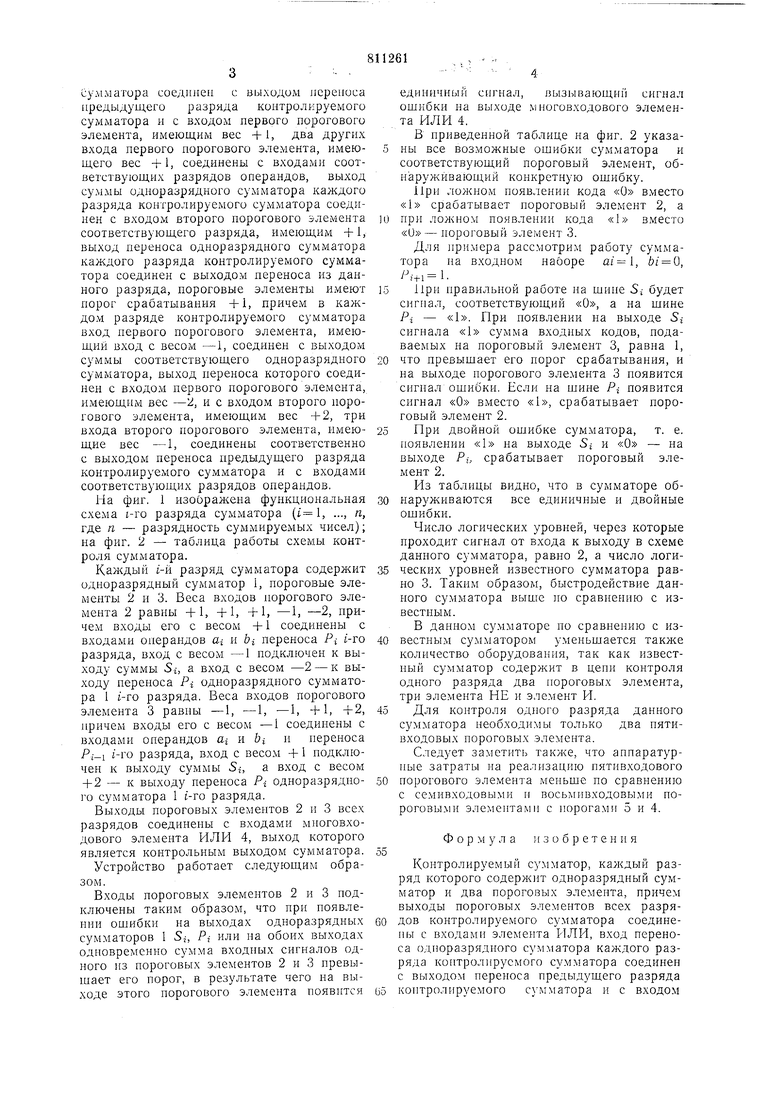

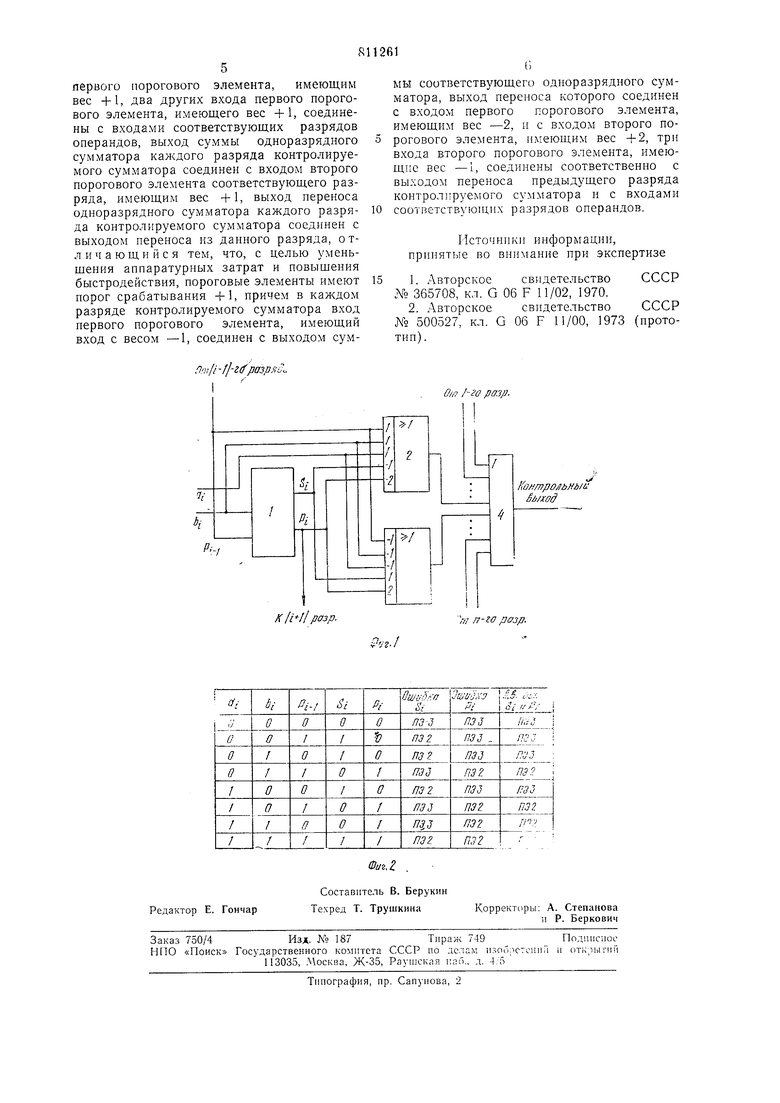

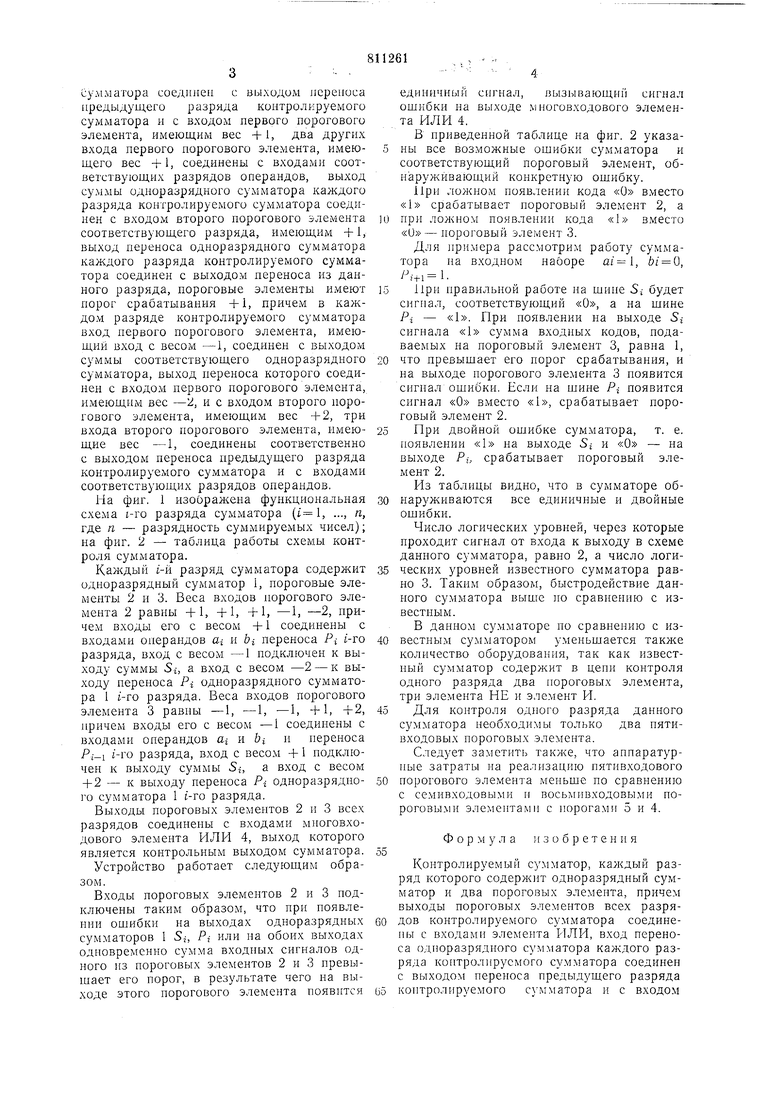

На фиг. 1 изображена функциональная схема :-го разряда сумматора (, ..., п, где п - разрядность суммируемых чисел); на фиг. 2 - таблица работы схемы контроля сумматора.

Каждый t-й разряд сумматора содержит одноразрядный сумматор 1, пороговые элементы 2 и 3. Веса входов порогового элемента 2 равны -М, -f 1, +1, -1, -2, нричем входы его с весом +1 соединены с входами операндов a-i и bi переноса Pi t-ro разряда, вход с весом -1 подключен к выходу суммы Si, а вход с весом -2 - к выходу переноса Pi одноразрядного сумматора 1 t-ro разряда. Веса входов порогового элемента 3 равны -1, -1, -1, +1, -f2, причем входы его с весом -1 соединены с входами операндов Ct и bi и переноса t-ro разряда, вход с весом +1 подключен к выходу суммы Si, а вход с весом 4-2 - к выходу переноса Pi одноразрядного сумматора 1 t-ro разряда.

Выходы пороговых элементов 2 и 3 всех разрядов соединены с входами многовходового элемента ИЛИ 4, выход которого является контрольным выходом сумматора.

Устройство работает следующим образом.

Входы пороговых элементов 2 и 3 подключены таким образом, что при появлении ошибки на выходах одноразрядных сумматоров 1 Si, Pi или на обоих выходах одновременно сумма входных сигналов одного из пороговых элементов 2 и 3 превышает его порог, в результате чего на выходе этого порогового элемента появится

единичный сигнал, вызывающий сигнал ошибки на выходе многовходового элемента ИЛИ 4.

В приведенной таблице на фиг. 2 указаны все возможные ощибки сумматора и соответствующий пороговый элемент, обнаруживающий конкретную ощибку.

11ри ложном появлении кода «О вместо «1 срабатывает пороговый элемент 2, а

при ложном появлении кода «1 вместо «и -пороговый элемент 3.

Для примера рассмотрим работу сумматора на входном наборе , Ы 0, .

При правильной работе на щипе Si будет сигнал, соответствующий «О, а на шине Pi - «1. Ири появлении на выходе Si сигнала «1 сумма входных кодов, подаваемых на пороговый элемент 3, равна 1,

что превышает его порог срабатывания, и на выходе порогового элемента 3 появится сигнал ошибки. Если на шине Pj появится сигнал «О вместо «1, срабатывает пороговый элемент 2.

При двойной ошибке сумматора, т. е. появлении «1 на выходе Si и «О - на выходе Pi, срабатывает пороговый элемент 2.

Из таблицы видно, что в сумматоре обпаруживаются все единичные и двойные ошибки.

Число логических уровней, через которые проходит сигнал от входа к выходу в схеме данного сумматора, равно 2, а число логических уровней известного сумматора равно 3. Таким образом, быстродействие данного сумматора выше по сравнению с известным. В данном сумматоре по сравнению с известным сумматором уменьшается также количество оборудования, так как известный сумматор содержит в цепи контроля одного разряда два пороговых элемента, три элемента ИЕ и элемент И.

Для контроля одного разряда данного сумматора необходимы только два пятивходовых пороговых элемента.

Следует заметить также, что аппаратурные затраты на реализацию пятивходового

порогового элемента меньше по сравнению с семивходовыми и восьмивходовыми пороговыми элементами с порогами 5 и 4.

Формула изобретения

Контролируемый сумматор, каждый разряд которого содержит одноразрядный сумматор и два пороговых элемента, причем выходы пороговых элементов всех разрядов контролируемого сумматора соединены с входами элемента ИЛИ, вход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса предыдущего разряда

контролируемого сумматора и с входом

первого порогового элемента, имеющим вес +1, два других входа первого порогового элемента, имеющего вес +1, соединены с входами соответствующих разрядов операндов, выход суммы одноразрядного сумматора каждого разряда контролируемого сумматора соединен с входом второго порогового элемента соответствующего разряда, имеющим вес 4-1, выход переноса одноразрядного сумматора каждого разряда контролируемого сумматора соединен с выходом переноса из данного разряда, отличающийся тем, что, с целью уменьшения аппаратурных затрат и повышения быстродействия, пороговые элементы имеют порог срабатывания +1, причем в каждом разряде контролируемого сумматора вход первого порогового элемента, имеющий вход с весом -I, соединен с выходом сум l:jili-{l-Z(fpa3p S

мы соответствующего одноразрядного сумматора, выход переноса которого соединен с входом первого порогового элемента, имеющим вес -2, и с входом второго порогового элемента, имеющим вес +2, три входа второго порогового элемента, имеющие вес -1, соединены соответственно с выходом переноса предыдущего разряда контролируемого сумматора и с входами

соответствующих разрядов операндов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 365708, кл. G 06 F 11/02, 1970.

2. Авторское свидетельство СССР № 500527, кл. G 06 F 11/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор с контролем | 1979 |

|

SU788108A1 |

| Контролируемый двоично-десятичныйСуММАТОР | 1979 |

|

SU845156A1 |

| Вычитающее у тройство с контролем | 1977 |

|

SU690481A1 |

| Устройство для выделения экстремальных чисел | 1983 |

|

SU1109736A2 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Контролируемый п-разрядный сумматор | 1973 |

|

SU500527A1 |

| Комбинационный сумматор | 1986 |

|

SU1327092A1 |

| Вычитающее устройство с контролем | 1978 |

|

SU807274A1 |

| Сумматор по модулю три | 1991 |

|

SU1797109A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

К разр.

П-tO pcf3fl.

Авторы

Даты

1981-03-07—Публикация

1978-07-12—Подача