1

Изобретение относится к вычислительной технике и может быть использовано при построении ЦВМ повышенной надежности.

Известны вычитающие устройства, контроль которых осуществляется схемами Нечетность / f и 2 .

Недостатком указанных устройств является невозможность обнаружения многократных ошибок и большие аппаратурные затраты.

Наиболее близким по технической сущности к предлагаемому является вычитающее устройство с контролем, каждый разряд которого содержит два полусумматора - вычитателя, элемент ИЛИ, объединяющий выходы заемов полусумматоров - вычигателей, элементы И и НЕ и два пороговых элемента (ПЭ) подключенных к прямым и инверсным выходам и входам полусумматоров - вычитателей и элемента ИЛИ. Выходы ПЭ-ов всех разрядов подключены через многовходовой элемент ИЛИ к шине ошибки вычитающего устройства.

При правильной работе сумма входов каждого ПЭ равна определенному числу, меньше порога срабатывания ПЭ-ов. При неправильной работе сумма входов одного из Пэ-ов, с учетом весов его входов, становится равной, либо превышает порог срабатывания даного ПЭ, и на контрольном выходе появляетвя сигнал ошибки pj .

Однако недостатком известного вычитающего устройства с контролем являются значительные аппаратурные затраты, а также невысокое быстродействие, так как схема контроля в нем выполнена с использованием многоуровневой логики.

Цель изобретения - уменьшение аппаратурных затрат.

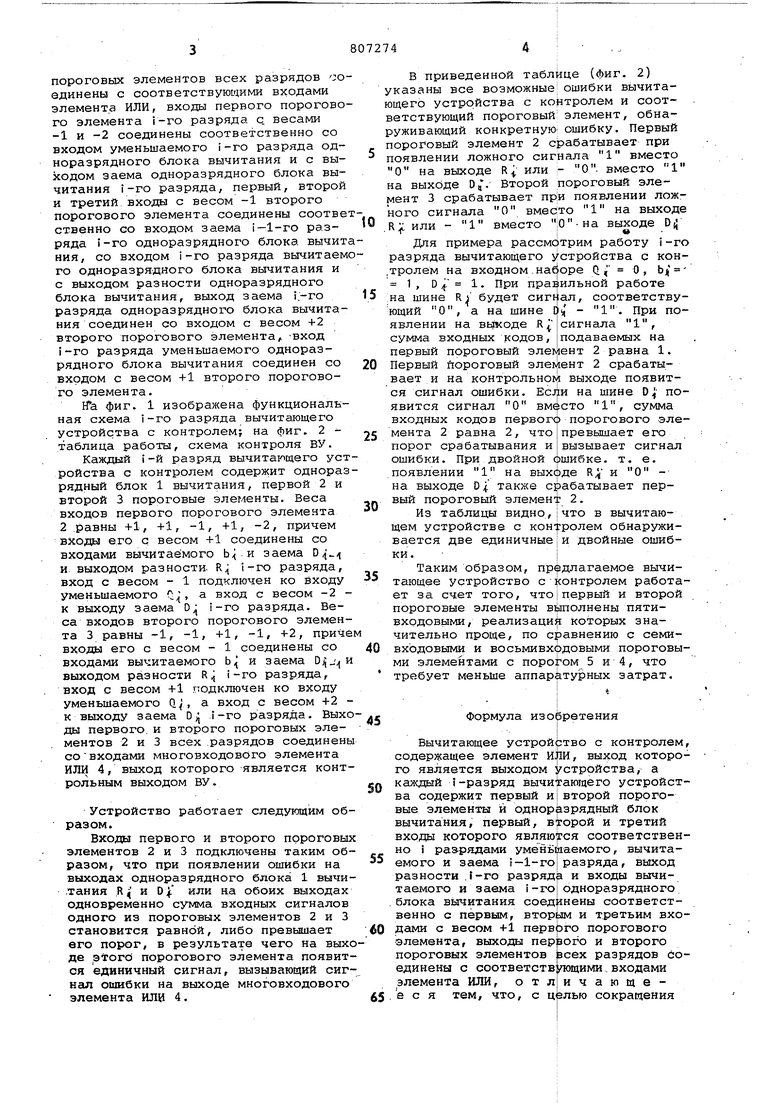

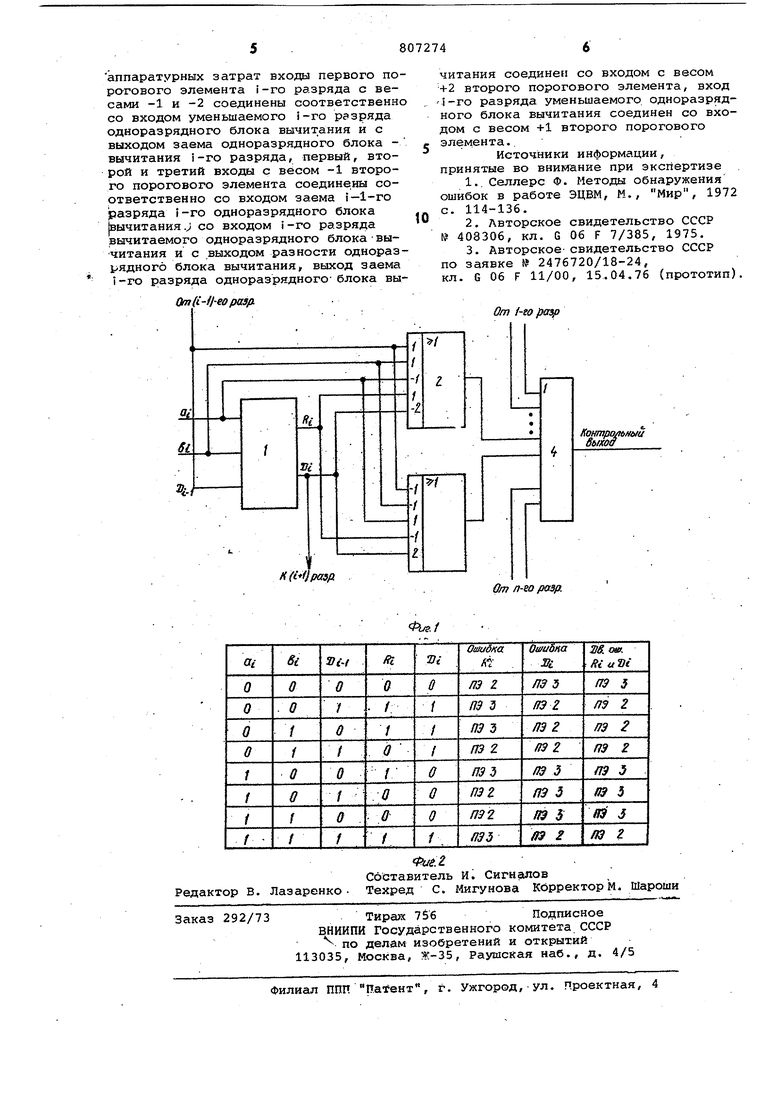

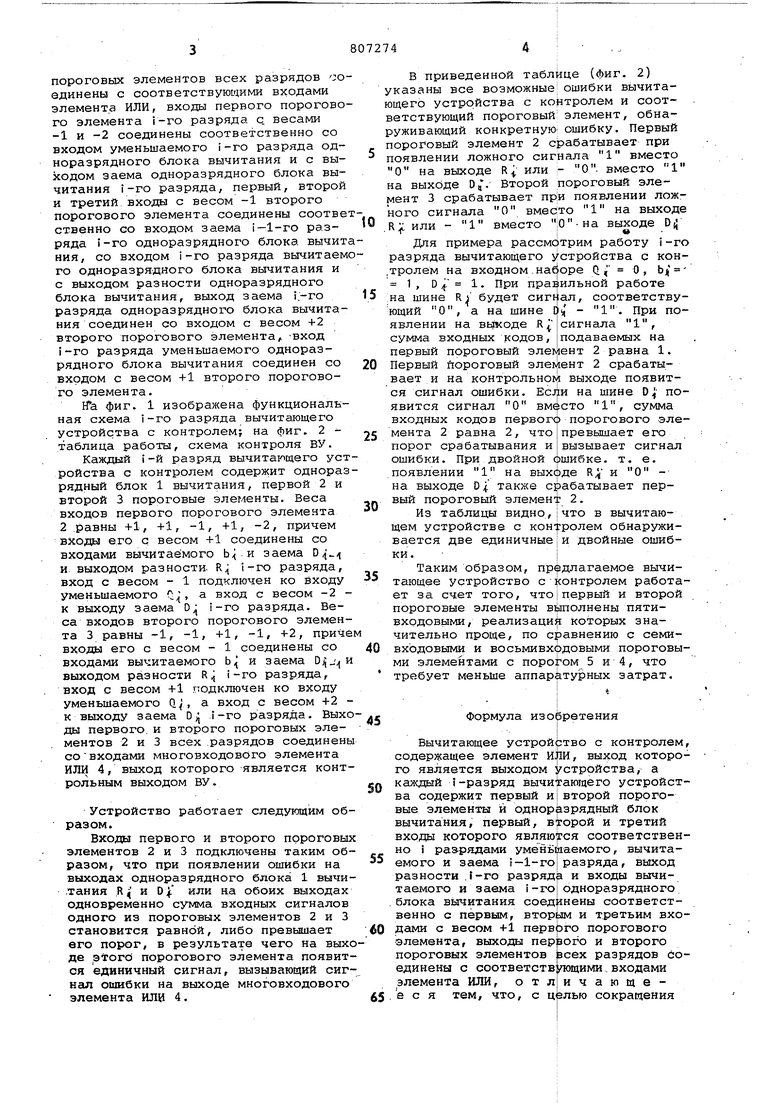

Поставленная цель достигается тем что в вычитающее устройство с контролем, содержащее элемент ИЛИ, выход которого является выходом устройства, а каж.цый i -разряд вычитающего устройства содержит первый и второй пороговые элементы и одноразрядный блок вычитания, первый, второй и третий входы которого являются соответственно i разрядами уменьшаемого, вычитаемого и заема f-1-го разряда, выход разности i-го разряда и входы вычитаемого и заема 1-го одноразрядного блока вычитания соединены соответственно с первым, вторым и третьим входами с весом +1 первого порогового элемента, выходы первого и второго пороговых элементов всех разрядов со единены с соответствующими входами элемента ИЛИ, входы первого порогово го элемента i-ro разряда с, весами -1 и -2 соединены соответственно со входом уменьшаемого i-ro разряда одноразрядного блока вычитания и с выходом заема одноразрядного блока вычитания i-ro разряда, первый, второй и третий входы с весом -1 второго порогового элемента соединены соотве ственно GO входом заема i-1-го разряда i-ro одноразрядного блока вычит ния, со входом I-го разряда вычитаем го одноразрядного блока вычитания и с выходом разности одноразрядного блока вычитания, выход заема 1.-го разряда одноразрядного блока вычитания соединен со входом с весом +2 второго порогового элементад Вход i-ro разряда уменьшаемого одноразрядного блока вычитания соединен со входом с весом +1 второго порогового элемента. ffa фиг. 1 изображена функциональная схема i-ro разряда вычитающего устройства с контролем; на фиг. 2 таблица работы, схема контроля ВУ. Каждый i-и разряд вычитающего уст ройства с контролем содержит однораз рядный блок 1 вычитания, первой 2 и второй 3 пороговые элементы. Веса входов первого порогового элемента 2 равны +1, +1, -1, +1, -2, причем входы его с весом +1 соединены со входами вычитаемого Ь и заема D и выходом разности- R i-ro разряда, вход с весом - 1 подключен ко входу уменьшаемого Г, а вход с весом -2 к выходу заема D i-ro разряда. Веса входов второго порогового элемента 3 равны -1, -1, +1, -1, н-2, приче входцл его с весом - 1 соединены со входами вычитаемого Ь и заема выходом разности R i-ro разряда, вход с весом +1 подключен ко входу уменьшаемого Q|, а вход с весом +2 к выходу заема Г ; i-ro разряда. Выхо ды первого, и второго пороговых элементов 2 и 3 всех разрядов соединены совходами многовходового элемента ИЛИ 4, выход которого является контрольным выходом ВУ. Устройство работает следующим об разом. Входы первого и второго пороговых элементов 2 и 3 подключены таким об разом, что при появлении ошибки на выходах одноразрядного блока 1 вычи .тания и или на обоих выходах одновременно сумма входных сигналов одного из пороговых элементов 2 и 3 становится равной, либо превышает его порог, в результате чего на вых де зтого порогового элемента появит ся единичный сигнал, вызывающий сиг нал ошибки на выходе многовходового элемента ИЛИ 4. в приведенной таблице (фиг. 2) казаны все возможные; ошибки вычитащего устройства с контролем и соотетствующий пороговый элемент, обнауживающий конкретную: ошибку. Первый ороговый элемент 2 срабатывает при оявлении ложного сигнала 1 вместо О на выходе R или - О, вместо 1 на выходе О,. Второй пороговый элеент 3 срабатывает пр:и появлении ложного сигнала О вместо 1 на выходе R;; или - 1 вместо выходе DIJ Для примера рассмотрим работу i-го разряда вычитающего устройства с контролем на входном .наборе Q, О, bf 1 , D 1. При правильной работе на шине R| будет , соответствующий О, а на шине 0 - 1. При появлении на вьжоде сигнала 1, сумма входных кодов, подаваемых на первый пороговый элемент 2 равна 1. Первый пороговый элемент 2 срабатывает и на контрольном выходе появится сигнал ошибки. Если на шине 0| появится сигнал О вместо 1, сумма входных кодов первогф порогового элемента 2 равна 2, что превышает его порог срабатывания и вызывает сигнал ошибки. При двойной ошибке, т. е. появлении 1 на выходе и О на выходе D j также срабатывает первый пороговый элеменф 2. Из таблицы видно,I что в вычитающем устройстве с кон|сролем обнаруживается две единичные I и двойные ошибки. I Таким образом, прфдлагаемое вычитающее устройство с контролем работает за счет того, что|первый и второй пороговые элементы выполнены пятивходовыми, реализаций которых значительно проще, по сравнению с семивходовыми и восьмивх довыми пороговыми элементами с nopoiroM 5 и 4, что требует Меньше аппаратурных затрат. Формула изобретения Вычитающее устройство с контролем, содержащее элемент ИЛИ, которого является выходом устройства, а Кс1жде;1й -разряд вычи- ающего устройства содержит первый и|второй пороговые элементы и одноразрядный блок вычитания, первый, в горой и третий входы которого явля1о|гся соответственно I разрядами уменьшаемого, вычитаемого и заема i-1-го разряда, выход разности 1-го разряда и входы вычитаемого и заема i-ro одноразрядного блока вБГЧитания соединены соответственно с первым, BTopiJM и третьим входами с весом +1 первого порогового элемента, выходы перзого и второго пороговых элементов всех разрядов йоединены с соответствующими,входами элемента ИЛИ, отличающееся тем, что, с ЦЭлью сокращения

аппаратурных затрат входы первого порогового элемента i-ro разряда с весами -1 и -2 соединены соответственно со входом уменьшаемого i-ro разряда одноразрядного блока вычитания и с выходом заема одноразрядного блока вычитания i-ro разряда, первый, второй и третий входы с весом -1 второго порогового элемента соедине.ны соответственно со входом заема i-1-го разряда i-го одноразрядного блока вычитания J со входом i -го разряда вычитаемого одноразрядного блока вычитания и с выходом разности одноразрядного блока вычитания, выход заема i-ro разряда одноразрядного блока выOm(i-fHopot3/i

читания соединен со входом с весом Ч2 второго порогового элемента, вход i-ro разряда уменьшаемого одноразрядного блока вычитания соединен со входом с весом +1 второго порогового элемента..

Источники информации, принятые во внимание при экспертизе 1.. Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ, М., Мир, 1972 с. 114-136.

0

2.Авторское свидетельство СССР 408306, кл. G 06 F 7/385, 1975.

3.Авторское-свидетельство СССР по заявке № 2476720/18-24,

кл. 6 06 F 11/00, 15.04.76 (прототип).

От f-го разр

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор с контролем | 1979 |

|

SU788108A1 |

| Вычитающее у тройство с контролем | 1977 |

|

SU690481A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Контролируемый сумматор | 1978 |

|

SU811261A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Контролируемый п-разрядный сумматор | 1973 |

|

SU500527A1 |

| Устройство для параллельного алгебраического сложения в знакоразрядной системе счисления | 1981 |

|

SU1003074A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

t.

Л

ц..

K()pasp.

Контрольный выход

От ft-so рвэр.

Авторы

Даты

1981-02-23—Публикация

1978-09-26—Подача