(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970478A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1418816A1 |

| Устройство для исправления ошибок в блоках памяти | 1979 |

|

SU868842A1 |

| Запоминающее устройство матрич-НОгО ТипА C САМОКОНТРОлЕМ | 1979 |

|

SU841063A1 |

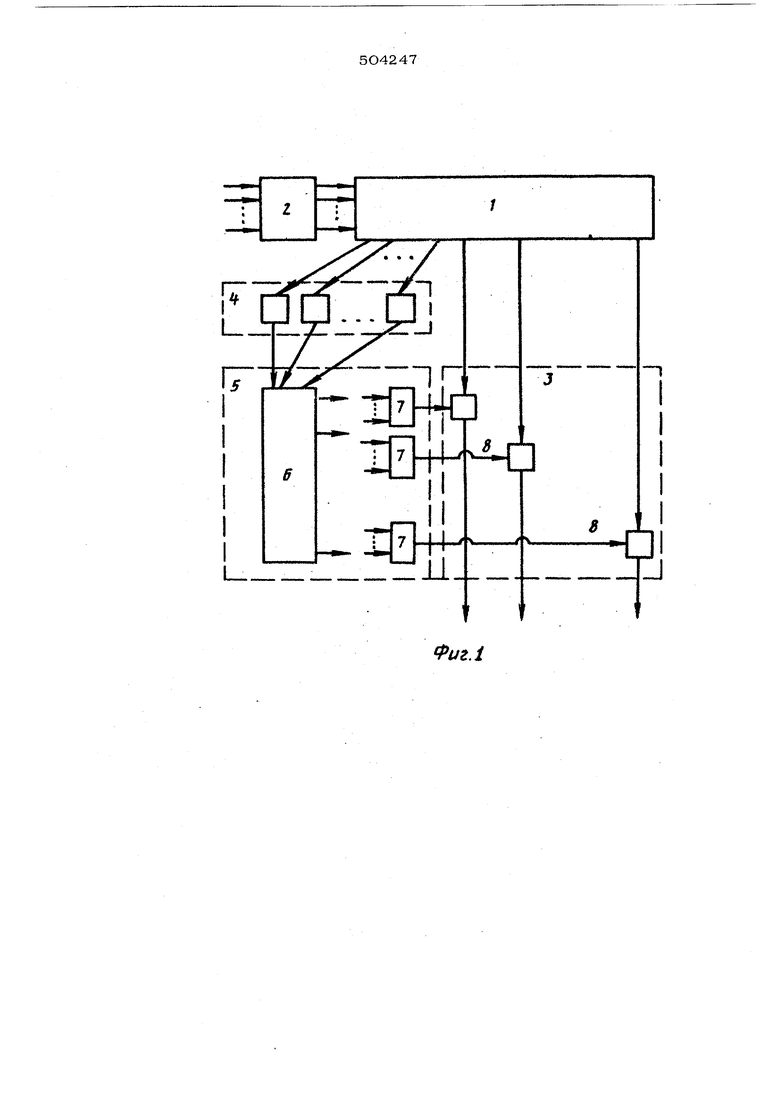

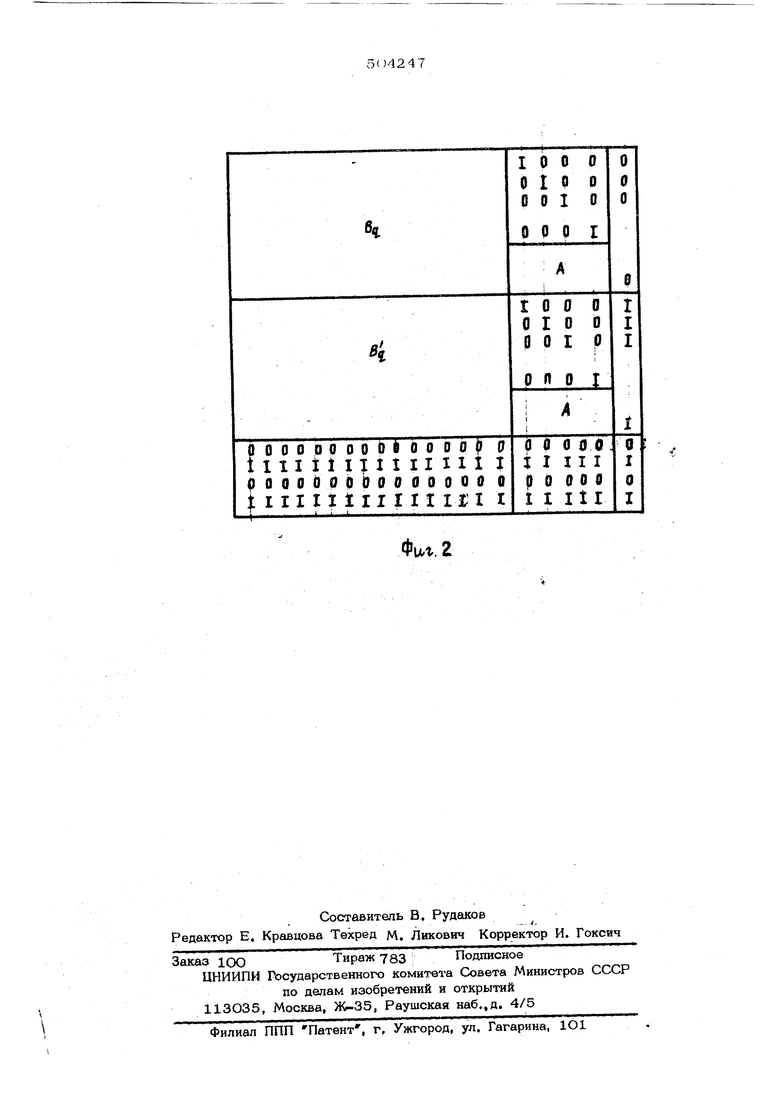

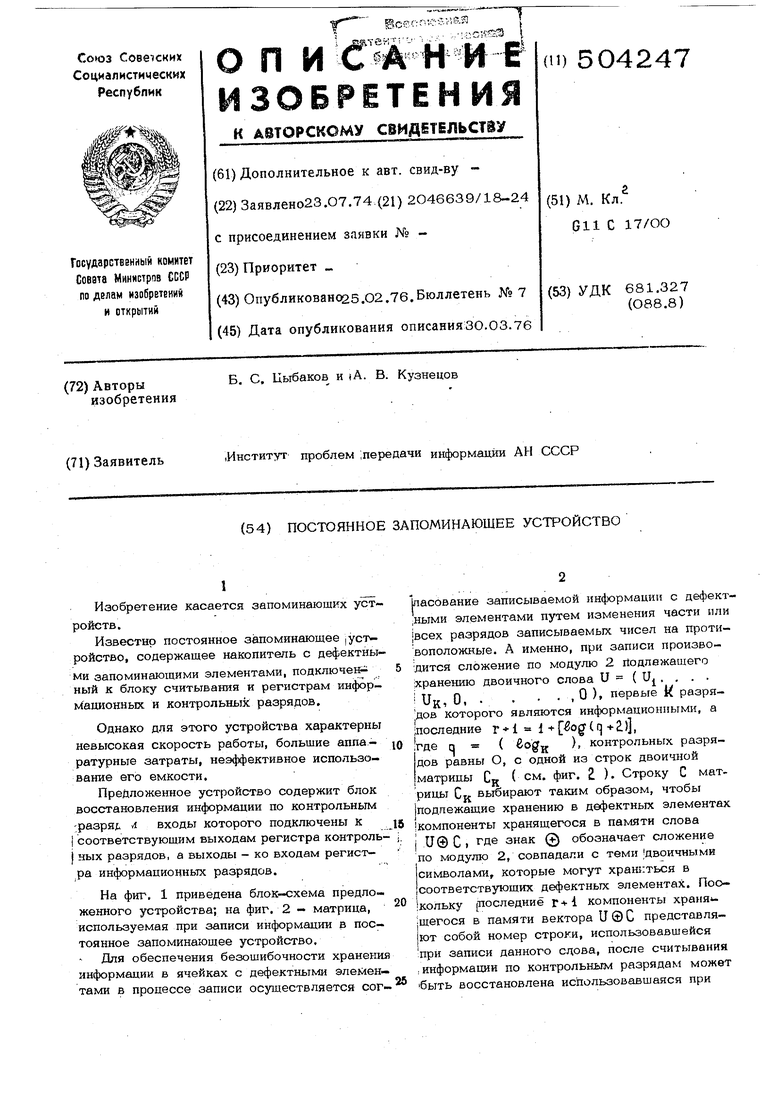

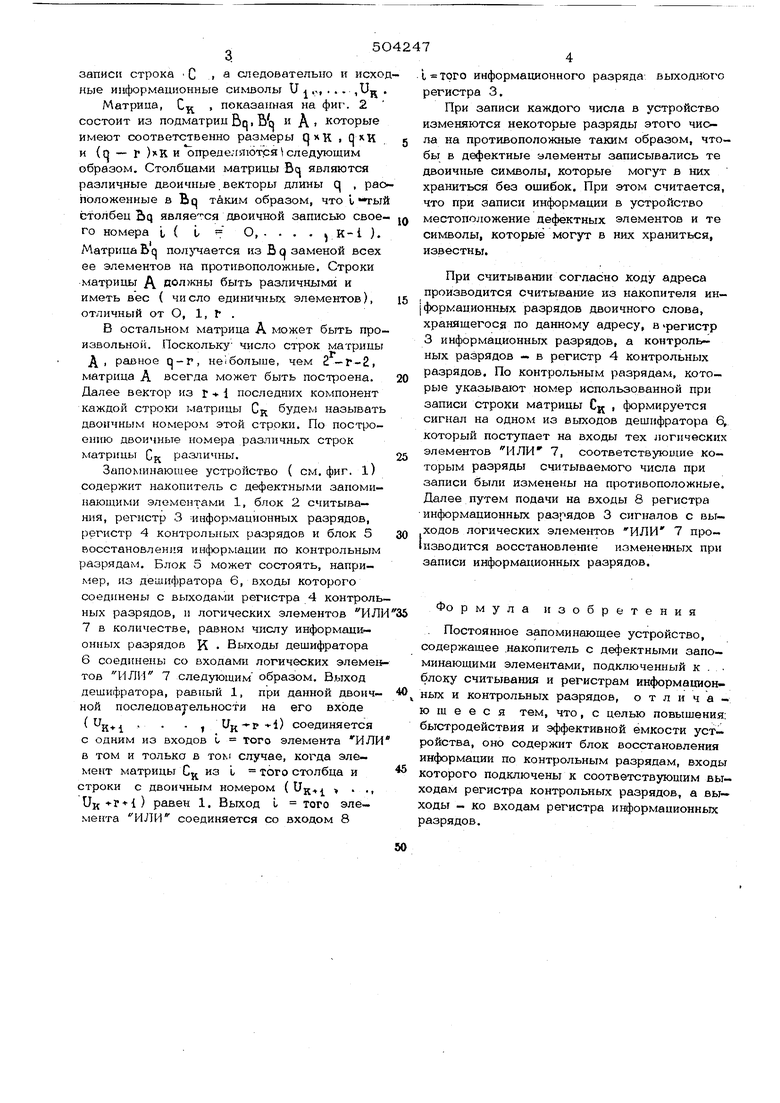

Изобретение касается запоминаюших устройств. Известно постоянное з)апомннающее уст- ройство, содержащее накопитель с дефектными запоминающими элементами, подключен ный к блоку считывания и регистрам инфорМ ационных и KOHTponbHbik разрядов. Однако для этого устройства характерны невысокая скорость работы, большие аппаратурные затраты, неэффективное использование его емкости. Предложенное устройство содержит блок восстановления информации по кoнтpoльньпvI -разряд л входы которого подключены к j соответствующим выходам регистра контроль) ных разрядов, а выходы - ко входам регист,ра информационньхх; разрядов. На фиг, 1 приведена блок-схема предложенного устройства; на фиг. 2 - матрица, используемая при записи информации в постоянное запоминающее устройство. Для обеспечения безошибочности хранения информации в ячейках с дефектными элементами в процессе записи осуществляется сог ласование записываемой информации с дефект,ными элементами путем изменения части или всех разрядов записываемых чисел на противоположные. А именно, при записи производится сложение по модулю 2 Подлежащего Хранению двоичного слова U ( Uj, . . . I UK, О, . . . , О Ь первые k разрядов которого являются информационными, а ;последние г 1 1 og (q 2.), :Где q ( ogj ), контрольных разрядов равны О, с одной из строк двоичной матрицы Сд ( см. фиг. 2. ). Строку С матрицы Cj{ выбирают таким образом, чтобы подлежащие хранению в дефектных элементах компоненты хранящегося в памяти слова j и® С ) Д® знак @ обозначает сложение по модулю 2, совпадали с теми {двоичными символами, которые могут храниться в соответствующих дефектных элементах. Поо|кольку Последние компоненты храня щегося в памяти вектора U © С представля|ют собой номер строки, использовавшейся при записи данного сдова, после считывания : информации по контрольным разрядам может быть восстановлена использовавшаяся при записи строка С .а следовательно и исхо ные ии юрмационные символы U .,,... ,Ujj Матрица, С , показанная на фиг. 2 состоит из подматриц Во Ьо и Д , которые имеют соответственно размеры Ц)К , q и (о - Г )К и определяютсяiследующим образом. Столбцами матрицы Ви являются различные двоичные.векторы длины q , рао пОложенные в Bq таким образом, что I столбец bq являе ся двоичной записью свое го номера t ( 1 О, . . . . K-t ). Матрица Во пол чается из В о заменой всех ее элементов на противоположные. Строки матрицы Д должны быть различными и иметь вес ( чи ело единичных элементов), отличный от О, 1, Г . В остальном матрица А может быть про извольной. Поскольку число строк матрицы Д, равное q-r, не больше, чем 2-г-2, матрица А всегда может быть построена. Далее вектор из г + 1 последних компонент каждой строки матрицы CK будем называть двоичным номером этой строки. По построению двоичные номера различных строк матрицы Cj различны. Запоминающее устройство ( см. фиг. l) содержит накопитель с дефектными запоминающими элементами 1, блок 2 считывания, регистр 3 информационных разрядов, регистр 4 контрольных разрядов и блок 5 восстановления ин4юрмации по контрольным разрядам. Блок 5 может состоять, например, из дешифратора 6, входы которого соединены с выходами регистра 4 контроль ных разрядов, и логических элементов ИЛ 7 в количестве, равном числу информационных разрядов К Выходы дещифратора 6 соединены со входами логических элемен тов ИЛИ 7 следующим образом. Выход дешифратора, равный 1, при данной двоичной последовательности на его входе ) соединяется с одним из входов I того элемента ИЛИ в том и только в том случае, когда элемент матрицы Cj из I того столбца и строки с двоичным номером ( UK+J ... UK ) равен 1. Выход L того элемента ИЛИ соединяется со входом 8 информационного разряда выходного регистра 3. При записи каждого числа в устройство изменяются некоторые разряды этого чиола на противоположные таким образом, чтобы в дефектные элементы записывались те двоичные символы, которые могут в них храниться без ошибок. При этом считается, что при записи информации в устройство местоположение дефектных элементов и те символы, которые могут в них храниться, известны. При считывании согласно коду адреса производится считывание из накопителя ин- I формационных разрядов двоичного слова, хранящегося по данному адресу, в -регистр 3 информационных разрядов, а контрольных разрядов - в регистр 4 контрольных разрядов. По контрольным разрядам, которые указывают номер использованной при записи строки матрицы С i формируется сигнал на одном из выходов дешифратора 6, который поступает на входы тех логических элементов ИЛИ 7, соответствующие которым разряды считываемого числа при записи были изменены на противоположные. Далее путем подачи на входы 8 регистра информационных разрядов 3 сигналов с выходов логических элементов ИЛИ 7 производится восстановление измененных при записи информационных разрядов. Формула изобретения Постоянное запоминающее устройство, содержащее .накопитель с дефектными запоминающими элементами, подключенный к . . блоку считывания и регистрам информационных и контрольных разрядов, отличающееся тем, что, с целью повыщения: быстродействия и эффективной емкости устройства, оно содержит блок восстановления информации по контрольным разрядам, входы которого подключены к соответствующим выходам регистра контрольных разрядов, а выходы - ко входам регистра информационных разрядов.

пг

-ЦП

//г./

Фиг. 2

Авторы

Даты

1976-02-25—Публикация

1974-07-23—Подача