1

Изобретение относится к вычислительной технике, может быть использовано в системах обработки данных, системах управления, в информацион«о-изл1ерительных комплексах.

Известны устройства для обмена данными, содержащие коммутатор каиало-в, соединенный с его первыми входом и выходом, счетчик адресов, первые вход и выход которого подключены соответственно ко вторым входу и выходу устройства, блок управления, выходы которого подключены соответственно к управляющим входам коммутатора канало-з, счетчика адресов, третьему, четвертому и пятому выходам устройства, входы - к третьему и четверто.му входам устройства, второй выход счетчика адресов соединен с соответствующем входом коммутатора каналов.

Известные устройства предназначены для поочередной организации связей междувнешним устройством и оперативным запоминающим устройством (ОЗУ).

Выбранное по программе внещнее устройство подключается к ОЗУ с помощью блока управления путем задания адреса зоны в ОЗУ, кода номера внещнего устройства и признака режима обмена (прием или передача). Дальнейший обмен продолжается только с подключенным устройством. Чтобы перейти на обмен с другим устройством, надо прервать программу работы процессора и повторить все операции по подключению нового устройства.

Цель изобретения - повыщение производительности устройства.

Предлагаемое устройство отличается тем, что в него введены блоки приоритетного выбора каналов окончания обмена и приоритетного выбора каналов синхросигналов, комм -таторы и регистраторы связи, выходы которых через первый коммутатор подключены ко входу коммутатора каналов, входы - соответственно к выходу блока управления и выходу второго коммутатора, входы которого соединены с соответствующим выходом блока управления, пятым входом устройства, первыми выходами блоков приоритетного выбора .каналов окончания обмена и приоритетного выбора каналов синхросигналов, вторые выходы которых подключены к соответствующим входам блока управления, входы-к шестому и седьмому входам устройства соответственно, выход первого коммутатора подключен ко BTOpoMiy входу счетчика адресо Б.

Это позволяет переключать каналы обмена с внешними устройствами без участия процессора и без прерывания програ.ммы его работы.

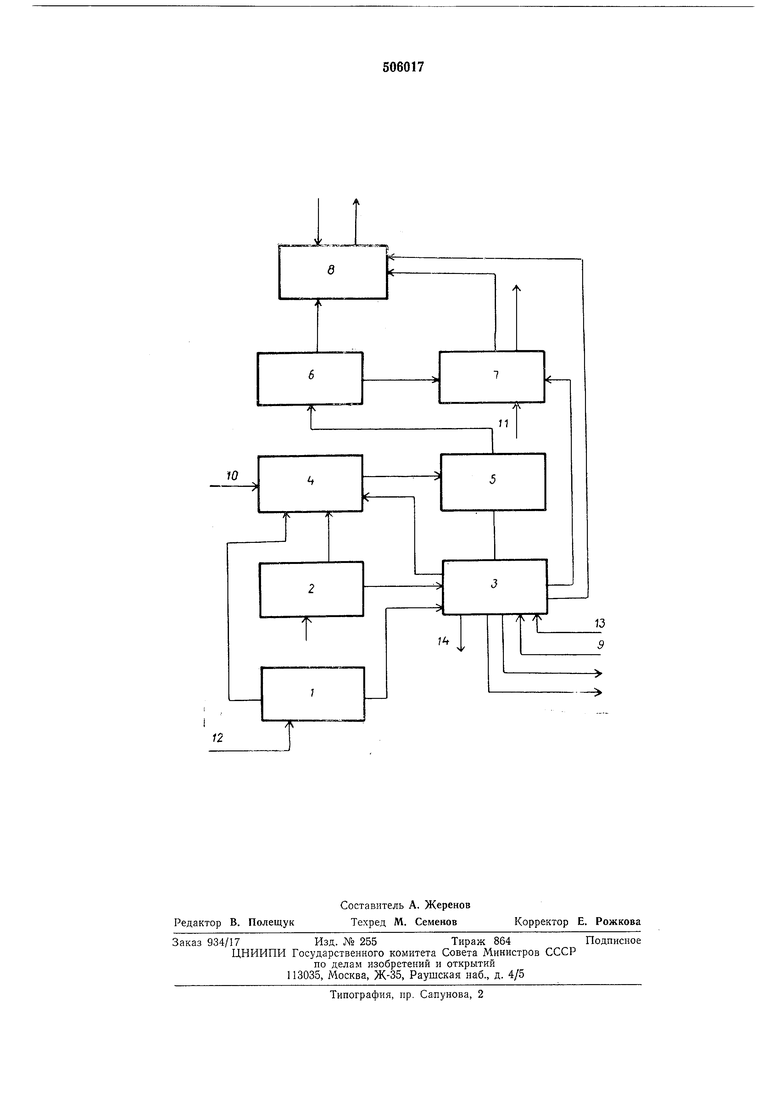

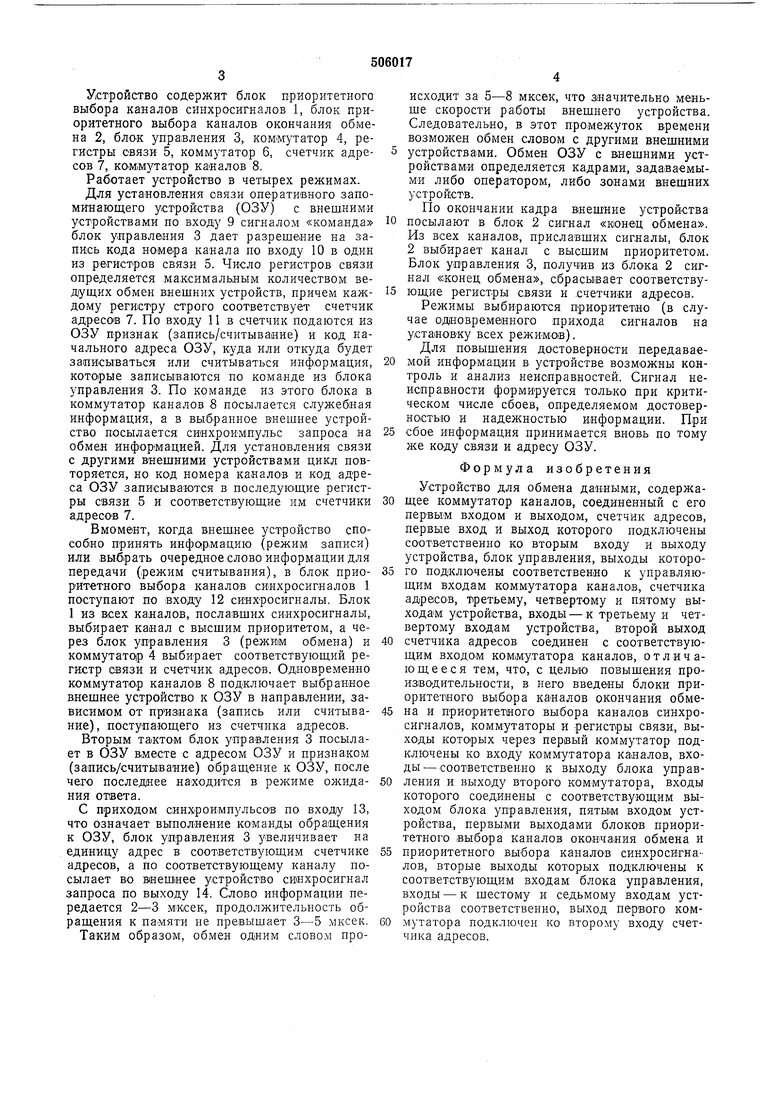

На чертеже представлена схема устройства.

Устройство содержит блок приоритетного выбора каналов синхросигналов 1, блок приоритетного выбора каналов окончания обмена 2, блОК упра1вления 3, коммутатор 4, регистры связи 5, коммутатор 6, счетчик адресов 7, коммутатор кавалов 8.

Работает устройство в четырех режимах.

Для установления связи оперативного запоминающего устройства (ОЗУ) с внешними устройствами по входу 9 сигналом «команда блок управления 3 дает разрешение на запись кода номера канала по входу 10 в один из регистров связи 5. Число регистров связи определяется максимальным количеством ведуш их обмен внешних устройств, причем каждому регистру строго соответствует счетчик адресов 7. По входу 11 в счетчик подаются из ОЗУ признак (запись/считывание) и код начального адреса ОЗУ, куда или откуда будет записываться или считываться информация, которые записываются по команде из блока управления 3. По команде из этого блока в коммутатор каналов 8 посылается служебная информация, а в выбранное внешнее устройство посылается синхрои-мпульс запроса на обмен информацией. Для установления связи с другими внешними устройствами цикл повторяется, но код номера каналов и код адреса ОЗУ записываются в последующие регистры связи 5 и соответствующие им счетчики адресов 7.

Вмомент, когда внешнее устройство способно принять информацию (режим записи) или выбрать очередное слово информации для передачи (режим считывания), в приоритетного выбора каналов синхросигналов 1 поступают по входу 12 синхросигналы. Блок 1 из всех каналов, пославших синхросигналы, выбирает канал с высшим приоритетом, а через блок управления 3 (режим обмена) и коммутато|р 4 выбирает соответствующий регистр связи и счетчик адресов. Одновременно коммутатор каналов 8 подключает выбранное внешнее устройство к ОЗУ в направлении, зависимом от признака (запись или считывание) , поступающего из счетчика адресов.

Вторым тактом блок управления 3 посылает в ОЗУ вместе с адресом ОЗУ и призна.ком (запись/считывание) обращение к ОЗУ, после чего последнее находится в режиме ожидания ответа.

С приходом синхроимпульсов по входу 13, что означает выполнение ко манды обращения к ОЗУ, блок управления 3 увеличивает на единицу адрес в соответствующим счетчике адресов, а по соответствующему каналу посылает во В1нешнее устройство синхросигнал запроса по выходу 14. Слово информации передается 2-3 мксек, продолжительность обращения к памяти не превышает 3-5 мксек.

Таким образом, обмен одним словом происходит за 5-8 мксек, что значительно меньше скорости ра.боты внешнего устройства. Следовательно, в этот промежуток времени возможен обмен словом с другими внешними устройствами. Обмен ОЗУ с внешними устройствами определяется кадрами, задаваемыми либо оператором, либо зонами внешних устройств.

По окончании кадра внешние устройства

посылают в блОК 2 сигнал «конец обмена. Из всех каналов, приславших сигналы, блок 2 выбирает канал с высшим приоритетом. Блок управления 3, получив из блОКа 2 сигнал «конец обмена, сбрасывает соответствующие регистры связи и счетчики адресов.

Режимы выбираются приоритетно (в случае одновременного прихода сигналов на установку всех режимов). Для повышения достоверности передаваемой информации в устройстве возможны контроль и анализ неисправностей. Сигнал неисправности формируется только при критическом числе сбоев, определяемом достоверностью и надежностью информации. При

сбое информация принимается вновь по тому же коду связи и адресу ОЗУ.

Формула изобретения

Устройство для обмена данными, содержащее коммутатор каналов, соединенный с его первым входом и выходом, счетчик адресов, первые вход и выход которого подключены соответственно ко вторым входу и выходу устройства, блок управления, выходы которого подключены соответственно к управляющим входам коммутатора каналов, счетчика адресов, третьему, четвертому и пятому выходам устройства, входы - к третьему и четвертому входам устройства, второй выход

счетчика адресов соединен с соответствующим входом коммутатора каналов, отличающееся тем, что, с целыю повышения произ)водительпости, в него введены блоки приоритетного выбора каналов окончания обмена и приоритетного выбора каналов синхросигналов, коммутаторы и регистры связи, выходы которых через первый коммутатор подключены ко входу коммутатора каналов, входы-соответственно к выходу блока управления и выходу второго коммутатора, входы которого соединены с соответствующим выходом блока управления, пятым входом устройства, первыми выходами блоков приоритетного выбора каналов окончания обмена и

приоритетного выбора каналов синхросигналов, вторые выходы которых подключены к соответствующим входам блока управления, входы - к шестому и седьмому входам устройства соответственно, выход первого коммутатора подключен ко второму входу счетчика адресов.

13

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена | 1976 |

|

SU636603A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для управления обменом | 1986 |

|

SU1315986A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

12

Авторы

Даты

1976-03-05—Публикация

1973-01-08—Подача