1

Изобретение относится к вычислительной технике и может найти применение при построении специализированных вычислительных устройств.

Известны арифметико-логические устройства, позволяющие производить суммирование операндов и формировать различные логические функции двух переменных 1. Недостатком таких устройств является невозможность выполнения сложения операнда с удвоенным другим операндом, а также сдвигов результата.

Наиболее близким к предлагаемому является арифметико-логическое устройство, содержащее регистры первого и второго операндов, блок распространения переносов, полусумматор и первый логический коммутатор, входы разрядов которого соединены с выходами прямого и инверсного значений разрядов регистров первого и второго операндов, первый выход каждого разряда первого логического коммутатора соединен со входом соответствующего разряда блока распространения переносов, выходы разрядов которого соответственно подключены ко входам разрядов полусумматора 2J.

В известном устройстве не выполняются арифметические операции со сдвигом в одном цикле, не выполняются предварительные сдвиги одного из операндов и арифметические операции в одном цикле и устройство не имеет дополнительного входа для выполнения коррекции результата, которая необходима при завершении операции деле0ния. Все это ограничивает быстродействие устройства при выполнении операций умножения и деления.

Целью изобретения является увеличение быстродействия устройства при

5 выполнении операций умножения и деления .

Для достижения этой цели в устройство введены второй, третий и четвертый логические коммутаторы, блок эле0ментов И и регистр результата, причем первый и второй выходы первого логического коммутатора поразрядно соединены с первым и вторым входами второго логического коммутатора,

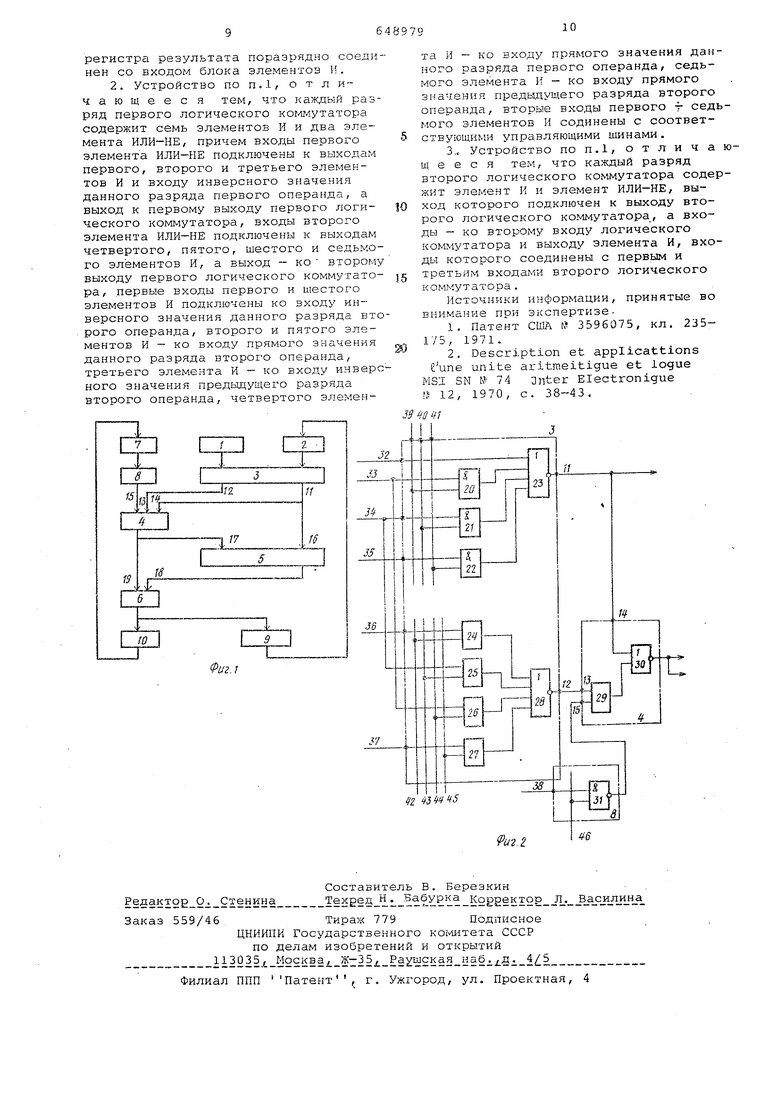

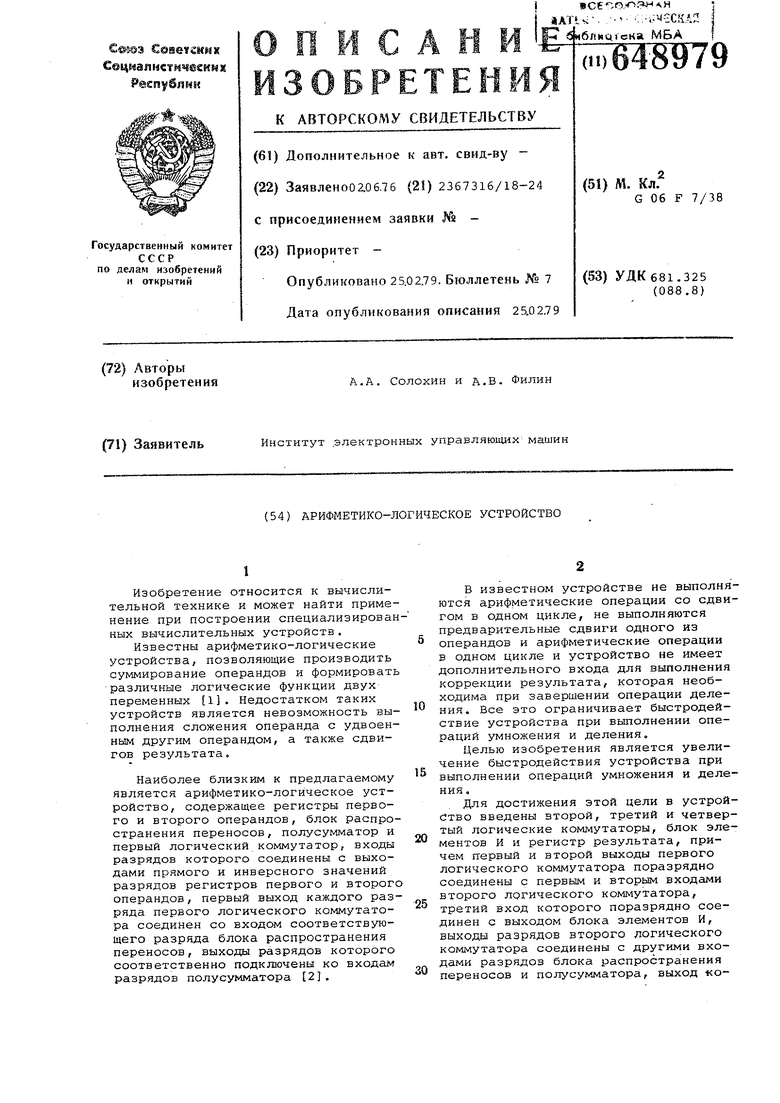

5 третий вход которого поразрядно соединен с выходом блока элементов И, выходы разрядов второго логического коммутатора соединены с другими входами разрядов блока распространения переносов и полусумматора, выход «оторого поразрядно соединен со вхол;ами третьего и четвертого логических коммутаторов, выходы которых соединены со входами соответственно регистра второго операнда и регистра резуль тата/ выход регистра результата поразрядно соединен со входом блока элементов И, Поставленная цель достигается также тем, что каждый разряд первого логического коммутато За содержит семь элементов И и два элемента ИЛИНЕ, причем входы первого элемента ИЛИ Н.Е подключены к выходам первого, вто рого и третьего элементов И и входу инверсного значения данного разряда первого операнда, а выход -- к первом выходу первого логического коммутатора,, входы второго элемента ИЛИ-ИЕ подключены к выходам четвертого, пятого, шестого и седьмого элементов И а выход - ко второму выходу первого логического коммутатора, первые входы первого и шестого элементов И под ключены ко входу инверсного значения. данного разряда второго операнда, второго и пятого элементов И - ко вх ду прямого значения данного разряда второго операнда, третьего элемента И - ко входу инверсного значеЕ1ия предыдущего разряда второго операнда четвертого элемента И - ко входу пря мого значения да 1ного раз.ряда первого .операнда, седьмого элемента И ко входу прямого значения предыдущег разряда второго операнда, вторые вхо ды первого седьмого элементов И соединены с соответствующими управляющими шинами; каждый разряд второг логического коммутатора содержит эле мент И и элемент -ИЛИ-НЕ, выход которого подключен к выходу второго логического коммутатора, а входы -- ко второму входу логического коммутатора и выходу элемента И, входы которого соединены с первым и третьим входами второго логического коммутатора. На фиг. 1 изображена структурная схема арифметико-логического устройства; на фиг, 2 - логическая схема одного разряда первого и второго логических коммутаторов, а также блока элементов И. Арифметико-логическое устройство содержит регистр 1 первого операнда регистр 2 второго операнда, первый логический коммутатор 3, второй логический коммутатор 4, блок 5. распространения переносов, полусу1 1а тор 6, регистр 7 результата, блок элементов И 8,.третий логический коммутатор 9, четвертый логический коммутатор 10, первые., выходы 11 раз рядов первого логического коммутато ра 3, вторые выходы 12 разрядов пер вого логического коммутатора 3, пер вые входы 13, вторые входы 14, трет входы 15 разрядов вто)ого логического коммутатора 4, первые входы 16 и вторые входы 17 разрядов блока 5 распространения переносов, первые входы 18 разрядов полусумматора б, вторые входы 19 разрядов полусумматора 6 . Каждый разряд первого логического коммутатора 3 содержит элементы И 20-г 22, элемент ИЛИ-НЕ 23, элементы И 24 27, элемент ИЛИ-НЕ 28. Каждый разряд второго логического KOMjviyTaTOpa 4 содержит элемент И 29 и элемент ИЛИ-НЕ 30. В каждом разряде блока логических элементов И 8 содержится элемент ИНЕ 3 1 . Устройство выполнено следующим образом , Устройство имеет регистр 1 первого операн.да 1 и регистр 2 второго операнда. Выходы прямого и инверсного знач М Ий каждого разряда этих регистров соединены с соответствующими входами первого логического коммутатора 3. Первый логический коммутатор 3 имеет для каждого разряда два входа. Вы.ходы 13 первого логического коммутатора 3 соединены со входами 14 второго логического коммутатора 4 и входами 16 блока 5 распространения переносов-. Выходы 12 первого логического коммутатора 3 подключены к входам 13 второго логического коммутатора 4. Выходы каждого разряда второго логического коммутатора 4 подключены ко входам 17 блока 5 распространения переносов и входам 19 полусумтч-татора 6. ВЫХОД.Ы блока 5 распространения переносов подключены к входам 18 полусумматора 6. Выходы каждого разряда полусумматора 6 соединены со входами третьего и четвертого логических коммутаторов 9 и 10. Выходы третьего логического коммутатора 9 подключены ко входам регистра 2 второго операнда,- а выходы четвертого логического коммутатора 10 подключены ко входам регистра результата 7, Выходы регистра результата 7 через блок 8 логических элементов И подключены к входам 15 второго логического коммутатора 4 . Один разряд первого логического ком14утатора 3 содержит в каждом разряде семь элементов И 20, 21, 22, 24, 25, 26 и 27, два элемента ИЛИ-НЕ 23 и 28 и имеет шесть информационных вхо-дов 32-37, (38 - один из входов блока 8 элементов И), семь управляющих шин 39-45 и два выхода 11 и 12. Информационные входы 32-37 первого логического KOMivsyTaxopa 3 подключены к соответствующим выходам регистров 1 и 2 первого и второго операндов. Вход 32 инверсного зваче ВИЯ данного разряда первого операнда подключен к первому входу элемента ИЛИ-НЕ 23, В&од 33 инверсного значения данного разряда второго операнда подключен к входам элементов И 20

и 26. Вход 34 прямого значения данного разряда второго операнда подключен к входам элементов И 21 и 24.

Вход 35 инверсного значения предьщущего разряда второго операнда поключен к элементу И 22. Вход 36 прямого значения данного разряда первого операнда йодключен к входу элемента И 24 . Вход 37 прямого значения предыдущего разряда второго операнда подключен ко входу элемента И 27. Каждая управляющая шина 39-:-45 первог логического коммутатора 3 подключена ко второму входу соответствующего элемента И 20, 21, 22, 24, 25, 26, 27. Выходы элементов И 20, 21 и 22 подключены ко входам элемента ИЛИНЕ 23. Выходы элементов И 24-27 по,ключены ко входам элемента 28

Выход элемента ИЛИ-НЕ 23 подключен к первому выходу 11 первого логического коммутатора 3. Выход элемента ИЛИ-НЕ 28 подключен ко эторому выходу 12 первого логического KOMJ yтатора 3. Один разряд второго логического коммутатора 4 включает в себя элемент И 29 и элемент ИЛИ-НЕ 3 Первый и третий входы 13 и 15 второго логического коммутатора 4 подключены ко входам элемента И 29. Второй вход 14 второго логического коммутатора 4 подключен к входу элемента ИЛ НЕ 30, Выход элемента И 29 подключен к другому входу элемента ИЛИ-НЕ 30, выход которого подключен к выходу ВТ -рого логического коммутатора 4 ,

Каждый разряд блока 8 элементов И представляет собой элемент И-НЕ 31, первый вход которого соединен со входом 38 прямого значения данного разряда результата, а второй вход подключен к управляющей шине 46.

Устройство работает следующим образом,

В регистр 1 первого операнда и регистр 2 второго операнда помещаются операнды: прямое и инверсное значение каждого разряда операндов поступают на соответствующие входы первого логического коммутатора 3 (входы 32-37) и над ними выполняются функции, определяемые управляющими сигналами, поступающими по управляющим шинам 39-45. В результате этого на первых выходах 12 первого логического коммутатора 3 формируется конъюнкция либо прямых значений операндов, либо конъюнкция инверсного значения первого и прямого значения второго операндов одноименных разрядов, либо конъюнкция прямого значения второго операнда и прямого значения операнда на разряд младше рассматриваемого, либо логический нуль.

Так же, в зависимости от управляющих сигналов, на вторых выходах 12 первого логического коммутатора 3 формируется конъюнкция либо инверсных значений операндов, либо прямого значения первого операнда и инверсного значения второго, либо конюнкция инверсного значения первого операнда на один разряд младше рассматриваемого и инверсного значения второго операнда данного разряда, либо логическая единица.

Выходные сигналы на выходах 11 и 12 первого логического KON-sMyTaTOpa 3 поразрядно поступают на первые и вторые входы 13 и 14 второго логического коммутатора 4. На третьи входы 15 второго логического коммутатора 4 поступают сигналы с выходов блока 8 элементов И. Когда производятся операции над операндами, хранящимися в регистрах 1 и 2 первого и второго операндов, блок 8 элементов И закрыт Второй логический коммутатор 4 осуществляет дизъюнкцию первых и вторых входов 13 и 14.

Таким образом, при закрытом состоянии блока 8 элементов И в зависимости от управляющих сигналов на управляющих шинах первого логического коммутатора 3, на выходах каждого разряда второго логического коглмутатора 4 образуются либо сумма по модулю 2 соответствующих разрядов, либо функция эквивалентности соответствующих разрядов, либо сумма по модулю 2 значения разряда первого операнда на единицу младше рассматриваемого и значения второго операнда рассматриваемого разряда, либо логический нуль

Выходные сигналы с первых выходов 11 первого логического коммутатора 3 и выходные сигналы второго логического комм татора 4 поступают на входы блока 5 распространения переносов. Выходные сигналы блока 5 распространения переносов поступают на первые входы полусумматора 6. На вторые входы полусумматора 6 поступают сигналы со второго логического коммутатора 4. В этом блоке над ними производится логическая операция сложение по модулю 2 и на выходах образуются сигналы суммы.

Сигналы с выходов полус умматора 6 поступают на входы третьего и четвертого логических коммутаторов 9 и 10. В третье,м логическом коммутаторе входные сигналы передаются на выход либо без сдвига, либо со сдвигом .на один разряд влево, либо со сдвигом на два разряда вправо. С выхода третьего логического коммутатора 10 сигналы поступают на вход регистра 2 второго операнда.

Рассмотрим выполнение операции сложения первого операнда с удвоенным вторы операндом и со сдвигом результата На два разряда вправо. Эта операция, как и операции сложения или вычитания операндов со сдвигом результата на два разряда вправо, является основой для реализации умножения по методу умножения на два разряда одновременно . В регистры 1 и 2 первого операнда и второго операнда заносятся слагаемые. Управляющие сигналы, подаваемы (ia первый логический кo a4yтaтop 3, настраивают его так, что на первых е выходах 11 образуется конъюнкция пря мого кода первого операнда и прямого кода второгооперанда, сдвинутого на один разряд влево, а на вторых выходах - конъюнкция инверсного кода пер вого операнда . и инверсного кода второго операнда, также сдвинутого на один разряд влево. Для выполнения таких функций упра ляющие сигналы уровня логической единицы подаются на управляющие шины 41, 42 и 45. На другие управляю щие шины (39,40,43 и 44) подаются си налы логического нуля. Элементы И-НЕ 31 закрыты управляющим лом на управляющей шине 46 и на выходах второго логического коммутатора, поразрядно образуется суг,-1ма по юдyлю 2 удвоенного первого опе ранда и второго операнда. Сз гналы с первых выходов 11 первого логического коммутатора 3 и с выходов второго логического коммутатора 4 поступают на блок.5 распространения переносов. В этом бло.ке образуются сигналы переноса, которые на полусумматорах б складываются по .модулю 2 с сигна лами с в лходов второго логическог-о коммутатора 4 и образуют cyrviMy., Третий логический коммутатор 9 осуществляет сдвиг кодов с выходов полусумматора б на два разряда вправо и результат поступает на вход регистра второго операнда 2. Аналогично выполняются операции сложения и вычитания со сдвигом на два разряда вправо. Они отличаются от предыдущей только набором управляющих сигналов первого логического коммутатора 3, Операция сложения и вычитга-гия над операндами в первом и втором регистрах 1 и 2 со сдвигом результата на один разряд влево, па которых основано выполнение деления, отличаются от предыдущих набором управляюш.их сигналов на третьем логическом коммутаторе 9 . При реализации деления в дополнительных кодах возникает необходимост произвести в конце выполнения коррек цию результата - прибавить единицу в младший разряд результата. При вы полнении коррекции содержимого регистра результата 7 управляющие-сиг налы, подаваемые на первый логический коммутатор 3, настраивают его так, что на его первых выходах форм руются сигналы логического нуля а на BTOpbix выходах - логической единицы, блок 8 элементов И 8 открывается и на выходах второго ло гического коммутатора 4 появляется код корректируемого числа. Коды на , первых выходах первого логического KOiviMyTaTopa 3 (логический нуль ) и на выходах второго логического коммутатора 4 (код корректируемого числа) эквивалентны сложению корректируемого числа с нулем. На вход пееноса в младший разряд блока 5 расространения переноса подается корректирующая единица и на выходах поусумматора б появляется корректированное число, которое, пройдя через четвертый логический коммутатор 10, поступает в регистр результата 7. Таким образом, введенные схемные изменения позволяют выполнять за одну операцию {один цикл работы устройства) следующую цепочку преобразований информации: сдвиг одного операнда на один разряд, сложение второго операнда с результатом сдвига первого операнда и сдвиг результата сложения . Для подобного преобразования информации в прототипе необходимо выполнить три операции, т.е. три раза пропустить обрабатываемую информацию через устройство. Таким образом, в данном устройстве повышается быстродействие при выполнении операций умножения и деления. Формула изобретения 1. Арифметико-логическое устройство, содержащее регистры первого и второго операндов, блок распространения переносов, полусумматор и первый логический коммутатор, входы разрядов которого соединены с выходами прямого и инверсного значений разрядов регистра первого и второго операндов, первый выход каждого разряда первого логического коммутатора соединен со входом соответствующего разряда блока распространения переносов, выходы разрядов которого соответственно подключены ко входа разрядов полусуг матора, отличающееся тем, что, с целью увеличения быстродействия устройства при выполнении операций умножения и деления, в него введены второй, третий и четвертый логические коммутаторы, блок элементов И и регистр результата, причем первый и второй выходы - ервого логического коммутатора поразрядно соединены с первым и вторым входами второго логического коммутатора, третий вход которого поразрядно соединен с выходом блока элементов И, выходы разрядов второго логического коммутатора соединены с другими входами разрядов блока распространения переносов и полусумматора, выход которого поразрядно соединен со входами третьего и четвертого логических коммутаторов, выходы которых соединены со входами сооткетственно регистра второго операьда и регистра результата, выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство | 1974 |

|

SU509870A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Управляемый арифметический модуль | 1989 |

|

SU1695292A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

Авторы

Даты

1979-02-25—Публикация

1976-06-02—Подача