Изобретение относится к вычислительной технике и предназначено для использования в системах понятия .

известные оперативные запоминающие устройства, содержащие регистр адреса, соединенный Соответственно через дешифратор адреса и непосредственно с основным накопителем и олоком запоминания ассоциативных признаков, управляющий вход которого через соединенные последовательно блоки управления и контроля подключен к блоку разрядных цепей, связанному с основным и резервным накопителями, не имеет повышенного быстродействия и надежности работы, обусловленными необходимостью (в случае неисправности) тратить время на считывание адресов резервных чисел и излишней избыточностью из-за хранения этих адресов.

Отличием описываемого устройства является то, что оно содержит элемент «ИЛИ, подключенный к индикаторным выходам блока запоминания ассоциативных признаков, соединенным €0 входами резервного накопителя, а выход элемента «ИЛИ подключен к управляющему входу дешифратора адреса. Это позволяет повысить быстродействие и надежность работы устройства.

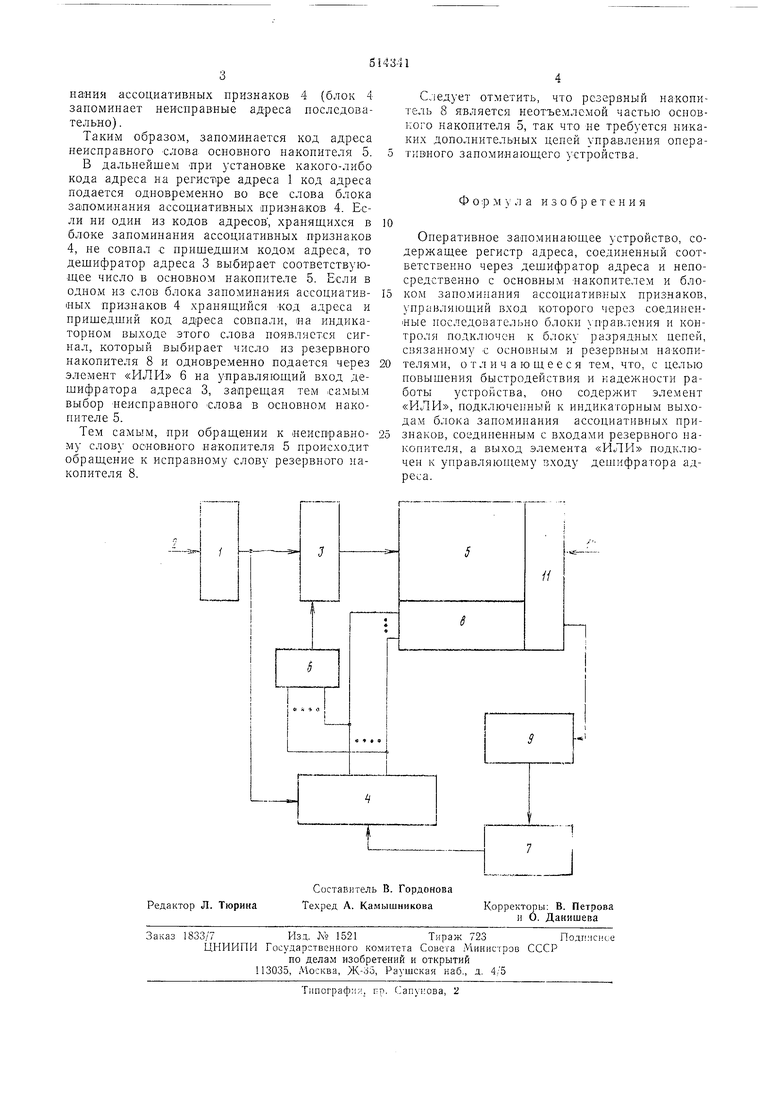

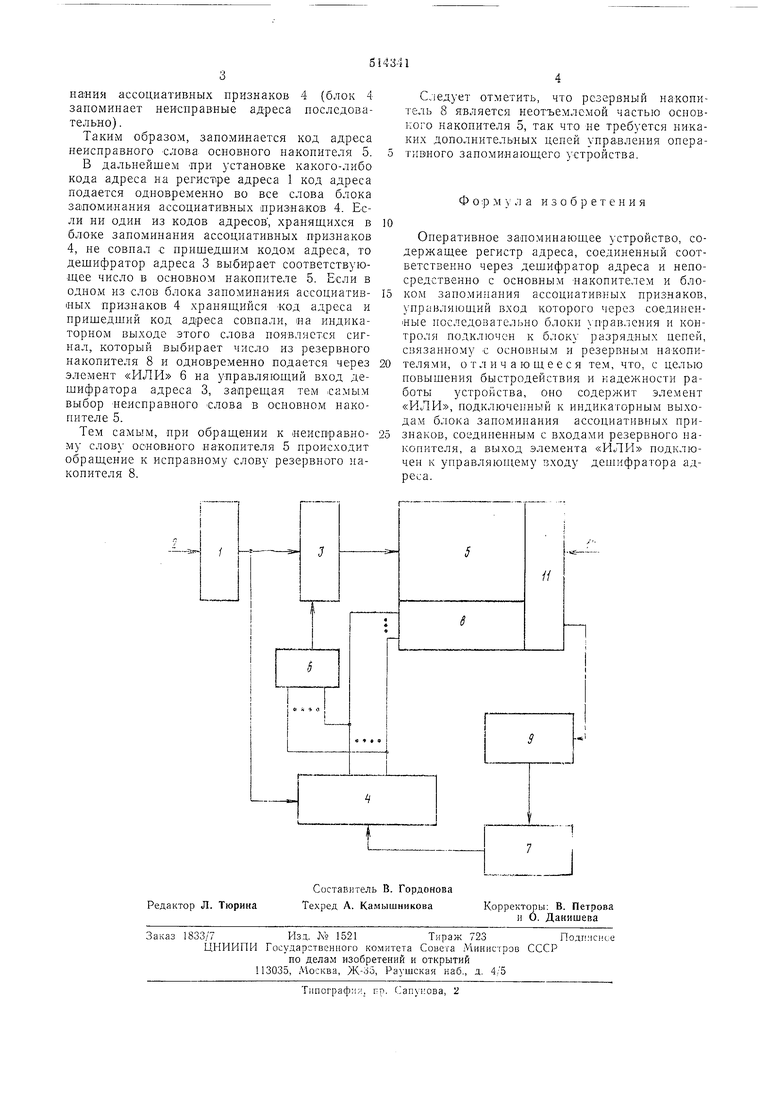

На чертеже показана блок-схема описываемого устройства.

Оно содержит регистр адреса 1 с адресным

входом 2, дешифратор адреса 3, блок запоминания ассоциативных признаков 4, основной накопитель о, элемент «ИЛИ о, Олок управления /, резервный накопитель а, олок

контроля у, информационный вход 10 и олок разрядных цепей il.

ь режиме «Запись или «Считывание информации код адреса запрашиваемого числа основного накопителя 5 подается на адресный

вход /. и запоминается в регистре адреса 1. 1ЧОД адреса с выходов регистра адреса 1 подается на дешифратор адреса 3 и иа соответствующий вход блока запоминания ассоциативных признаков 4. Дешифратор адреса

3 выоирает требуемое число в основном накопителе о. Ири этом в режиме «Запись информация поступает на информационный вход 10 и через блок разрядных цепей 11 записывается в выбранное число основного накопителя о, а в режиме «Считывание, если блок контроля 9 не обнаружил ошибки, информация считывается из выбранного числа основного накопителя 5 через блок разрядных цепей 11.

В случае, если при считывании информации из основного накопителя 5 блок контроля 9 обнаружил ошибку, то выдает сигнал на блок управления 7, который в свою очередь выдает сигнал на запись, когда адреса неисправного слова из регистра адреса 1 в блок запоминания ассоциативных признаков 4 (блок 4 запоминает неисправные адреса последовательно) .

Таким образом, запоминается код адреса неисправного слова основного накопителя 5.

В дальнейшем лри установке какого-либо кода адреса на региспре адреса 1 код адреса подается одновременно во все слова блока заиоминания ассоциативных призиакоВ 4. Если ни один из кодов адресов; хранящихся в блоке запоминания ассоциативных признаков 4, не совпал с пришедшим кодом адреса, то дешифратор адреса 3 выбирает соответствующее число в основном накопителе 5. Если в одном из слов блока запоминания ассоциативных признаков 4 хранящийся код адреса и пришедший код адреса совпали, на индикаторном выходе этого слова появляется сигнал, который выбирает число из резервного накопителя 8 и одновременно подается через элемент «ИЛИ 6 на управляющий вход дешифратора адреса 3, запрещая тем .самым выбор неисправного слова в основном накопителе 5.

Тем самым, при обращении к неисправному слову основного накопителя 5 происходит обращение к псправному слову резервного накопителя 8.

Следует отметить, что резервный накопитель 8 является неотъемлемой частью основного накопителя 5, так что не требуется никаких дополнительных цепей управления оперативного запоминающего устройства.

Ф о ;р м у Л а изобретения

Оперативпое запомипающее устройство, содержащее регистр адреса, соединенный соответственно через дешифратор адреса и непосредственпо с основным накопителем и блоком запоминания ассоциативных признаков, управляющий вход которого через соединенные носледовательно блоки управления и контроля подключен к блоку разрядных цепей, связанному с основным и резервным накопителями, отличающееся тем, что, с целью повышения быстродействия и надежности работы устройства, оно содержит элемент «ИЛИ, подключенный к индикаторным выходам блока запоминания ассоциативных признаков, соединенным с входами резервного накопителя, а выход элемента «ИЛИ подключен к управляюп,ему входу денгифратора адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU559282A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Ассоциативное запоминающее устройство | 1974 |

|

SU608198A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

Авторы

Даты

1976-05-15—Публикация

1974-12-30—Подача