Это достигается тем, что в устройство введены сумматор, элемент ИЛИ и одноразрядные элементы свертки, nepBbie входы которых подключены к выходам блока разрядных цепей и к оДнпм из входов сумматора 1„ вторые входы одноразрядных элементов свертки соедииены с другим выходом блока управления, третьи входы одаоразрядных элементов свертки подключены к выходам ассоциативного накопителя, третьи входы которого соединены с выходами сумматора и входами элемента ИЛИ, выход которого подключен к входу блока управления, информационные входы сумматора соединены с информационными входами устройства, выходы одноразрядных элементов свертки соединены с вы ходами устройства.

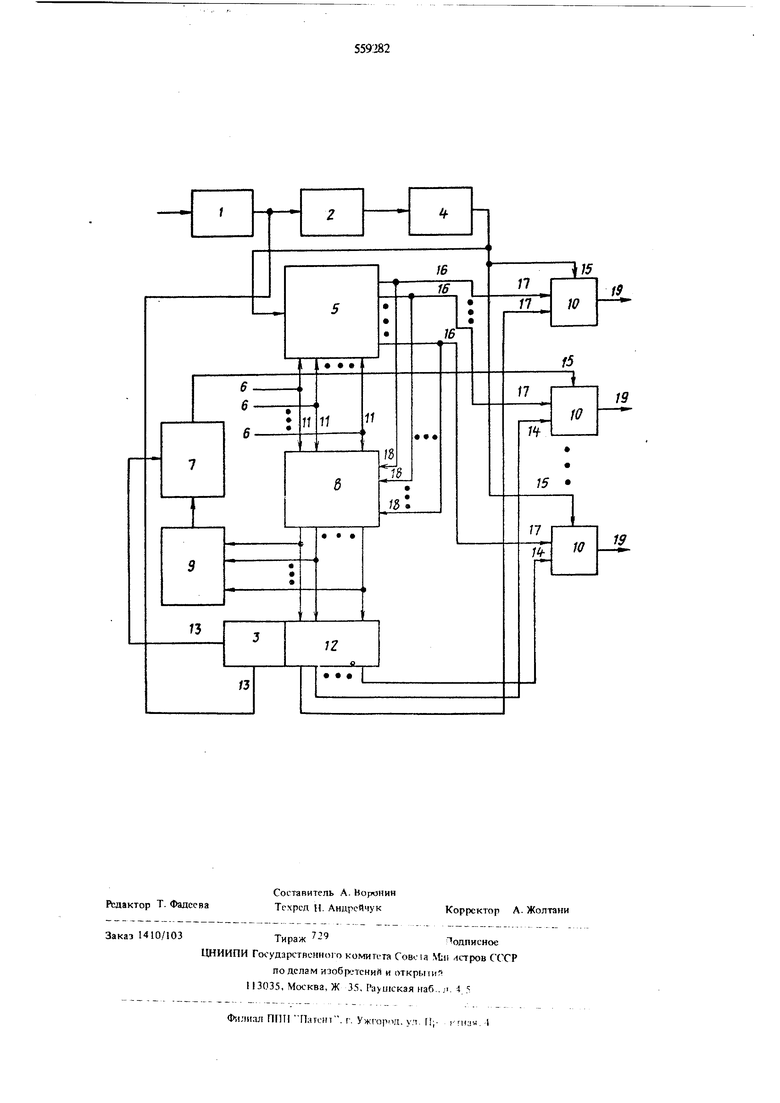

На чертеже представлена блок-схема предлагаемого устройства.

Оперативное заполшнающее устройство содержит регистр адреса 1, выходы которого соединены с входами дешифратора адреса 2 и с входом ассоциативного накопителя 3. Выходы дешифратора адреса 2 соединены с соответствующими входами блока накопителя 4, а выходы блока накопителя соединены с блоком разрядных цепей 5, на информационные входы 6 которого подается код числа, заиисываемый в ОЗУ. Кроме того, ассоциативный накопитель 3 соединен с блоком управления 7Оперативное запоминающее устройство содержит также сумматор 8, элемент ИЛИ 9 и одноразрядные элементы свертки 10 (по одному на один разряд сшеративного запоминающего устройства) Входы 11 сумматора 8 соединены с информационными входами 6 блока разрядных цепей 5, а выходы сумматора 8 с входами элемента ИЛИ 9 и с входами 12 ассоциативного накопителя 3. Кроме того, выходы 13 ассоциативного накопителя 3 соединены с третьими входами 14 соответствующих одноразрядных элементов свертки 10, вторые входы 15 которых соединены с блоком управления 7, который соединен с выходом элемента ИЛИ 9.

Выходы 16 блока разрядных цепей 5 соедине1п 1 с первыми входами, 17 соответствующих одноразрядных элементов свертки 10 и с входами 18 сумматора 8.

Устройство работает следующим образом. В режиме запись или считывание код адреса запрашиваемого числа наксшителя 4 подается в регистр адреса I. Код адреса с выхода регистра адреса 1 подается на дешифратор адреса .2 и на ассоциативный накопитель 3. Дешифратор адреса 2 выбирает требуемое число в накопителе 4.

В режиме, запись на информационный вход 6 блока разряднЬ1х цепей 5 подается код числа, который записывается в соответствующее чисЛо накопителя 4 и через входы 11 записывается в сумматор 8. Затем блок управления 7 выдает сигнал на считывание информации из числа накопителя 4, в которое в предыдущий момент была записана информация (на регистре адреса 1 продолжает оставаться код адреса, к которому производилось обращение по зш1иси к ОЗУ). Блок управления 7 выдает сигнал ш вторые входы 5 одноразрядных элементов свертки 10, блокируя их, и считавшая из накопителя i информация не проходит на выходы 19 ОЗУ, а подается на входы 18 сумматора 8.

В сумматоре производится сложение по модулю два записанного и считанного кода числа и в тех разрядах сумматора 8, в которых не произошло совпадение записанного и считанного кодов, появляется единица. Таким образом, наличие единицы на выходе сумматора 8 в каких-либо разрядах свидетельствует о неисправности в этих разрядах числа накопители 4, к которому произошло обращение по записи. При появлении хотя бы одной единицы ш выходе сумматора 8 на выходе элемента ИЛИ 9 появляется единица. Тогда блок управления 7 выдает сигнал на запись в число ассоциативного накопителя 3 кода адреса неисправного числа ОЗУ из регистра адреса 1 (ассоциативный накопитель 3 заполняется последовательно), а в число ассоциативного накопителя 3, соответствующего числу, в которое записан код адреса неисправного числа накопителя 4, записывается из сумматора код, который получился в результате сложения записанного и считанного кодов чисел. Таким образом, ассоциативный накопитель запоминает адреса неисправных чисел накош1теля 4, а также запоминает, какие неисправные разряды имеются в зтом числе.

В случае равенства записанного и считанного кодов на выходе сумматора 8 будут присутствовать одни нули во всех разрядах и блок управления 7 не выдаст сигнала на запись кода числа накопителя 4 в ассоциативный накопитель 3.

В режиме считывание код адреса числа, к которому производится обращение по считыванию, подается с выхода регистра 1 во все числа ассоциативного накопителя 3. Если ни один из кодов адресов хранящихся в ассоциативном накопителе 3 не совпал с прищедпшм кодом адреса, что означает, что обращение произошло к исправному числу накопителя 4, то дешифратор адреса 2 выбирает соответствующее число из накопителя 4, и производится считывание информации из этого числа. Так как блок управления 7 выдает соответствующий (догнал на вторые входы 15 одноразрядных элементов свертки 0, а с выходов 13 ассоциативного накопителя 3 на третьих входах 14 одноразрядных элементов свертки Ю присутствуют нули, которые не могут изменить считанный код числа, то с вькодов 16 считанный код числа попадает на первые входы 17 одноразрядных элементов свертки 10 (каждый разряд считанного кода - на соответствующую схему свертки 10) и проходит без изменений через них на выходы 19 ОЗУ.

Если же в одном из чисел ассоциативного накопителя 3 хранящийся код адреса и пришедший код адреса и пришедший код адреса совпали, что означает, что обращение произошло к неисправному числу накопителя 4, то из числа ассоциативного накопителя 3, соответствующего числу асооадативного накопителя 3, в котором произошло сх)впадение кодов, производится считывание кода. У этого кода единицы присутствуют в тех разрядах, которые соответствуют неисправным разрядам числа накопителя 4, к котсрому производится обращение по считьшанню. Этот код подается на третьи входы 1 соответствующих одноразрядных элементов свертки 10, и когда на первых входах 17 соответствующих одноразрядных элементов свертки 10 появляется считанный код числа, происходит исправление тех разрядов считанного кода числа, которые попадают на те одноразрядные элементы свертки 10, на третьих входах 14 которых присутствуют единицы, и тогда на выходах 19 ОЗУ будет появляться только правильная информация. Таким образом, при обращении по считыванию к какому-либо числу накопителя 4, в котором имеются неисправные разряды, отказы любой кратности, на выходах 19 ОЗУ будет появляться только правильно считанная информация. Предлагаемое оперативное запоминающее устр ойство имеет более высокую надежность, так как позволяет обнаруживать и исправлять отказы чисел накопителя любой кратности. Кроме того, за счет того, что избыточность предлагаемого ОЗУ практически не зависит от кратности отказов уменьшается объем используемой аппаратуры, что приводат к уменьшению его стоимости и габаритов, а также улучшению его ремонтопригодности. Формула изобретения Оперативное запоминающее устройство, содержащее последовательно соединенные регистр адреса, дешифратор адреса, накопитель и блок разрядных цепей, ассоциативный накопитель, первый вход которого соединен с выходом регастра адреса, второй вход ассоциативного накопителя подключен к одному из выходов блока управления, адресные входы устройства подключе}1ы к входам регистра адреса, информационные входы устройства соединены с входами блока разрядных цепей, отличающее; я тем, что, с целью повышения надежности устройства, в него введены сумматор, элемент ИЛИ и одноразрядные элементы свертки, первые входы которых подключены к выходам блока разрядных цепей и к одним из входов сумматора, вторые входы одноразрядных элементов свертки соединены с другим выходом блока управления, третьи входы одноразрядных элементов свертки подключены к выходам ассоциативного накопителя, третьи входы которого соединены с выходами сумматора и входами элемента ИЛИ, выход которого подключен к входу блока управления, информационные входы сумматора соединены с информационными входами устройства, выходы одноразрядных элементов свертки соединены с выходами устройства. Источники информации, принятые во внимание при экспертизе: США № 3422402, кл. 340-172,5, 1.Патент опубл. 1968. 2.Патент США № 3501748, кл. 340-172,5, опубл. 1969. ФРГ N 1290973, кл. 21 а 37/66, 3.Патент опубл. 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1976 |

|

SU733019A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Опреративное запоминающее устройство | 1976 |

|

SU645204A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Оперативное запоминающее устройство | 1974 |

|

SU514341A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

Авторы

Даты

1977-05-25—Публикация

1975-09-12—Подача