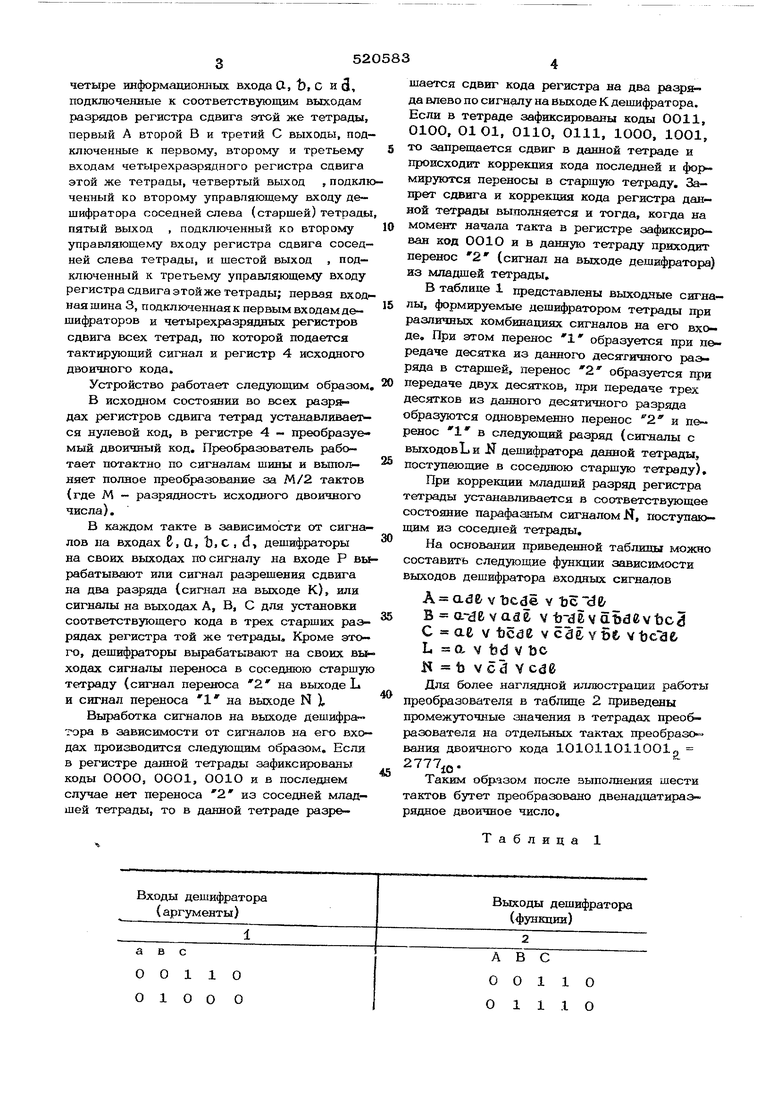

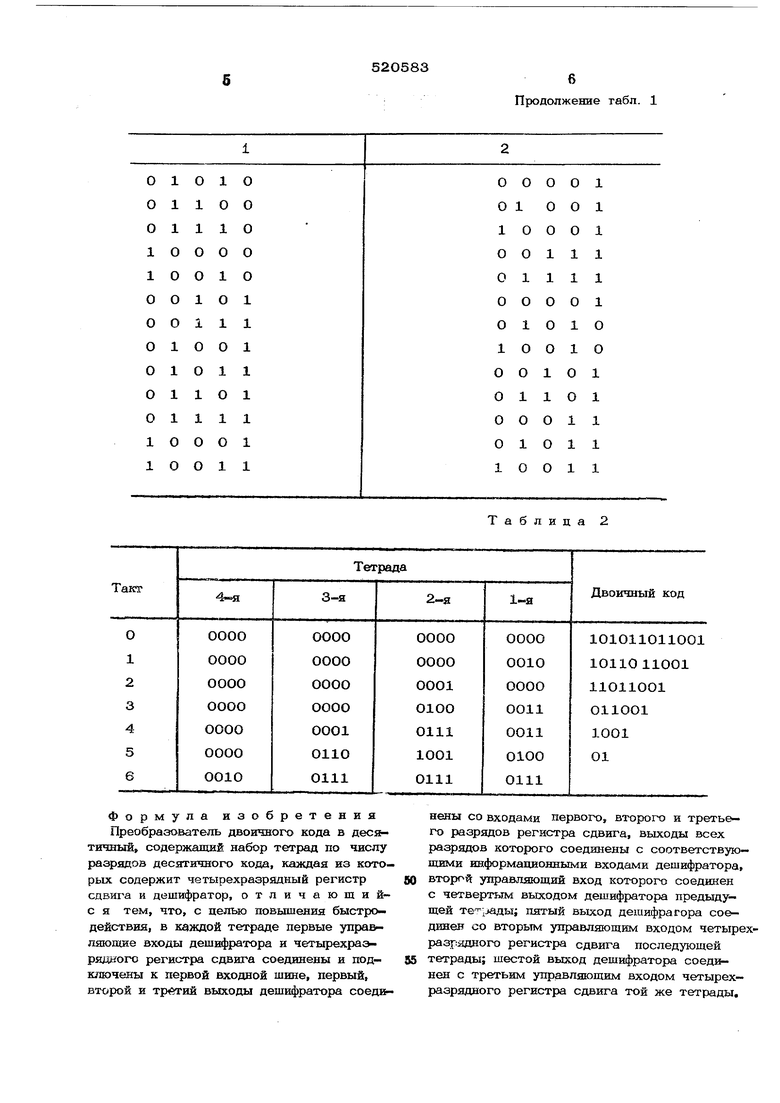

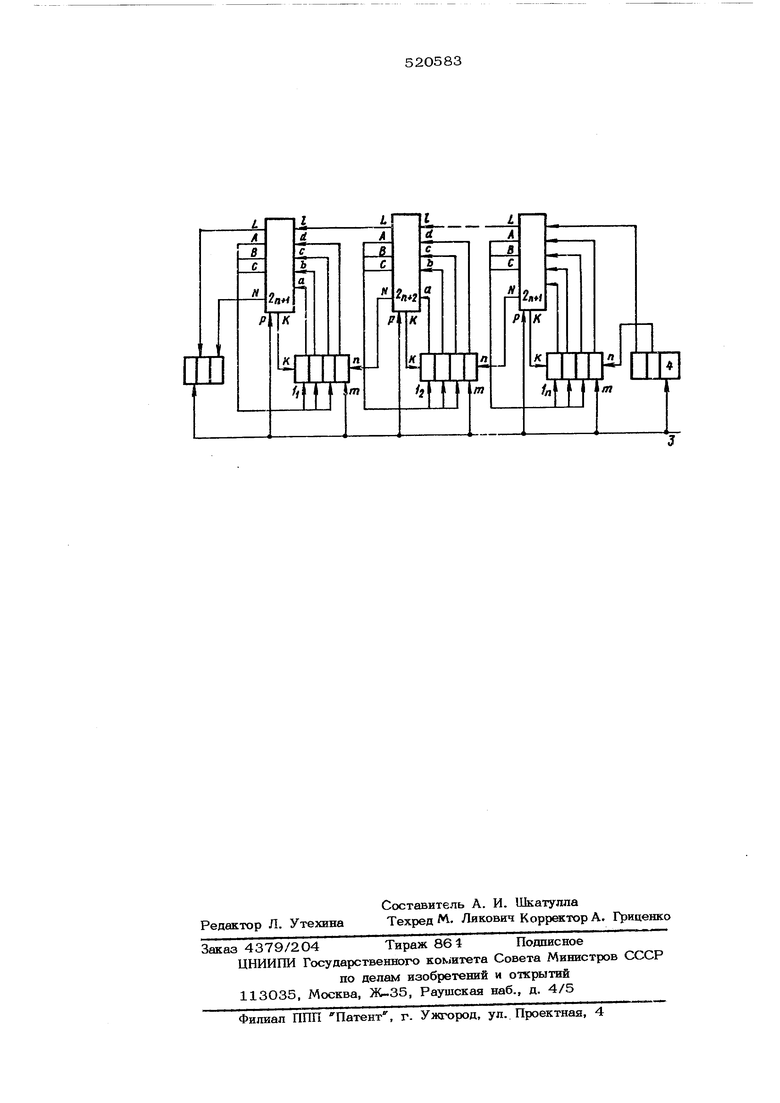

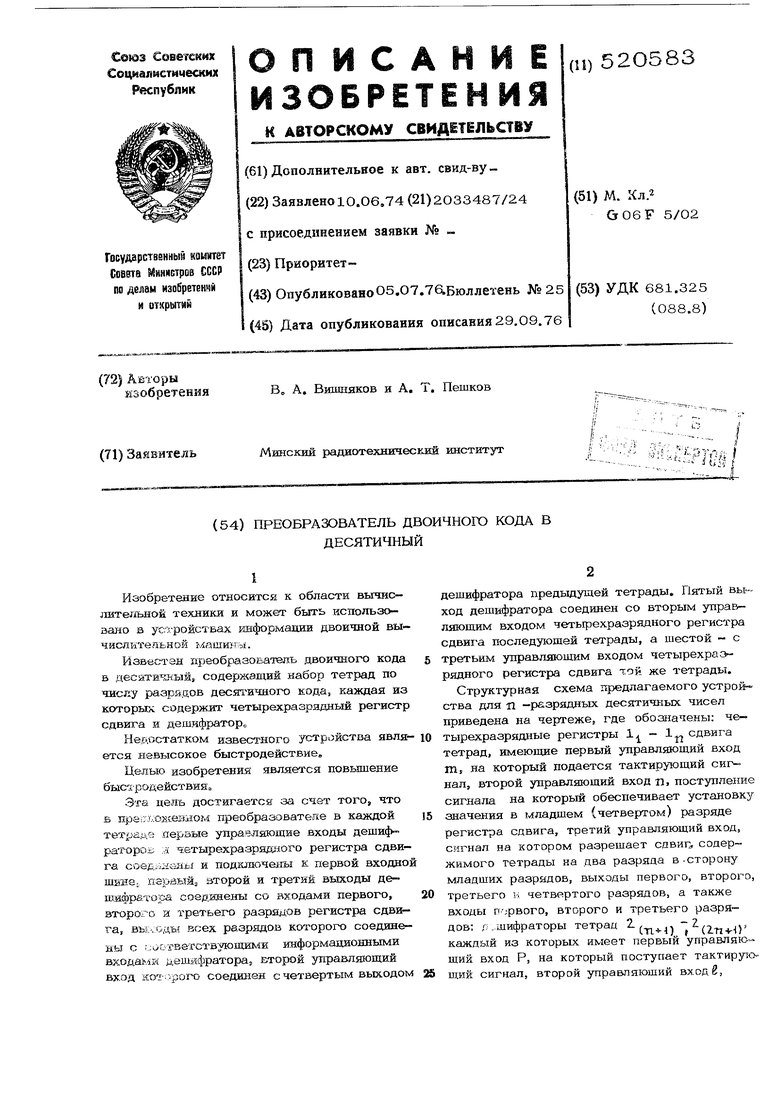

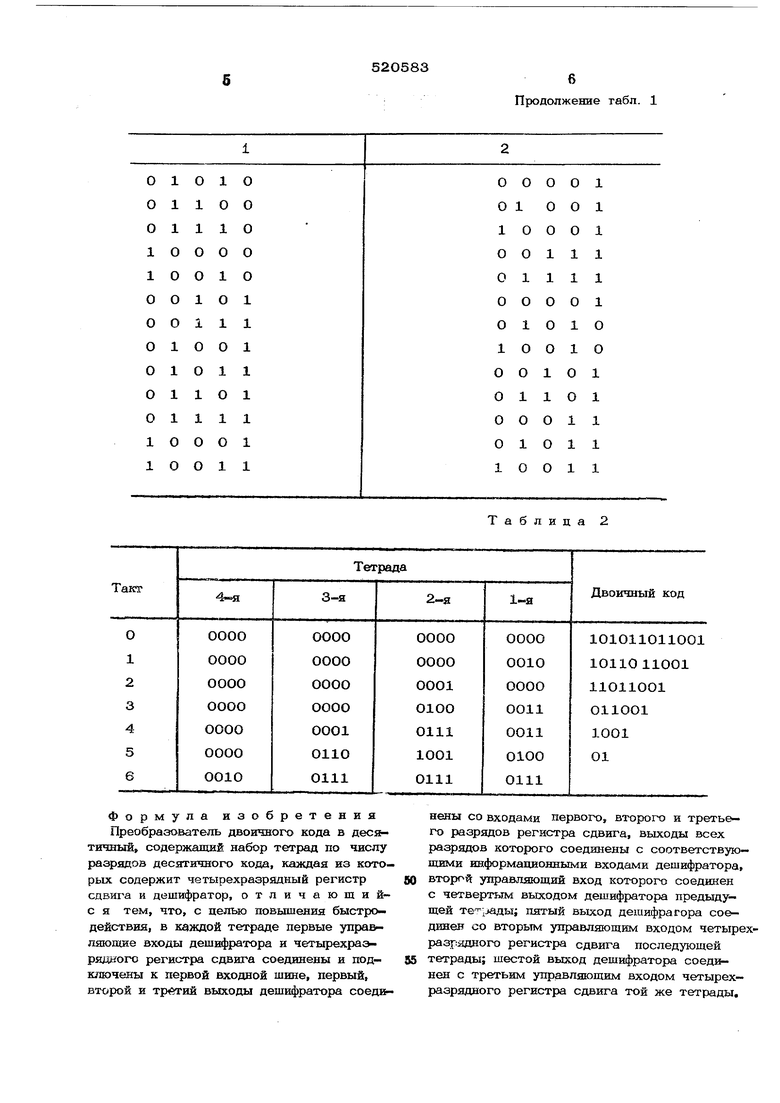

четыре информационных входа О-, bt С и 3, подключенные к соответствующим выходам разрядов регистра сдвига этой же тетрады, первый А второй В и третий С выходы, подключенные к первому, второму и третьему входам четырехразрядного регистра сдвига этой же тетрады, четвертый выход , подклю ченный ко второму управляющему входу дешифратора соседней слева (старщей) тетрады пятый выход , подключенный ко второму управляющему входу регистра сдвига соседней слева тетрады, и шестой выход , подключенный к третьему управляющему входу регистра сдвига этойже тетрады; первая входрегистра сдвига этойже тетрады; первая вход„ная шина 3, подключенная к первым входам де„шифраторов и четырехразрядных регистров сдвига всех тетрад, по которой подается тактирующий сигнал и регистр 4 исходного двоичного кода. Устройство работает следующим образом, В исходном состоящий во всех разрядах регистров сдвига тетрад устанавливает ся нулевой код, в регистре 4 - преобразуемый двоичный код. Преобразователь работает потактно по сигналам шины и выполняет полное преобразование за М/2 тактов (где М - разр$здность исходного двоичного числа). В каждом такте в зависимости от сигналов на входах 6, U, 1), С , d, дешифраторы на своих выходах по сигналу на входе Р вы рабатывают или сигнал разрешения сдвига на два разряда (сигнал на выходе К), или сигналы на выходах А, В, С для установки соответствующего кода в трех старших разрядах регистра той же тетрады. Кроме этого, дешифраторы вырабатывают на своих вьь ходах сигналы переноса в соседнюю старшую тетраду (сигнал переноса 2 на выходе L и сигнал переноса на выходе N X Выработка сигналов на выходе дешифратора в зависимости от сигналов на его вхо дах производится следующим образом. Если в регистре данной тетрады зафиксированы коды ОООО, ООО1, ОО1О и в последнем случае нет переноса 2 из соседней младшей тетрады, то в данной тетраде разрешается сдвиг кода регистра на два разряда влево по сигналу на выходе К дешифратора. Если в тетраде зафиксированы коды ООН, 0100, 0101, ОНО, 0111, 100О, 1001, то запрещается сдвиг в данной тетраде и происходит коррекция кода последней и формируются переносы в старшую тетраду. Запрет сдвига и коррекция кода регистра данной тетрады выполняется и тогда, когда на момент начала такта в регистре зафиксирован код ОО1О и в данную тетраду приходит перенос 2 (сигнал на выходе дешифратора) из младшей тетрады, В таблице 1 представлены выходные сигна.. .. - „ лы, формируемые дешифратором тетрады при f fj t речди различных комбинациях сигналов на его вхоПЯЯЛИТИТчГГ ТСПМПИНЯ nwcnr гчггЯагтпп ттп QT-U-I „ де. При этом перенос образуется при п&редаче десятка из данного десятичного ра&. ряда в старшей, перенос 2 образуется при передаче двух десятков, при передаче трех десятков из данного десятичного разряда образуются одновременно перенос 2 и пе ренос 1 в следующий разряд (сигналы с выходов L и К дешифратора данной тетрады, поступающие в соседнюю старшую тетраду). При коррекции младший разряд регистра тетрады устанавливается в соответствующее состояние парафазным сигналом Я, поступающим из соседней тетрады. На основании приведенной таблицы можно составить следующие функции зависимости выходов дешифратора входных сигналов А ad& V Dcde V 1эс d& B a-devaae V t-dlvaBdevt)c3 С « ae V tcdC V cde V бе vbest L a V fed V be К b vcd vcde Для более наглядной иллюстрации работы преобразователя в таблице 2 приведены промежуточные значения в тетрадах преобразователя на отдельных тактах преобразо- вания двоичного кода lOlOllOllOOlp . Таким образом после выполнения шести тактов бутет преобразовано двенадцатиразрядное двоичное число. Таблица 1

Продолжение табл. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1973 |

|

SU517890A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

Формула изобретения Преобразователь двоичного кода в дес5 тичный, содержащий набор тетрад по числу разрядов десятичного кода, каждая из которых содержит четырехразрядный регистр сдвига и дешифратор, отличающийс я тем, что, с целью повышения быстродействия, в каждой тетраде первые управляющие входы дешифратора и четырехра рядного регистра сдвига соединены и подключены к первой входной шине, первый, второй и третий выходы дешифратора соедвн

Таблица 2

нены со входами первого, второго и третьего разрядов регистра сдвига, выходы всех разрядов которого соединены с соответствующими информационными входами дешифратора,

второй управляющий вход которого соединен с четвертым выходом дешифратора предыдущей Te-j iJaMH; пятый выход дешифратора соединен со вторым управляющим входом четырехразрядного регистра сдвига последующей

тетрады; шестой выход дешифратора соединен с третьим управляющим входом четырехразрядного регистра сдвига той же тетрады.

Авторы

Даты

1976-07-05—Публикация

1974-06-10—Подача