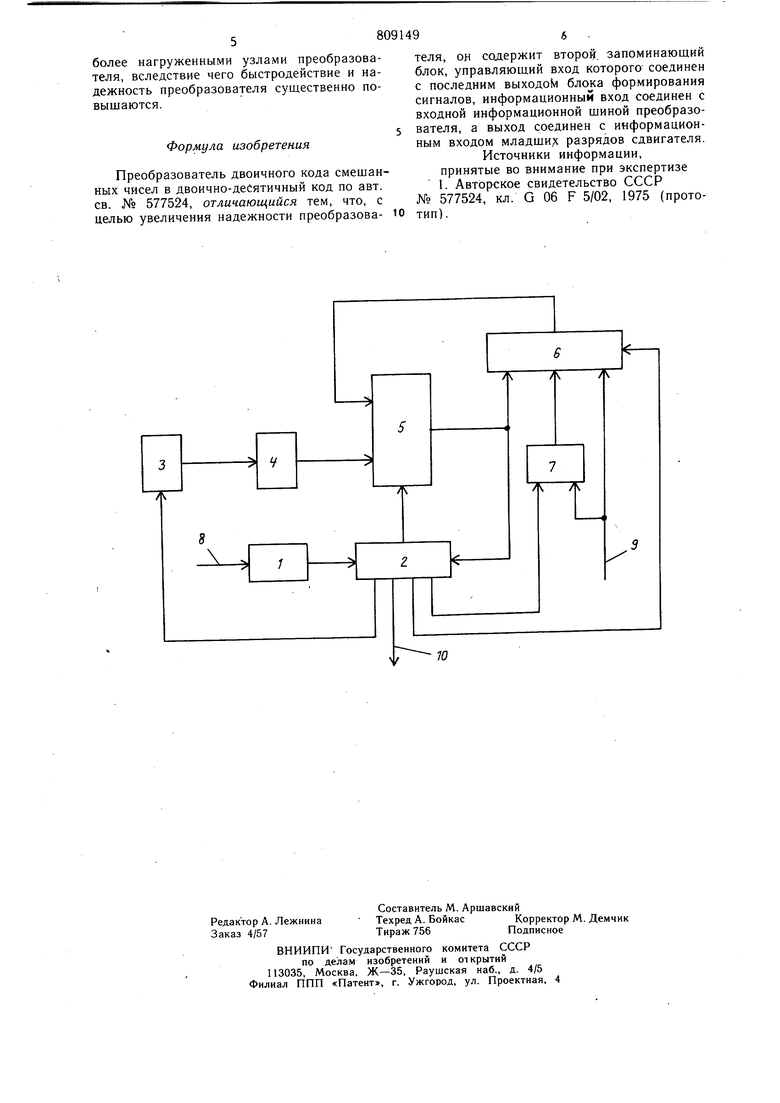

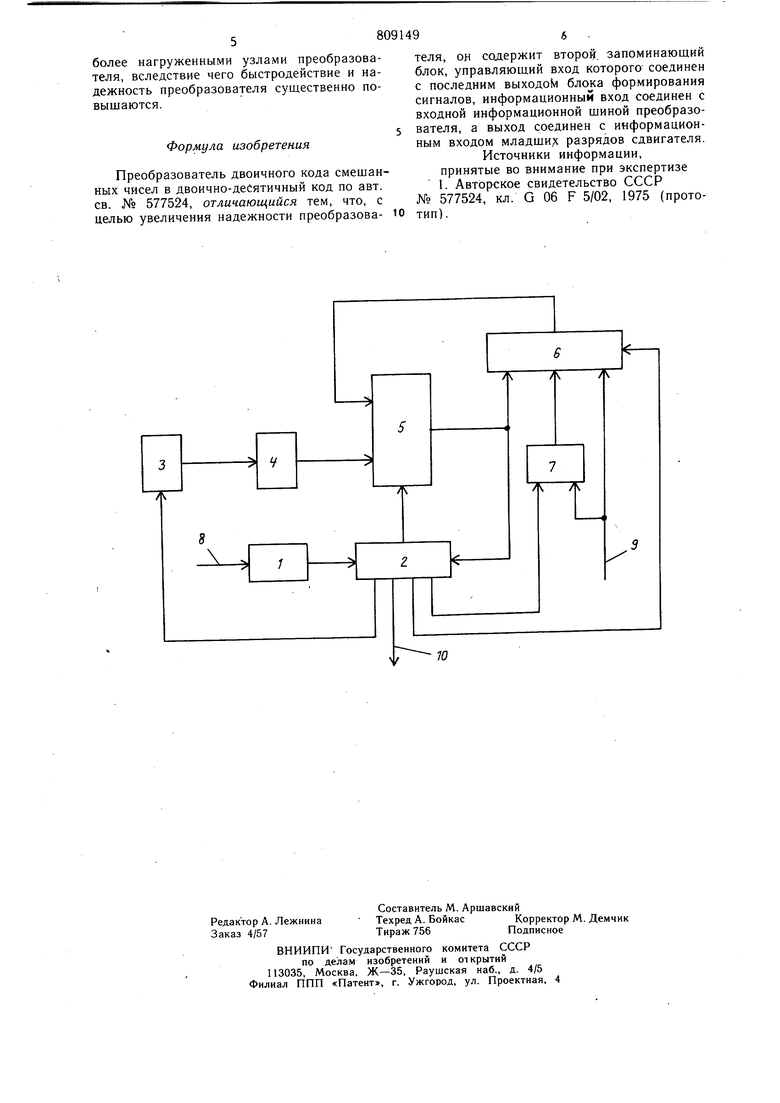

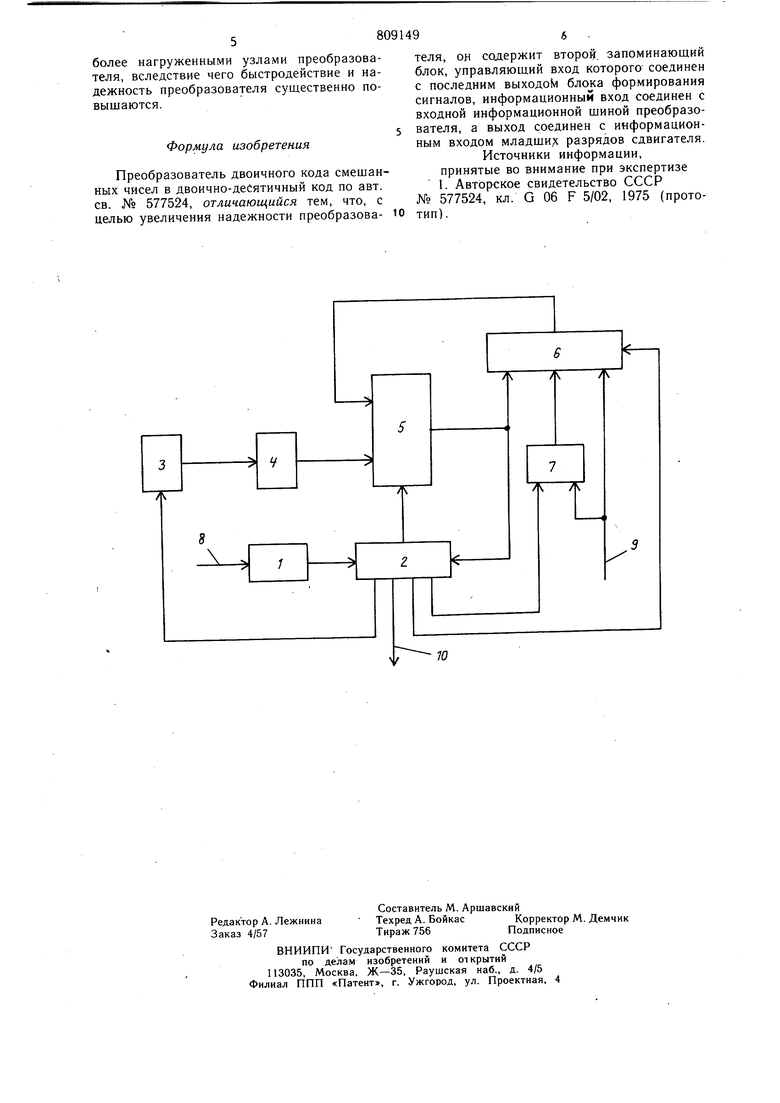

(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА СМЕШАННЫХ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД онным входом младших разрядов сдвигателя. На чертеже представлена структурная схема преобразователя двоичного кода, смешанных чисел в двоично-десятичный код. Предлагаемый преобразователь содержит блок 1 управления, блок 2 формирования сигналов, переключатель 3 эквивалентов, первый запоминающий блок 4, сумматор-вычитатель 5, сдвигатель 6, второй запоминающий блок 7, входную управляющую щину 8, входную информационную щину 9, выходную информационную тину 10. Преобразователь работает следующим образом. По входной информационной щине 9 на вход сдвигателя 6 поступает двоичный код целой части переводимого смешанного числа, а на вход запоминающего блока 7 - дробная часть переводимого числа. Одновременно на шину 8 подается управляющий импульс, который запускает в работу блок 1 управления, вырабатывающий импульсы, необходимые для автономного функционирования преобразователя. Управляющие импульсы с выхода блока 2 записывают в запоминающий блок 7 дробную часть подаваемого числа и одновременно пропускают через сдвигатель 6 целую часть числа на вход сумматора-вычитателя 5 без сдвига двоичного кода. В то же время в первом такте преобразования управляющий импульс от блока 2, пройдя через переключатель эквивалентов 3, поступает в запоминаюший блок 4, который содержит двоичные эквиваленты десятичных чисел вида, ( )э, где I - число десятичных разрядов целой части переводимого числа, т 1,2,3... (k-1), k; а k - обшее число десятичных разрядов переводимого числа. Количество двоичных эквивалентов определяется принятой разрядностью десятичных чисел. Преобразование осушествляется методом деления переводимого числа (а в дальнейшем остатков) без восстановления остатка на свой двоичный эквивалент при нахождении каждой двоично-десятичной тетрады. Под действием управляюшего импульса из блока 4 считывается соответствующий эквивалент (в начале преобразования старший, т.е. ), двоичный параллельный код которого поступает на вход сумматора-вычитателя 5 и служит при нахождении данной тетрады делителем. Делимым же служит поступивший на другой вход сумматора-вычитателя 5 двоичный параллельный код входной информации (в дальнейшем делимым является предыдуший остаток). Блок 2 разрешает в первом такте преобразования вычитание делителя из делимого в сумматоре-вычитателе 5, откуда на вход сдвигателя 6 поступает код полученного частичного остатка, знаковый разряд которого поступает также в блок 2 для формирования кода двоично-десятичной тетрады и определения необходимости вычитания или сложения в следующем такте преобразования. При этом, если по анализу знакового разряда сумматора-вычитателя 5 частичный остаток-отрицателен, то блок 2 выдает на выходную информационную шину 10 в виде очередной цифры двоично-десятичной тетрады «О и подготавливает в сумматоре-вычитателе 5 цепи сложения для следующего такта преобразования, а если частичный остаток положителен, то на выходную щину 10 выдается «1, а в следующем такте производится вычитание делителя из делимого. В следующих тактах определения данной двоично-десятичной тетрады делимое, т.е. предыдущий частичный остаток, передается через сдвигатель 6 на вход сумматора-вычитателя 5 со сдвигом кода на один двоичный разряд в сторону старщих разрядов, делитель остается прежним. После нахождения всех цифр двоично-десятичной тетрады, т.е. выполнения четырех тактов, в случае отридательного остатка производится восстановление положительного остатка в дополнительном такте путем прибавления в сумматоре-вычитателе 5 того же делителя к отрицательному остатку. Для нахождения последующих двоично-десятичных тетрад пе реключатель 3 эквивалентов переводится под воздействием сигналов блока 2 на выборку из запоминающего блока 4 следующих по порядку (меньших по величине) эквивалентов, которые берутся новыми делителями, в качестве делимых берутся предыдушие положительные остатки и выполняется порядок вышеописанных действий определения кода каждой тетрады. При переходе к переводу дробной части числа предыдущий остаток становится равным нулю, а на вход сумматора-вычитателя 5 поступает из запоминающего блока 7 в первом такте определения данной двоично-десятичной тетрады код числа, сдвинутый в сдвигателе б на 3-С разряда в сторону старших разрядов. и определяются аналогично вышеописанному тетрады дробной части числа. Процесс преобразования повторяется до тех пор, пока не будут найдены все десятичные разряды числа. Предлагаемый преобразователь при преобразовании п-разрядного двоичного кода смещанных чисел в двоично-десятичный код позволяет уменьшить разрядность узлов преобразователя и находящихся в обращении операндов до значения п-(Зч-4)Ц или п-(3-7-4) g, где g - число десятичных разрядов дробной части переводимого числа. Сокращение длины операндов позволяет уменьшить прежде всего возможность появления ошибки в вычислениях, повысить помехоустойчивость аппаратуры, а также сократить разрядность таких узлов преобразователя, как сумматор-вычитатель и сдвигатель, работающих в непрерывном динамическом режиме в процессе производства преобразований, т.е. являющихся наиболее нагруженными узлами преобразователя, вследствие чего быстродействие и надежность преобразователя существенно повышаются. Формула изобретения Преобразователь двоичного кода смешанных чисел в двоично-дебятичный код по авт. св. № 577524, отличающийся тем, что, с целью увеличения надежности преобразователя, он содержит второй, запоминающий блок, управляющий вход которого соединен с последним выходов блока формирования сигналов, информационный вход соединен с входной информационной щиной преобразователя, а выход соединен с информационным входом младших разрядов сдвигателя. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 577524, кл. G 06 F 5/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1975 |

|

SU577524A1 |

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1976 |

|

SU714391A2 |

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Авторы

Даты

1981-02-28—Публикация

1978-04-18—Подача