УСТРОЙСТВО для УПРАВЛЕНИЯ ОБЩИМИ ДАННЫМИ

(54) ПАРАЛЛЕЛЬНЫХ ПРОЦЕССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обучения операторов автоматизированных систем управления | 1985 |

|

SU1257692A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для контроля электрического монтажа | 1989 |

|

SU1698843A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для управления блоками памяти | 1976 |

|

SU636676A1 |

Изобретение относится к вычислительной технике .

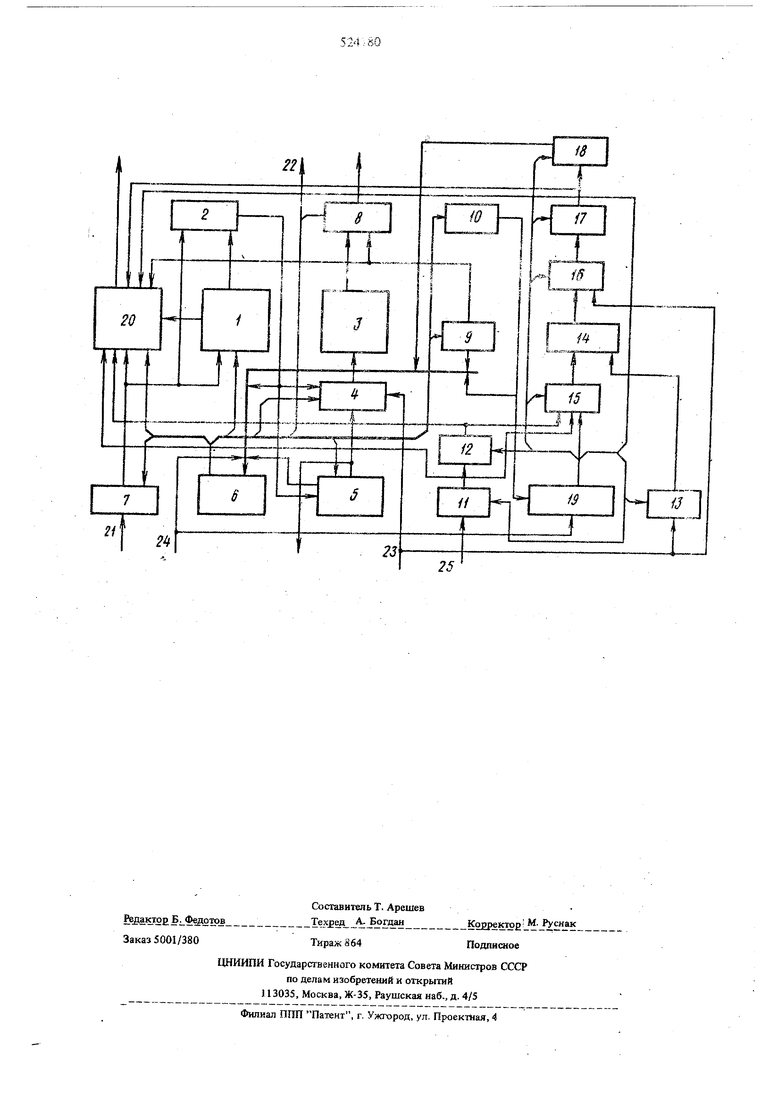

Известны устройства для управления общими данными параллельных процессов, содержаише регистр адреса, регистр данных, блок памяти данных, коммутатор памяти, блок задания очередности использования ячеек памяти, блок индикаторов состояний ячеек памяти, блок управления, блок адресных регистров, блок сравнения адресов, входы которого соединены соответственно с выходом регистра адреса и первым выходом блока адресных регистров, выход соединен со входной шиной блока управления, со входами коммутатора памяти и блока задания очередности использования ячеек памяти, выход которого подключен к выходу устройства и через коммутатор памяти-ко входу блока памяти данных, выход которого соединен с первым входом регистра данных, второй вход которого подключен к выходу блока индикаторов состояний ячеек памяти, управляющие вход и выход которого соединены соответственно с выходной и входной шинами блока управления, выход регистра адреса подключен ко входу блока адресных регистров, вход соединен с адресным входом устройства, первый информационный вход и информационный выход устройства соединены соответстве1шо с информационным входом коммутатора памяти и выходом регистра данных, управляющие входы регистра данных, регистра адреса, блока адресных

5 регистров, коммутатора памяти, блока зада{шя очередности использования ячеек памяти и управляющий выход устройства соединены с выходной щиной блока управления, входная щина которого соединена с управляющим входом устройства и выходом блока 0 очередности использования ячеек памяти. В известном устройстве содержится оборудование управления быстродействующими блоками памяти (ассоциативными запоминающими блоками), входящими в состав вычислительных маишн системы и 6 связанными с основной памятью. К быстродействующим блокам памяти обращаются либо в математических, либо в физических адресах; для хранения адресов данных, находящихся в этих блоках памяти, применяются ассоциативные регистры. Когда одна из мащин записьшает информацию в основную память, устройство проверяет наличие инфор мации с тем же адресом в ячейках блоков памяти остальных .машин и исключает возможность обраще{шя к этим ячейкам до тех пор, пока в 1шх не

8 будет записана новая информация из основной

Составитель Т. Арешев

Ревакто Б Ф отовТехред.А; гданКорректор М- Уснак

Заказ 5001/380Тираж 864Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 lOB фавнения, но, кроме этого, он используется для дублирования регистра 13 при приеме кода времени. Содержимое регистра 17 передается в блок 20 для формирова1Шя контрольных разрядов и проверки результатов сравнений в блоке 14, Данные, записьшаемые в блок памяти Зи считьшаемые из него, сопровождаются контрольными разрядами по модулю три, а считанные данные проверяются в приемнике этих данных, например в арифметическом блоке. При выполнении записи контролируется состояние индикатора в бпоке 9, соответствующего той ячейке, в которую идет запись. Если этот индикатор находится в единичном состоянии, в блоке 20 формируется сигнал ошибки. Для выполнения данного вида проверки выходы всех индикаторов блока 9 соединены со входами блока контроля 20. Формула изобретения Устройство для управления общими данными параллельных процессов; содержащее регистр адреса, регистр данных, блок памяти данных, коммутатор памяти, блок задания очередности использования ячеек памяти, блок индикаторов состояний ячеек памяти, блок управления, блок адресных регистров, блок сравнения адресов , входы которого соединены соответственно с выходом регистра адреса и первым выходом блока адресных регистров, выход соеданен со входной шиной блока управления, со входами коммутатора памяти и блока задания очередности использования ячеек памяти, выход которого подключен к выходу устройства и через коммутатор памяти - ко входу блока памяти данных, выход которого соединен с первым входом регистра данных, второй вход которого подключен к выходу блока индикаторов состояний ячеек памяти, управляющие вход и выход которого соединены соответственно с выходной и входной шинами блока управления, выход регистра адреса подключен ко входу блока адресных регистров, вход соединен с адресным входом устройства, первый информационный вход и информационный выход устройства соединены соответственно с информационным входом коммутатора памяти и выходом регистра данных, управляющие входы регистра данных, регистра адреса, блока адресных регистров, коммутатора памяти, блока задания очередности использования ячеек памяти и управляющий выход устройства соединены с выходной щиной блока управления, входная шина которого соединена с управляющим входом устройства и выходом блока очередности использования ячеек памяти, о т л к а ю щ е е с я тем, что, с целью повышения произзсдктельности, в него введены регистры кода времени, блоки коммутаций, буферный регистр, форм)рователь, распределитель тактовых сигналов, выходы которого подключены к управляющим входам введенных блоков, регистров и формирователя, блок указателей обращений к ячейкам памяти и блок сравнения кодов времени, первьш вход которого через первый блок .коммутации соединен с выходами первого и второго регистров кода времени, второй вход- с выходом третьего регистра кода времени, выход- через последовательно соединенные второй блок коммутации, буферный регистр и формирователь соединен со входной шиной блока управления, второй информационный вход устройства подключен ко входу первого регистра кода |Времени., выход которого подключен ко входу второго регистра кода времени, первый информационный вход устройства соединен со входами третьего регистра кода времени и второго блока коммутации, выход блока указателей обращений к ячейкам памяти подключен к первому управляющему входу распределителя тактовых сигналов и ко входной шине блока ттравления, выходная тина которого соединена со входом блока указателей обращений к ячейкам памяти, второй управляющий вход распределителя тактовых сигналов подключен к управляющему входу устройства.

Авторы

Даты

1976-08-05—Публикация

1974-12-30—Подача