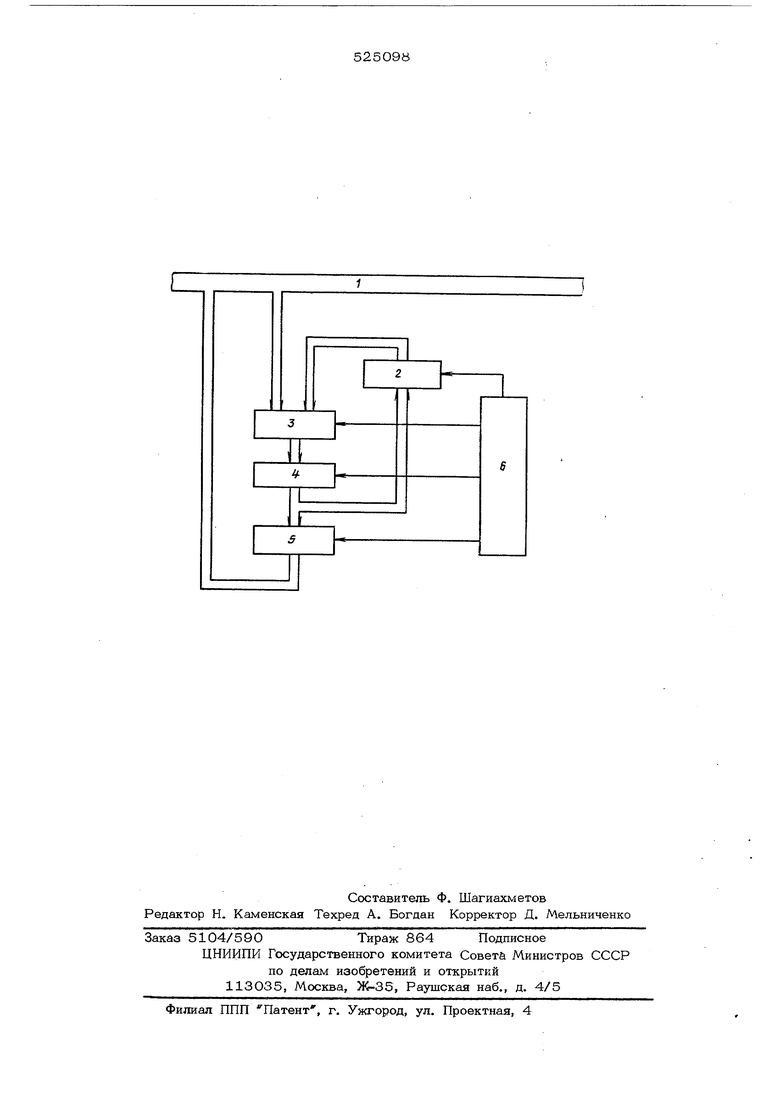

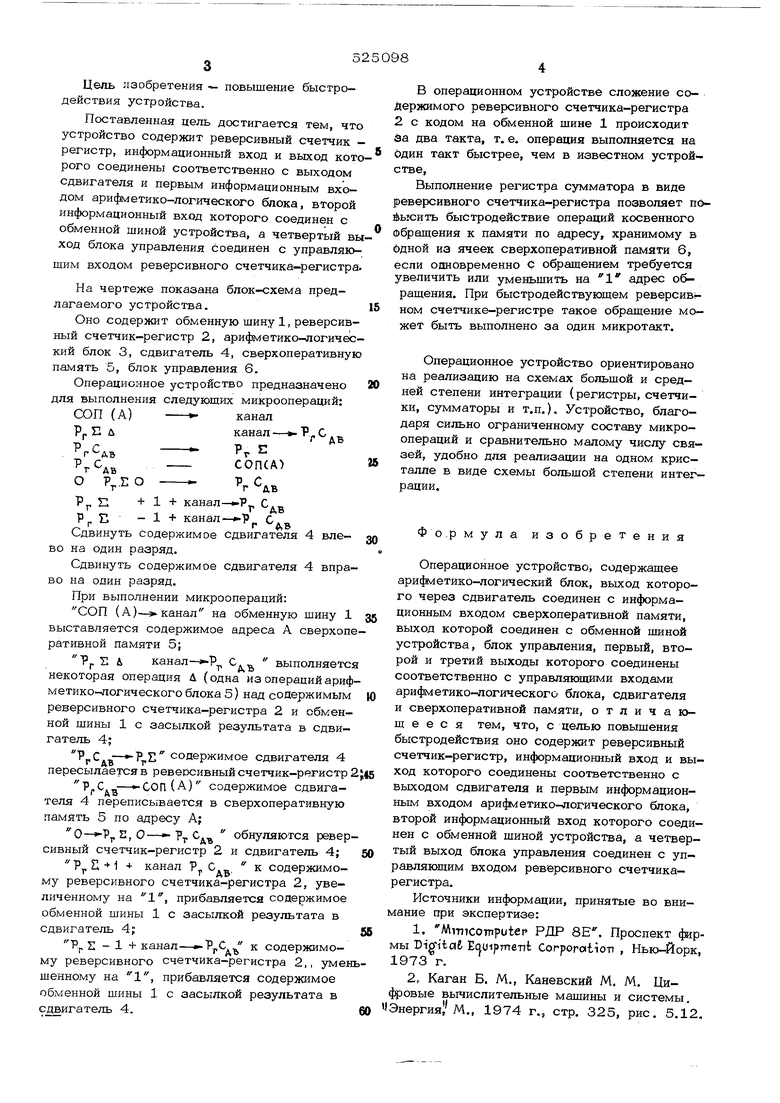

(54) ОПЕРАЦИОННОЕ УСТРОЙСТВО Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, чт устройство содержит реверсивный счетчик регистр, информационный вход и выход кот рого соединены соответственно с выходом сдвигателя и первым информационным входом арифметико-логического блока, второй информационный вход которого соединен с обменной шиной устройства, а четвертый в ход блока управления соединен с управляю щим входом реверсивного счетчика-регистра На чертеже показана блок-схема предлагаемого устройства. Оно содержит обменную шину 1, реверсивный счетчик-регистр 2, арифметико-логичес кий блок 3, сдвигатель 4, сверхоперативную память 5, блок управления 6. Операционное устройство предназначено для выполнения следующих микроопераций: СОП (А) канал РрС U канал -I Е СОП(А) + 1 + канал- 1 + каналСдвинуть содержимое сдвигателя 4 влево на один разряд. Сдвинуть содержимое сдвигателя 4 во на один разряд. При выполнении микроопераций: СОП (А)-. канал на обменную шину адреса А сверхоп выставляется содержимое ративной памяти 5; Рр Е Л канал- -Р С выполняетс некоторая операция Д (одна из операций ариф метико-логического блока 5) над содержимым реверсивного счетчика-регистра 2 и обменной шины 1 с засылкой результата в сдвигатель 4; Р с Е содержимое сдвигателя 4 пересылается в реверсивный счетчик-регистр PC (А) содержимое сдвигателя 4 переписывается в сверхоперативную память 5 по адресу А; обнуляются ревер ,2,02 и сдвигатель 4; сивный счетчик-регистр к содержимо+ канал му реверсивного счетчика-регистра 2, увеличенному на 1, прибавляется содержимое обменной шины 1 с засылкой результата в сдвигатель 4; Р|, S - 1 + канал- -РрС к содержимому реверсивного счетчика-регистра 2,, уме шенному на 1, прибавляется содержимое обменной шины 1 с засылкой результата в сдвигатель 4, В операционном устройстве сложение соержимого реверсивного счетчика-регистра с кодом на обменной шине 1 происходит а два такта, т.е. операция выполняется на - быстрее, чем в известном устройВыполнение регистра сумматора в виде еверсивного счетчика-регистра позволяет поысить быстродействие операций косвенного бращения к памяти по адресу, хранимому в дной КЗ ячеек сверхоперативной памяти 6, спи опновременно О обращением требуется величить или уменьшить на 1 адрес обращения. При быстродействующем реверсив-ном счетчике-регистре такое обращение может быть выполнено за один микротакт. Операционное устройство ориентировано на реализацию на схемах больщой и средней степени интеграции (регистры, счетчики, сумматоры и т.п.). Устройство, благодаря сильно ограниченному составу микроопераций и сравнительно малому числу связей, удобно для реализации на одном кристалле в виде схемы большой степени интеграции. Фо.рмула изобретения Операционное устройство, содержащее арифметико-логический блок, выход которого через сдвигатель соединен с информационным входом сверхоперативной памяти, выход которой соединен с обменной шиной устройства, блок управления, первый, второй и третий выходы которого соединены соответственно с управляющими входами арифметико-логического блока, сдвигателя и сверхоперативной памяти, о т л и ч а ю- щ е е с я тем, что, с целью повышения быстродействия оно содержит реверсивный счетчик-регистр, информационный вход и выход которого соединены соответственно с выходом сдвигателя и первым информационHbuv входом арифметико-логического блока, второй информационный вход которого соединен с обменной шиной устройства, а четвертый выход блока управления соединен с управляющим входом реверсивного счетчикарегистра. Источники информации, принятые во вниание при экспертизе: 1, MiTJicoTHputep РДР SE. Проспект фирмы Dig-itafc Eauipment Corpopatio-n , Нью-Йорк, 1973 г. 2, Каган Б. М., Каневский М. М. Цифровые вычислительные машины и системы. Энергия М., 1974 г., стр. 325, рис. 5.12,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Устройство обработки данных процессора | 1988 |

|

SU1647584A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для сопряжения эвм с периферийной системой | 1984 |

|

SU1246104A1 |

| Оперативное запоминающее устройство | 1978 |

|

SU788173A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Авторы

Даты

1976-08-15—Публикация

1974-09-30—Подача