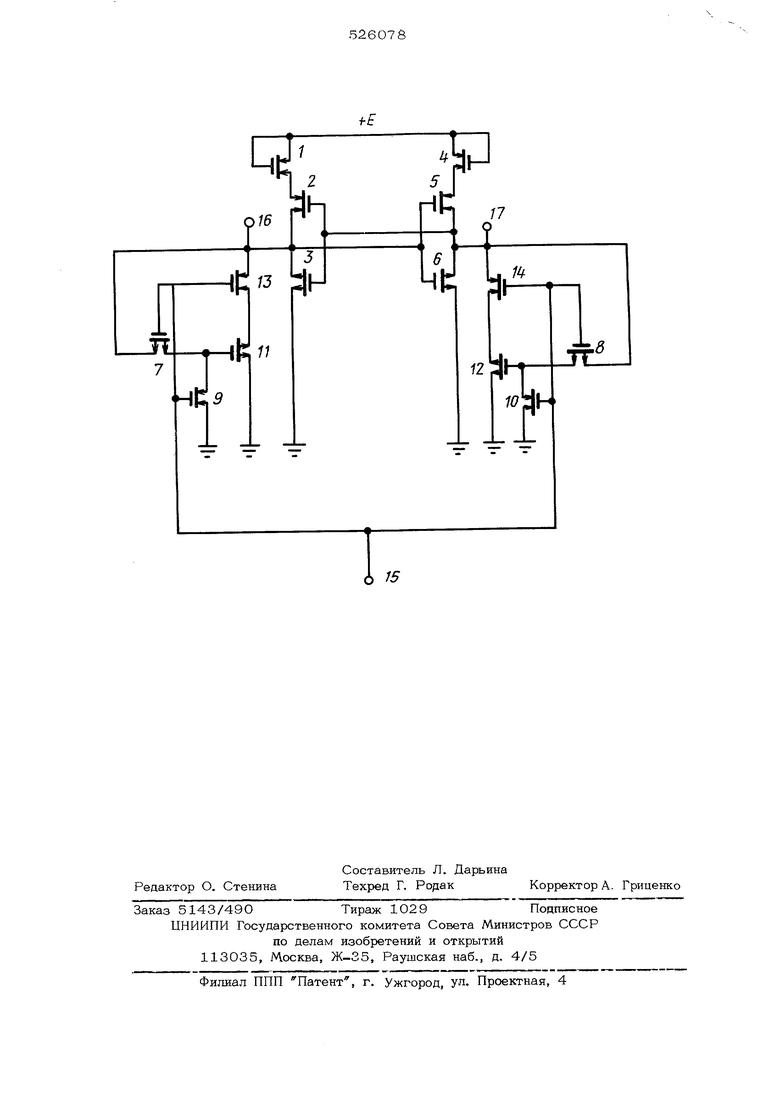

последовательно с транзистором 12, сток транзистора 7 соединен с затвором транзистора 11 и истоком транзистора 9, сток тра зистора 8 - с затвором транзистора 12 и истоком транзистора 10, стоки транзисторов 9, 10 и истоки транзисторов 11, 12 подключены к общей тине, а затворь; транзисто ров 7-10, 13 и 14 объединены и подключены к счетном.у входу 15 триггера. Триггер работает следующим образом. Допустим, что в исходном состоянии на выходе 16 триггера высокий уровень (логическая единица), на выходе 17 - низкий (логический нуль). При поступлении положительного импульса на счетный вход 15 триг гера транзистор 7 открывается и передает уровень логической единицы на затвор транзистора 11 и заряжает емкость затвора последнего, а транзистор 9 и транзистор 13 закрыты уровнем логической единицы на затворе. На другом плече триггера, несмотря на открывание транзистора 8, транзистор 12 не открывается, так как с выхода 17 на загвор транзистора 12 поступает нулевой уровень. Во время действия счетного импульса это состояние схемы, сохраняется без изменения После окончания действия счетного пульса закрывается транзистор 7 и открывакл ся транзисторы 9 и 13. Во время разряда емкости затвора транзистора 11 через транзистор 9 создается такое положение, когда одновременно открыты транзистор 13 и транзистор 11. При этом на выходе 16 формируется нулевой уровень, который через обратную связь формирует на выходе 17 высокий уровень, который через обратную связь обеспечивает формирование нулевого уровня .на выходе 16, т. е. триггер переключается в устойчивое состояние, при котором на вы ходе 16 : огический нуль, а на выходе 17 логическая единица. При поступлении второго счетного импульса триггер переключается в противоположное устойчивое состояние, причем последовательность срабатывания транзисторов правого плеча триггера полностью соответствует рассмотренной последовательности срабатывания транзисторов левого плеча. Формула изобретения Счетный триггер на дополняющих МДПтранзисторах, содержащий два симметричных плеча, выход каждого из которых соединен со входом другого плеча, и четыре управляющих транзистора в каждом плече, о т л ичаюшийс я тем, что, с целью упрощения устройства, выход каждого плеча соединен с истоком своего первого управляющего Т1-транзистора, сток которого подключен к истоку второго управляющего р -транзистора, третий управляющий тг -транзистор и четвертый управляющий р-транзистор включены последовательно, причем затвор третьего управляющего Tt -транзистора соединен со стоком первого управляющего п. -транзистора, исток четвертого управляющего р-транзистора соединен с выходом этого же плеча, затворы первого, второго и четвертого управляющих транзисторов обоих плеч объединены и подключены к счетному входу тригге ра, а исток третьего и сток второго управ- ляющих транзисторов подключены к общей шине. Источники информации, принятые во внимание при экспертизе: 1.Патент Англии № 1 341 156, НЗТ, 19.12.73. 2.Валиев К. А. и др. Цифровые интегральные схемы на МДП-транзисторах, 1971, с. 275, рис. 7.19 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Триггер с раздельными входами | 1978 |

|

SU746874A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

Авторы

Даты

1976-08-25—Публикация

1974-05-31—Подача