1

Изобретение относится к технике передачи дискретной информации и может использоваться в системах синхронизации приемников дискретной информации, в частности в устройствах фазирования по посылкам.

Известно усредняющее устройство с блокировкой для фазирования дискретной информации, содержащее многоразрядный реверсивный счетчик, один выход которого через триггер добавления подключен ко входу первого элемента И, а второй выход реверсивного счетчика через триггер вычитания подключен к входу второго элемента И, причем к дополнительным входам элементов И подключены соответствующие входы реверсивного счетчика.

Однако такое устройство характеризуется существенным ухудщением точности установления синхронизма при появлении значительных искажений краев посылок.

С целью повыщения помехоустойчивости устройства, промежуточный разряд вычитания реверсивного счетчика соединен с нулевым входом триггера добавления, а промежуточный разряд добавления реверсивного счетчика

соединен с нулевым входом триггера вычитания.

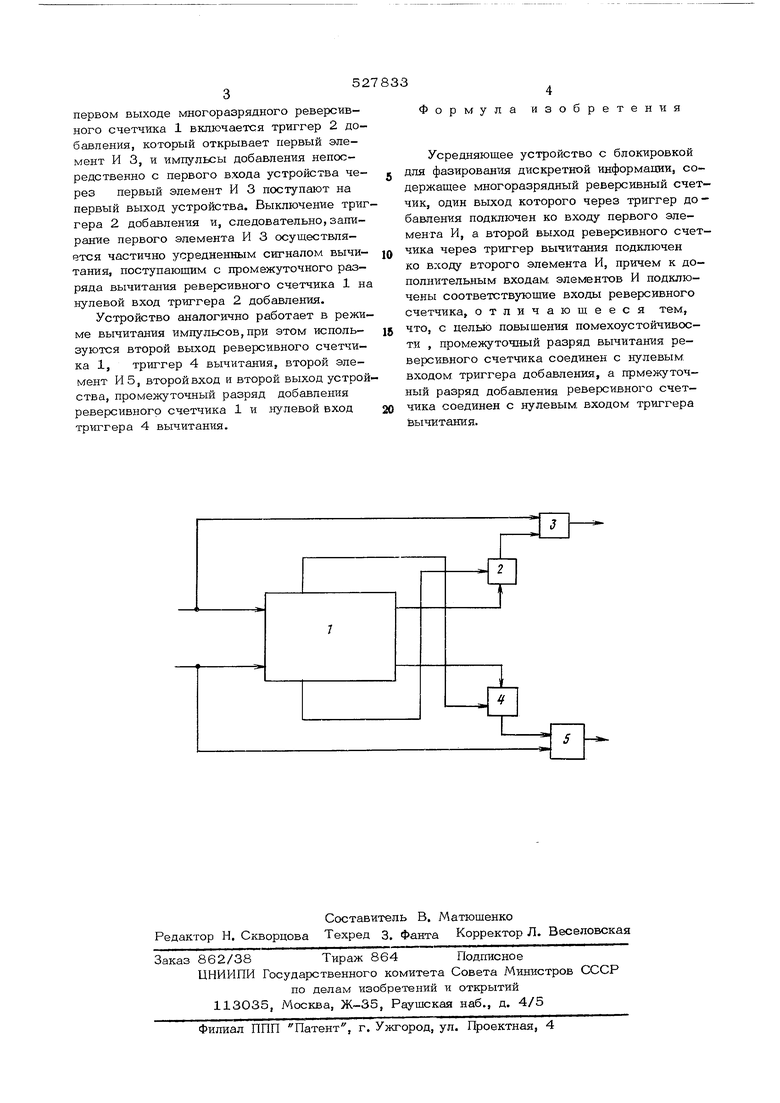

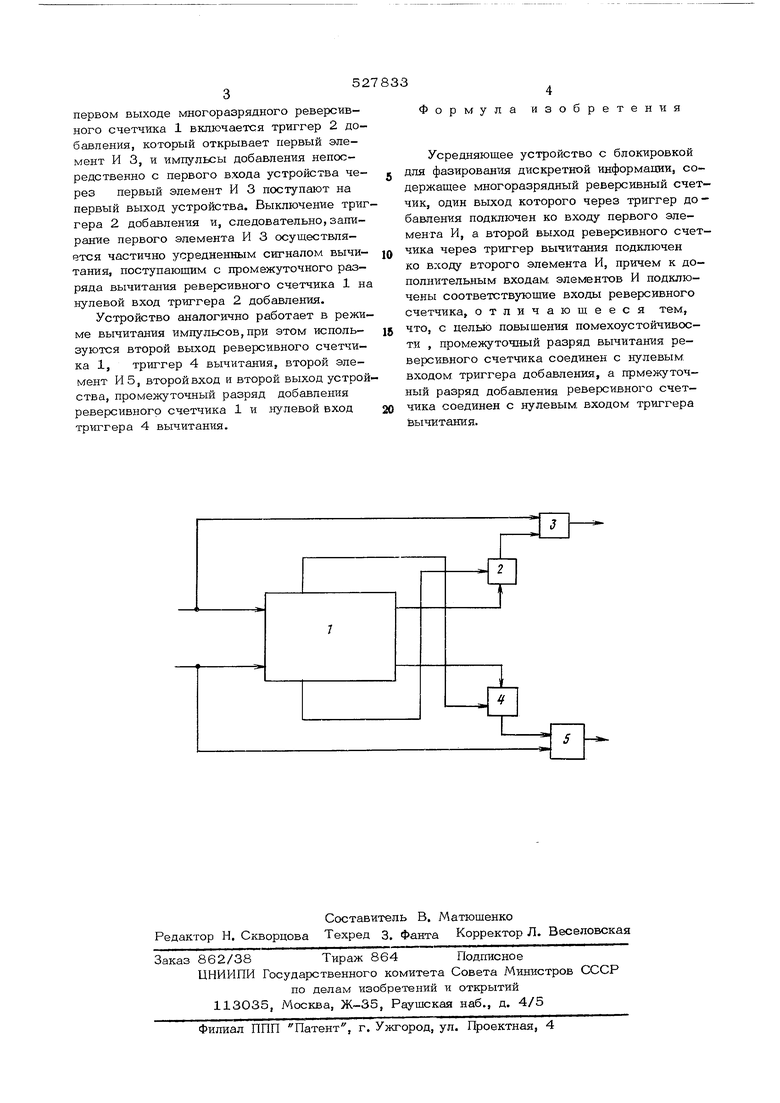

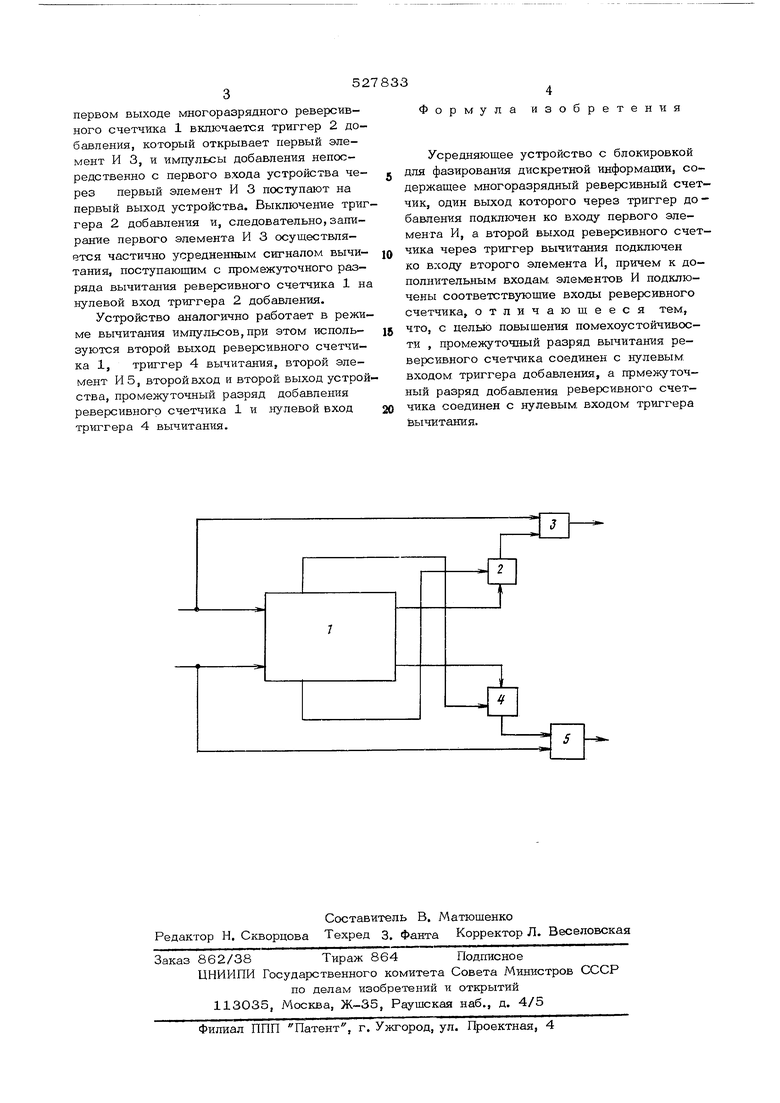

На чертеже приведена структурная электрическая схема усредняющего устройства с блокировкой для фазирования дискретной информвиии.

Устройство содержит многоразрядный реверсивный счетчик 1, один выход которого через триггер 2 добавления подключен ко входу первого элемента И 3, а второй выход реверсивного счетчика через триггер 4 вычитания подключен ко входу второго элемента И 5, причем к допол1ттельным входам элементов И 3 и 5 подключены соответствующие входы реверсивного счетчика 1; промежуточный разряд вычитания реверсивного счетчика 1 соединен с щлевым входом триггера 2 добавления, а промежуточный разряд добавления реверсивного счетчика 1 соединен с нулевым входом триггера 4 вычитания.

Усредняющее устройство с блокировкой для фазирования дискретной информации работает слещющим образом.

При появлении импульса добавления на первом выходе многоразрядного реверснвного счетчика 1 вкдючается триггер 2 добавления, который открывает первый элемент И 3, и импульсы добавления непосредственно с первого входа устройства через первый элемент И 3 поступают на первый выход устройства. Выключение триг гера 2 добавления и, следовательно, запирание первого элемента И 3 осуществляется частично усредненным сигналом вычитания, поступающим с промежуточного разряда вычитания реверсивного счетчика 1 н нулевой вход триггера 2 добавлентш. Устройство аналогично работает в режи ме вычитания импульсов, при этом используются второй выход реверсивного счетчика 1, триггер 4 вычитания, второй элемент И 5, второй вход и второй выход устрой ства, промежуточный разряд добавления реверсивного счетчика 1 и .нулевой вход триггера 4 вычитания. Формула изобретения Усредняющее устройство с блокировкой для фазирования дискретной информахши, содержащее многоразрядный реверсивный счетчик, один выход которого через триггер добавления подключен ко входу первого элемента И, а второй выход реверсивного счетчика через триггер вычитания подключен ко входу второго элемента И, причем к дополнительным входам, элементов И подключены соответствующие входы реверсивного что, с целью повышения помехоустойчивости , пром.ежуточный разряд вычитания реверсивного счетчика соединен с нулевым входом триггера добавления, а прмежуточный разряд добавления реверсивного счетчика соединен с нулевым, входом триггера Вычитания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усредняющее устройство с блокировкой для фазирования дискретной информации | 1980 |

|

SU896785A2 |

| Усредняющее устройство с блокировкой | 1981 |

|

SU978380A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1529466A1 |

| Усредняющее устройство | 1978 |

|

SU773947A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

Авторы

Даты

1976-09-05—Публикация

1974-06-24—Подача