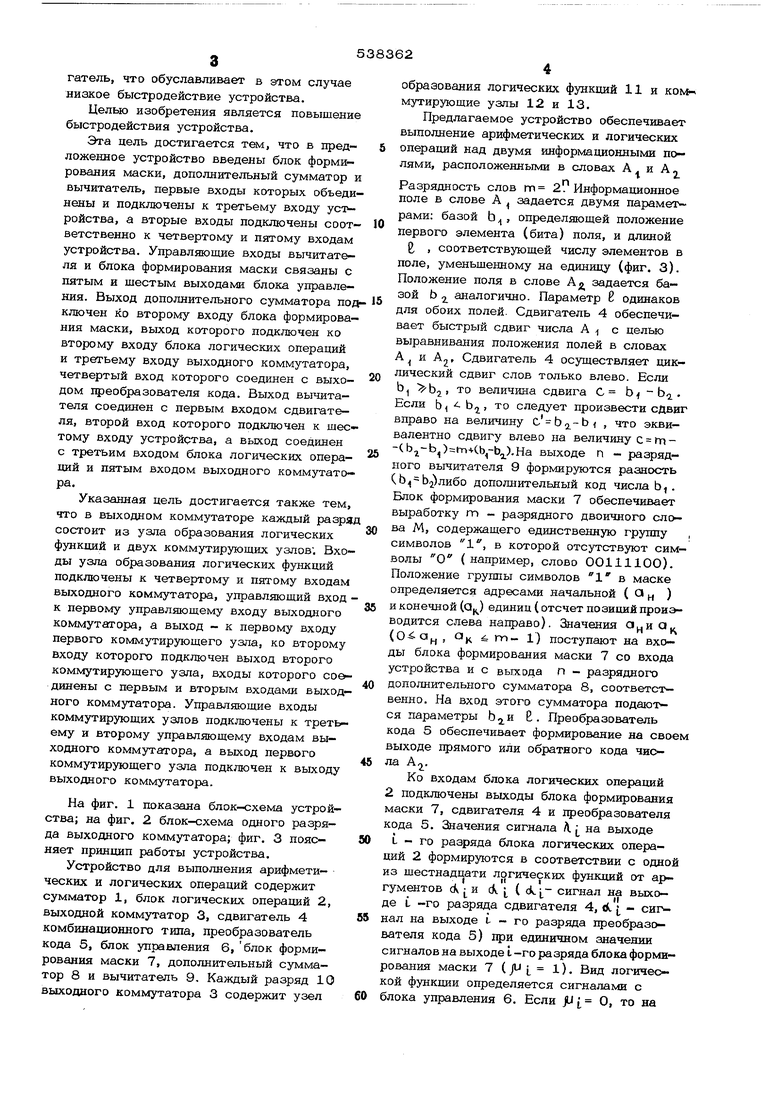

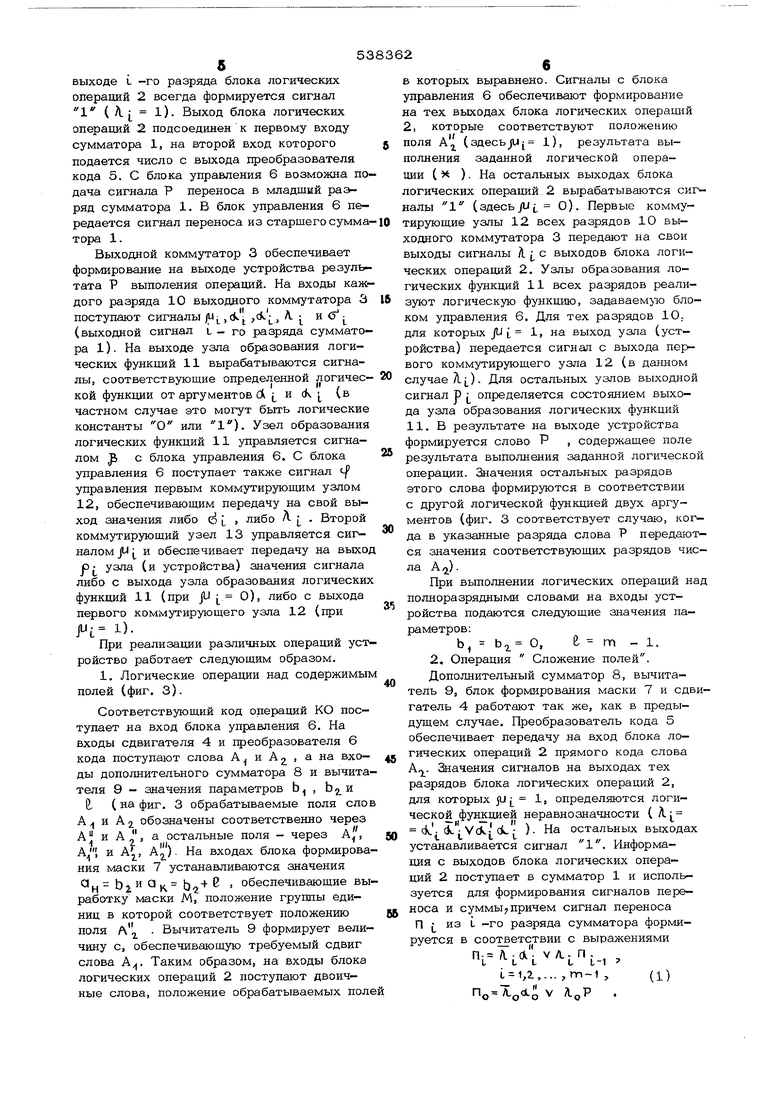

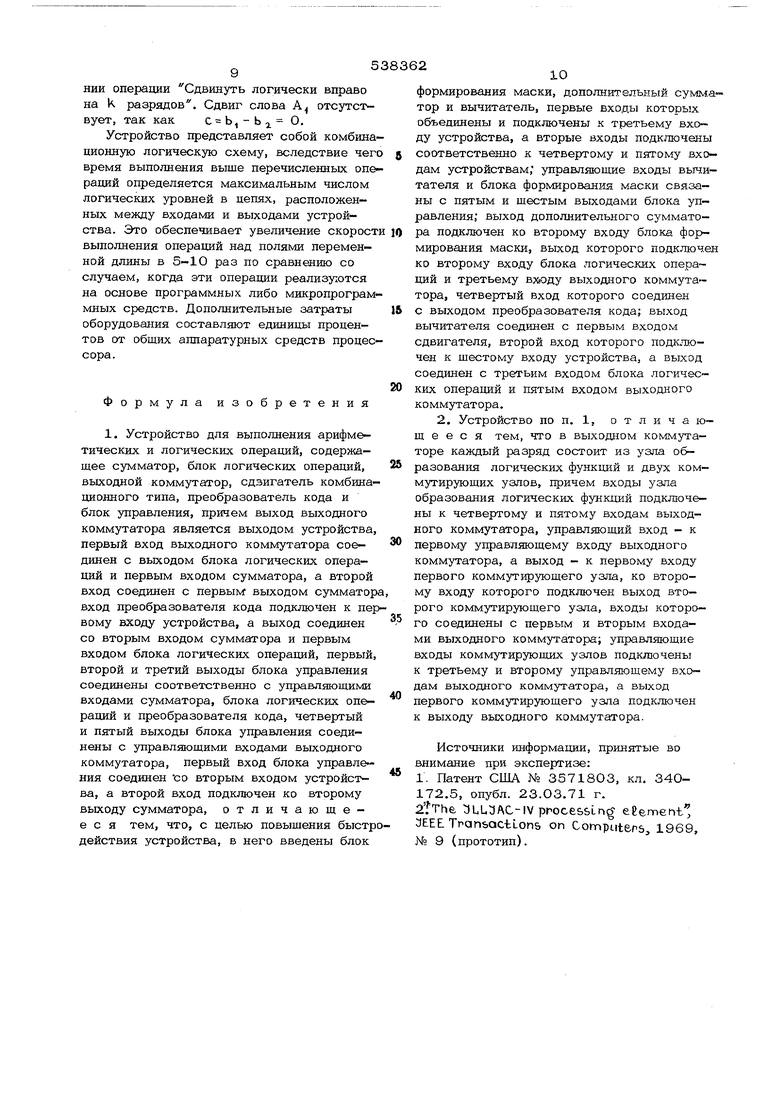

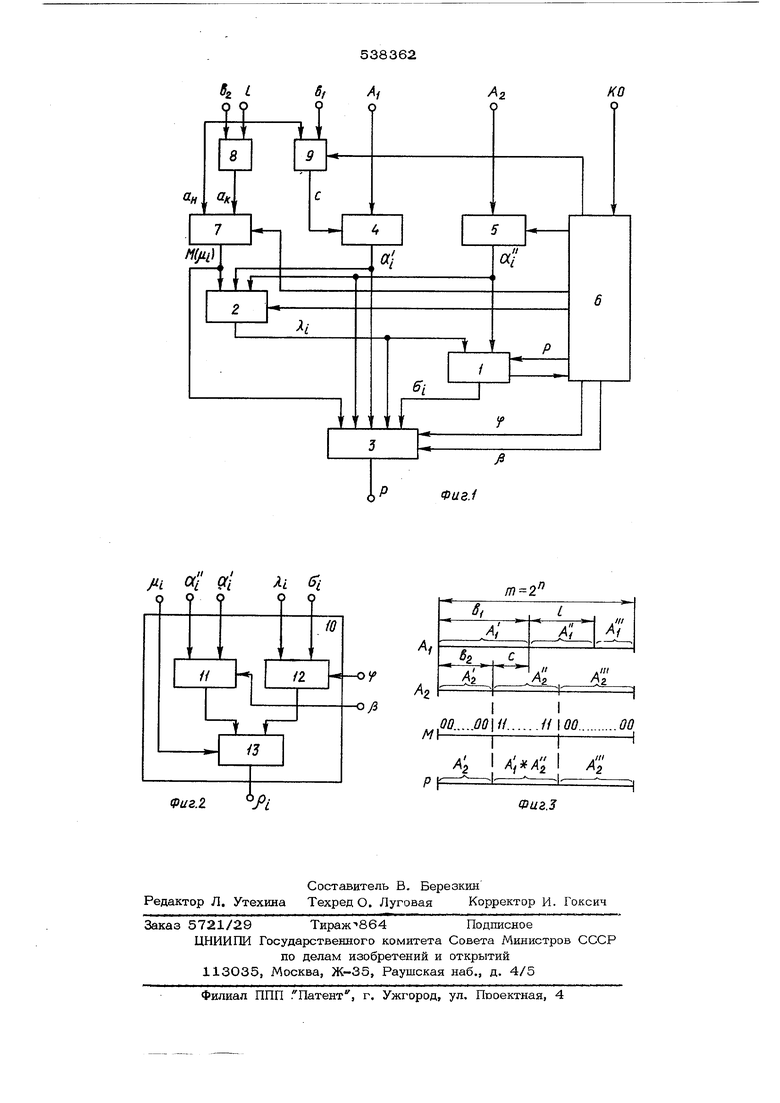

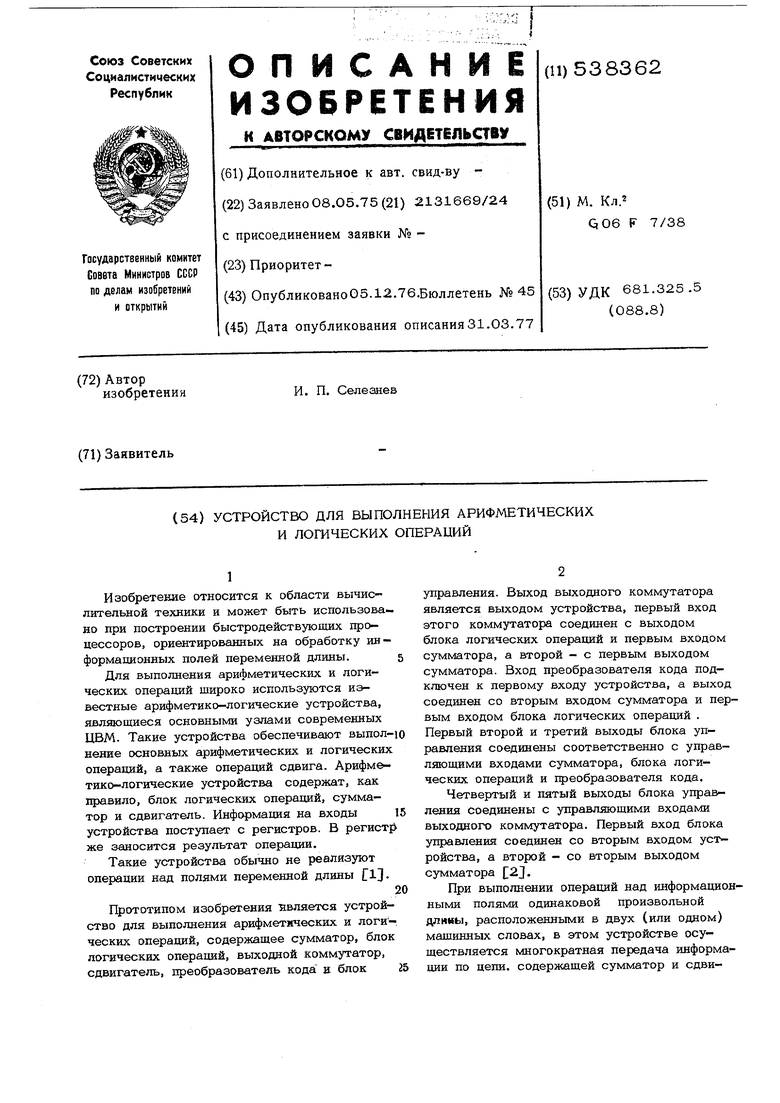

гатель, что обуславливает в этом случае низкое быстродействие устройства. Целью изобретения является повышение быстродействия устройства, Эта цель достигается тем, что в предложенное устройство введены блок формирования маски, дополнительный сумматор вычитатель, первые входы которых объеди нены и подключены к третьему входу устройства, а вторые входы подключены соответственно к четвертому и пятому входам устройства. Управляющие входы вычитателя и блока формирования маски связаны с пятым и шестым выходами блока управления. Выход дополнительного сумматора nof ключен ко второму входу блока формирования маски, выход которого подключен ко второму входу блока логических операций и третьему входу выходного коммутатора, четвертый вход которого соединен с выходом преобразователя кода. Выход вычитателя соединен с первым входом сдвигате- ля, второй вход которого подключен к шес тому входу устройства, а вьрсод соединен с третьим входом блока логических операций и пятым входом выходного коммутатора. Указанная цель достигается также тем, что в выходном коммутаторе каждый разря состоит из узла образования логических функций и двух коммутирующих узлов; Вхо ды узла образования логических функций подключены к четвертому и пятому входам выходного коммутатора, управляющий вход к первому управляющему входу выходного коммутатора, а выход - к первому входу первого коммутирующего узла, ко второму входу которого подключен выход второго коммутирующего узла, входы которого сое динены с первым и вторым входами выходного коммутатора. Управляющие входы коммутирующих узлов подключены к третьему и второму управляющему входам выходного коммутатора, а выход первого коммутирующего узла подключен к выходу выходного коммутатора. На фиг. 1 показана блок-схема устройства; на фиг. 2 блок-схема одного разряда выходного коммутатора; фиг. 3 поясняет принцип работы устройства. Устройство для выполнения арифметических и логических операций содержит сумматор 1, блок логических операхшй 2, выходной коммутатор 3, сдвигатель 4 комбинационного типа, преобразователь кода 5, блок управления 6, блок формирования маски 7, дополнительный сумматор 8 и вычитатель 9, Каждый разряд 10 выходного коммутатора 3 содержит узел образования логических функций 11 и KON мутирующие узлы 12 и 13. Предлагаемое устройство обеспечивает выполнение арифметических и логических операций над двумя информационными порасположенными в словах А . и А лями, Разрядность слов пп 2. Информационное поле в слове А задается двумя параметрами: базой b , определяющей положение первого элемента (бита) поля, и длиной , соответствующей числу элементов в поле, уменьшенному на единицу (фиг. 3). Положение поля в слове Ад задается базой b аналогично. Параметр 6 одинаков для обоих полей. Сдвигатель 4 обеспечивает быстрый сдвиг числа А с целью выравнивания положения полей в словах А н Aj, Сдвигатель 4 осуществляет 1шклический сдвиг слов только влево. Если b, bj , то величина сдвига С b - Ь/. Если Ь( Ь, то следует произвести сдвиг вправо на величину c b2.-b , что эквивалентно сдвигу влево на величину с гп-(b.)in+Cb -b,).Ha выходе п - разрядного вычитателя 9 формируются разность ()либо дополнительный код числа Ь . Блок формирования маски 7 обеспечивает выработку m - разрядного двоичного слова М, содержащего единственную группу , символов 1, Б которой отсутствуют символы О (например, слово 00111100). Положение группы символов I. в маске определяется адресами начальной (OH ) и конечной (а) единиц (отсчет позиций производится слева направо). Значения а (, Оц & т- 1) поступают на входы блока формирования маски 7 со входа устройства и с выхода П - разрядного дополнительного сумматора 8, соответственно. На вход этого сумматора подаются параметры Ь2,и Е. Преобразователь кода 5 обеспечивает форлшрование на своем выходе прямого или обратного кода числа А 2,. Ко входам блока логических операций 2 подключены выходы блока формирования маски 7, сдвигателя 4 и преобразователя кода 5. Значения сигнала Л. ( на выходе L - го разряда блока логических операций 2 формируются в соответствии с одной из шестнадцати логических функций от аргументов (li(d.L сигнал на выходе i -го разряда сдвигателя 4, Л { - сигнал на выходе i- - го разрада гфеобразо- вателя кода 5) при единичном значении сигналов на выходе I -го разряда блока формирования маски 7 ( 1 1). Вид логической функции определяется сигналами с блока управления 6. Если JU О, то на

выходе L -го разряда блока логических операций 2 всегда формируется сигнал 1(Л.1). Выход блока логических операций 2 подсоединен к первому входу сумматора 1, на второй вход которого подается число с выхода преобразователя кода 5. С блока управления 6 возможна подача сигнала Р переноса в младший разряд сумматора 1. В блок управления 6 передается сигнал переноса из старшего сумма тора 1. Выходной коммутатор 3 обеспечивает формирование на выходе устройства резуль тата Р выполения операций. На входы каж дого разряда 10 выходного коммутатора 3 поступают сигналы ..,(;,A.j и G (выходной сигнал L - го разряда суммато ра 1). На выходе узла образования логических функций 11 вырабатываются сигналы, соответствуюшие определенной логичес кой функции от аргументов d j и сК - (в частном случае это могут быть логические константы О или 1). Узел образования логических функций 11 управляется сигналом f, с блока управления 6. С блока управления 6 поступает также сигнал f управления первым коммутирующим узлом 12, обеспечивающим передачу на свой выход значения либо (э либо А Второй коммутирующий узел 13 управляется сигналом Ji L и обеспечивает передачу на выхо f узла (и устройства) значения сигнала либо с выхода узла образования логических функций 11 (при JU j О), либо с выхода первого коммутирующего узла 12 (при Я- реализации различных операций уст ройство работает следующим образом. 1. Логические операции над содержимы полей (фиг. 3). Соответствующий код операций КО поступает на вход блока управления 6. На входы сдвигателя 4 и преобразователя 6 кода поступают слова А к А i а на вхо- ды дополнительного сумматора 8 и вычита теля 9 - значения параметров Ь , i 2. (на фиг. 3 обрабатываемые поля сло А и А 2 обозначены соответственно через AI и А а остальные поля - через А и А, А). На входах блока формирова ния маски 7 устанавливаются значения au biKaj tj-fB , обеспечивающие вы работку маски М, положение группы единиц в которой соответствует положению поля AIJ . Вычитатель 9 формирует величину с, обеспечивающую требуемый сдвиг слова А. Таким образом, на входы блока логических операций 2 поступают двоичные слова, положение обрабатываемых поле

в которых выравнено. Сигналы с блока управления 6 обеспечивают формирование на тех выходах блока логических операций 2, которые соответствуют положению поля Aj (здесьju 1), результата выполнения заданной логической операции ( ). На остальных выходах блока логических операций 2 вырабатываются сигналы 1 (здесь)и О). Первые коммутирующие узлы 12 всех разрядов 10 выходного коммутатора 3 передают на свои выходы сигналы Л. | с выходов блока логических операций 2. Узлы образования логических функций 11 всех разрядов реализуют логическую функцию, задаваемого блоком управления 6. Для тех разрядов 10. для которых JU ( 1, на выход узла (устройства) передается сигнал с выхода первого коммутирующего узла 12 (в даьшом случае 1|). Для остальных узлов выходной сигнал Р j определяется состо$шием выхода узла образования логических функций 11. В результате на выходе устройства формируется слово Р , содержащее поле результата выполнения заданной логической операции. Значения остальных разрядов этого слова формируются в соответствии с другой логической функцией двух аргументов (фиг. 3 соответствует случаю, когда в указанные разряда слова Р передаются значения соответствующих разрядов числа А л). При выполнении логических операций над полноразрядными словами на входы устройства подаются следующие значения параметров:Ь, о, ПП - 1. 2, Операция Сложение полей. Дополнительный сумматор 8, вычитатель 9, блок формирования маски 7 и сдвигатель 4 работают так же, как в предыдущем случае. Преобразователь кода 5 обеспечивает передачу на вход блока логических операций 2 прямого кода слова Ал(. Значения сигналов на выходах тех разрядов блока логических операций 2, для которых ju j 1, определяются логической фун кцией неравнозначности ( Л- ck.- ck: Vck. ci ). На остальных выходах устанавливается сигнал 1. Информация с выходов блока логических операций 2 поступает в сумматор 1 и используется для формирования сигналов переноса и суммы причем сигнал переноса П ( из 1 -го разряда сумматора формируется в соответствии с выражениями (х;у/1.п., По V Значение сигнала Р задается блоком управления 6. При вьтолнении рассматривае мой операции Р О. Из выражений (1) следует, что в младших разрядах сумматора 1, соответствующих полю А (см. фиг. 3), сигналы переноса отсутствуют, так как Л;, 1и Р 0. Это обеспечивает нормаль ное выполнение операции сложения в разрядах сумматора, соответствующих полю А (здесь А ...). Если возникает сигнал п еноса из разряда сумматора, соответствующего положению старшего разряд поля А, то он распространяется до выхода переноса из старшего разряда сумма- тора, так как для разрядов сумматора, соответствующих полю А, , Л 1. Первые коммутирующие узлы 12 всех разрядов 10 выходного коммутатора 3 передают на свои выходы сигналы (5 ( с выходов сумматора 1. Блок управления 6 задает определенную логическую функцию, реализуемую управляемыми узлами образования логических функций 11 всех разрядов 10, Передача информации на выходы вторых коммутирующих узлов 13 разрядов 10 выходного коммутатора 3 осуществляется так же, как и при выполнении логических операций. При сложении полноразрядных слов , 1, 3.Операция Вычитание полей. Эта операция выполняется так же, как операция Сложение полей, с той разницей, что на выходе преобразователя кода 5 формируется обратный код числа А.,, а задаваемый блоком управления 6 сигнал Р 1. В соответствии с выражениями (1) в рассматриваемом случае формируется сигнал переноса из разряда сумматора 1, соответствующего положению старшего ра& ряда поля А2 (для всех разрядов этого поля AJ; 1). Таким образом, в разрядах сумматора 1, соответствующих полю А,, производится сложение полей в дополнит ном коде, т. е. вычитание. 4.Операция Сдвинуть логически влево на k разрядов. Соответствующий код операции подаетс в блок управления 6, на вход сдВигателя 4 поступает сдвигаемое число А . Параметры имеют следующие значения: Ь, k, b2 О, значение Е. соответствует обратному коду числа k( m-l - k ). Устройство работает так же, как при выпо нении логических операций над содержимым полей, причем на выходы тех разрядов бло ка логических операций 2, для которых /и j 1, передаются соответствующие значения А с выхода сдвигателя 4, а на выходах узлов образования логических фун 1ЩЙ 11 всех разрядов 10 выходного коммутатора 3 устанавливаются значения О. В рассматриваемом случае К, , ,j + .. Следовательно, в результате выполнения операции слово А сдвигается влево на величину k , и bk младших разрядов занесены нули. 5.Операция Сдвинуть логически вправо на k разрядов. В данном случае параметры имеют следующие значения:Ь, О, ,В СК1д§ р, Устройство работает так же, как и при выполнении предыдущей операции, причем ,, + . а величина с соответствует дополшительному коду k. 6.Операция Сдвинуть арифметически вправо на К разрядов. Операция выполняется так же, как операция Сдвинуть логически вправо на К разрядов с той разницей, что на выходы узлов образования логических функций 11 всех разрядов 10 выходного коммутатора 3 из блока управления 6 передается значение знакового разряда сумматора. 7. Операция Сдвинуть циклически влево на k разрядов. Устройство работает так же, как при выполнении операции Сдвинуть логически влево на К разрядов, хфичем входные параметры имеют следующие значения: b. k. В ггч - 1. Следовательно, маска W содержит единицы во всех разрядах, что обеспечивает передачу на выход устройства слова А, сдвинутого влево на К разр5здов. 8. Операция Сдвинуть циклически вправо на k разрядов. Устройство работает так же, как при выполнении предыдущей операции, однако вычитатель 9 работает в режиме, когда на его выходе формируется дополнительный код числа Ь j ( К ) 9.Операция Отбросить К разрядов справа. На входы устройства поступают соответствующий код опфадии, число А., параметры Ь, . В дальнейшем устройство работает так же, как при выполнении операции Сдвинуть логически влево на k разрядов. Очевидно, что сдвиг слова А в данном случае c b,-b 0. отсутствует, так как 10.Операция Отбросить k разрядов слева. В данном случае параметры имеют следующие значения: b b Ус ройство работает так же, как при выполнеНИИ операции Сдвинуть логически вправо на К разрядов. Сдвиг слова А отсутствует, так как c b,-b.j. О. Устройство представляет собой комбина ционную логическую схему, вследствие чег время выполнения выше перечисленных опе раций определяется максимальным числом логических уровней в цепях, расположенных между входами и выходами устройства. Это обеспечивает увеличение скорост выполнения операций над полями переменной длины в 5-10 раз по сравнению со случаем, когда эти операции реализуются на основе программных либо микропрограм мных средств. Дополнительные затраты оборудования составляют единицы процентов от общих аппаратурных средств процес сора. Формула изобретения 1. Устройство для выполнения арифметических и логических операций, содержащее сумматор, блок логических операций, выходной коммутатор, сдэигатель комбина ционного типа, преобразователь кода и блок управления, причем выход выходного коммутатора является выходом устройства первый вход выходного коммутатора соединен с выходом блока логических операций и первым входом сумматора, а второй вход соединен с первым выходом сумматор вход преобразователя кода подключен к пе вому входу устройства, а выход соединен со вторым входом сумматора и первым входом блока логических операций, первый второй и третий выходы блока управления соединены соответственно с управляющими входами сумматора, блока логических операций и преобразователя кода, четвертый и пятый выходы блока управления соединены с управляющими входами выходного коммутатора, первый вход блока управле- ния соединен со вторым входом устройства, а второй вход подключен ко второму выходу сумматора, отличающееся тем, что, с целью повыщения быстр действия устройства, в него введены блок формирования маски, дополнительный сумматор и вычитатель, первые входы которых объединены и подключены к третьему входу устройства, а вторые входы подключены соответственно к четвертому и пятому входам устройствам, управляющие входы вычитателя и блока формирования маски связаны с пятым и щестым выходами блока управления, выход дополнительного сумматора подключен ко второму входу блока формирования маски, выход которого подключен ко второму входу блока логических операций и третьему входу выходного коммутатора, четвертый вход которого соединен с выходом преобразователя кода; выход вычитателя соединен с первым входом сдвигателя, второй вход которого подключен к щестому входу устройства, а выход соединен с третьим входом блока логических операций и пятым входом выходного коммутатора. 2. Устройство по п. 1, о т л и ч а ю- щ е е с я тем, что в выходном коммутаторе каждый разряд состоит из узла образования логических функций и двух коммутирующих узлов, причем входы узла образования логических функций подключены к четвертому и пятому входам выходного коммутатора, управляющий вход - к первому управляющему входу выходного коммутатора, а выход - к первому входу первого коммутирующего узла, ко второму входу которого подключен выход второго коммутирующего узла, входы которого соединены с первым и вторым входами выходного коммутатора; управляющие входы коммутирующих узлов подключены к третьему и второму управляющему входам выходного коммутатора, а выход первого коммутирующего узла подключен к выходу выходного коммутатора. Источники информации, принятые во внимание при экспертизе: 1. Патент США № 3571803, кл. 340172.5, опубл. 23.ОЗ.71 г. , ::)LU3АС-IV processing eEemeht ЗЕЕЕ Transact tons on Computers, 1969, № 9 (прототип).

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения арифметических и логических операций | 1977 |

|

SU674017A2 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для замены числовых полей | 1983 |

|

SU1132284A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

i (Х- Of- Ai ffi о 9 9О О

Фиг.2 °Л

о/г

OQ,....OQ iiin 00.

.00

М

А I А

Фиг.З

Авторы

Даты

1976-12-05—Публикация

1975-05-08—Подача