(54) АССОЦИАТИВНАЯ ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1977 |

|

SU637866A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Элемент памяти | 1986 |

|

SU1388947A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU868836A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1990 |

|

SU1751816A1 |

1

Изобретение относится к области ЗУ.

Известны ассоциативные ячейки памяти 1,2.

Одна из известных ассоциативных ячеек памяти выполнена интегральнь м способом и содержит большое количество транзисторов 1. Кроме того, она потребляет большую мощность при обращении и особенно при хранении информации.

Из известных ассоциативных ячеек памяти наиболе близким техническим решением к данному изобретению является ассоциативная ячейка памяти, содержащая информационные транзисторы, коллекторы и базы которых соединены перекрестно, а эмиттеры подключены к первой управляющей цшне, нагрузочньш двухколлекторный транзистор дополняющего типа, коллекторы которого соединены с базами информационных транзисторов, а эмиттер - со второй управляющей шиной, выходные транзисторы, коллекторы которых подключены к шине ассоциативной выборки, и разрядные шины 2. Кроме того, ячейка содержит другие управляющие шины, что затрудняет ее выполнение в интегральной форме и значительно усложняет саму ячейку.

Целью изобретения является упрощение ячейки.

Эта цель достигается тем, что предложенная ассоциативная ячейка памяти содержит вспомогательные двухколлекторные транзисторы дополняющего типа, эмиттеры которых подключены к разрядным шинам, одни коллекторы соединены с базами выходных транзисторов, другие - с базами информационных транзисторов. Эмиттеры выходных транзисторов и базы транзисторов дополняющего типа соединены с первой управляющей шиной.

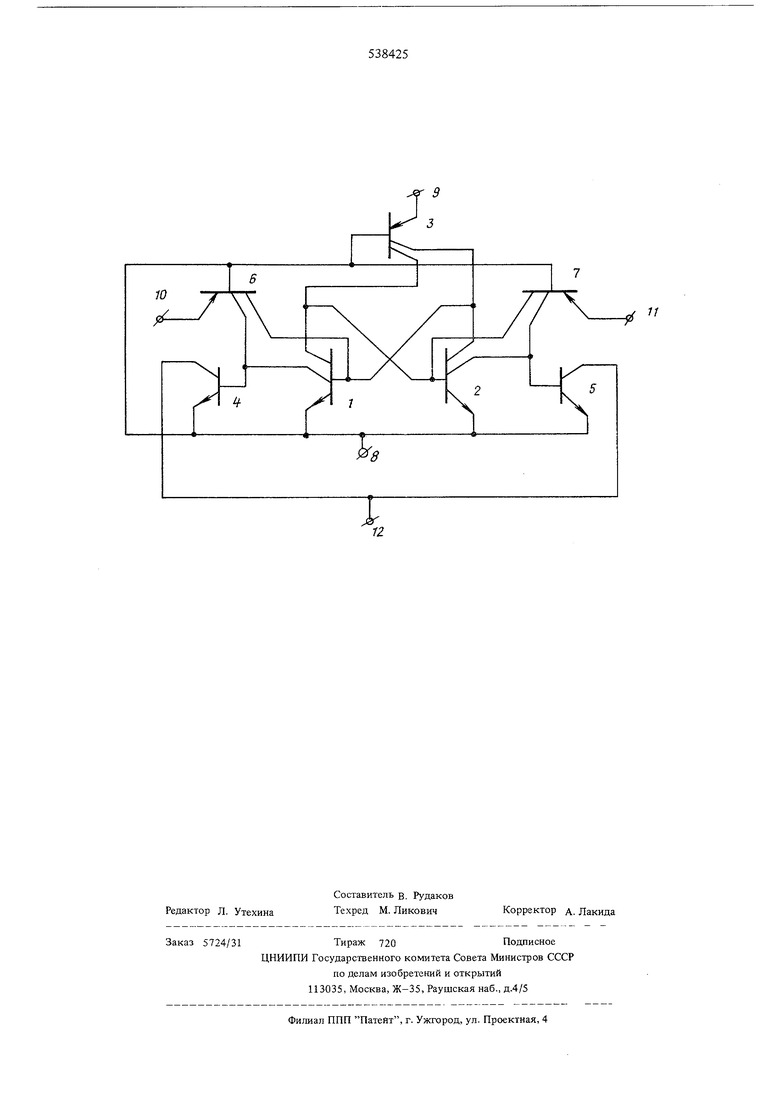

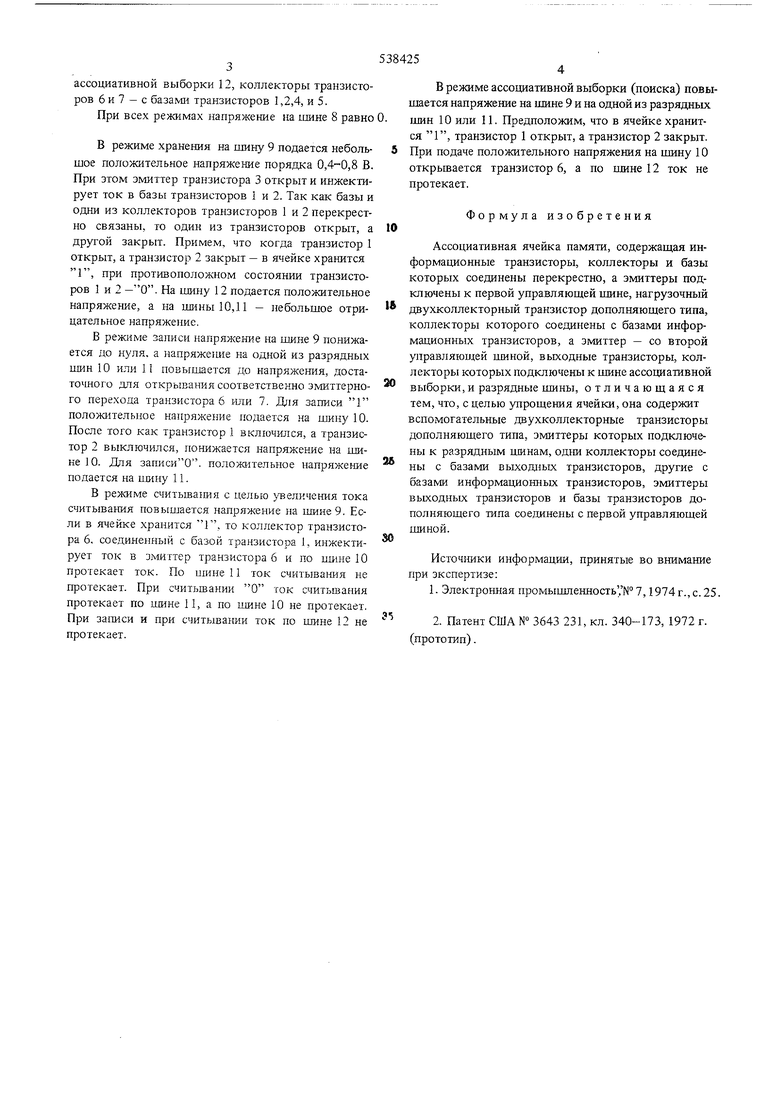

На чертеже дана электрическая схема предложенной ячейки.

Ассоциативная ячейка памяти содержит два, например двухколлекторных, информационных транзистора 1 и 2, нагрузочный двухколлекторный

транзистор 3 дополняющего типа, два выходных транзистора 4 и 5 и два вспомогательных двухколлекторных транзистора 6 и 7 дополняющего типа. Эмиттеры транзисторов 1,2,4, и 5 соединены с базами транзисторов 3,6 и 7 и подключены к первой управляющей шине 8, которая может быть общей шиной. Эмиттер транзистора 3 соединен со второй управляющей шиной 9, которая может быть словарной шиной. Эмиттеры транзисторов 6 и 7 соединены соответственно с разрядными шинами 10 и 11. Коллекторы транзисторов 4 и 5 соединены с шиной

ассоциативной выборки 12, коллекторы транзисторов 6 и 7 - с 6a3aNffl транзисторов 1,2,4, и 5.

При всех режимах напрях ение на шине 8 равно

В режиме хранения на шину 9 подается небольшое положительное напряжение порядка 0,4-0,8 В. При этом эмиттер транзистора 3 открыт и инжектирует ток в базы транзисторов 1 и 2. Так как базы и одни из коллекторов транзисторов 1 и 2 перекрестно связаны, то один из транзисторов открыт, а другой закрыт. Примем, что когда транзистор 1 открыт, а транзистор 2 закрыт - в ячейке хранится 1, при противоположном состоянии транзисторов 1 и 2 . На шину 12 подается положительное напряжение, а на шины 10,11 - небольшое отрицательное напряжение.

В режиме записи напряжение на шине 9 понижается до нуля, а напряже ше на одной из разрядных шин 10 или 11 повышается до напряжеш1я, достаточного для открывания соответственно эмиттерного перехода транзистора 6 или 7. Для записи 1 положите.чьное напряжение подается на шину 10. После того как транзистор 1 включился, а транзистор 2 выключился, понижается напряжение па шине 10. Для записи 0. положительное напряжегше подается на шипу 11.

В режиме считыва1шя с пелью увеличения тока считывания повьш1ается напряжение па шине 9. Если в ячейке хранится 1, то коллектор транзистора 6. соединенный с базой транзистора 1, инжектирует ток в змиттер транзистора 6 и по пшне 10 протекает ток. По шине 11 ток считывания не протекает. При считьшании О ток считьшапия протекает по шине 11, а по ишне 10 не протекает. При за1тиси и при считывании ток по шине 12 не протекает.

В режиме ассоциативной выборки (поиска) повышается напряжение на шине 9 и на одной из разрядных шин 10 или 11. Предположим, что в ячейке хранится 1, транзистор 1 открыт, а транзистор 2 закрыт. При подаче положительного напряжения на шину 10 открьшается транзистор 6, а по шине 12 ток не протекает.

Формула изобретения

Ассоциативная ячейка памяти, содержащая информационные транзисторы, коллекторы и базы которых соединены перекрестно, а эмиттеры подключены к первой управляюшей шине, нагрузочный двухколлекторный транзистор дополняющего типа, коллекторы которого соединены с базами информационных транзисторов, а змиттер - со второй управляющей пшной, выходные транзисторы, коллекторы которых подключены к шине ассоциативной выборки, и разрядные шины, отличающаяся тем, что, с целью упрощения ячейки, она содержит вспомогательные двухколлекторные транзисторы дополняющего типа, эмиттеры которых подключены к разрядным шинам, одьш коллекторы соединены с базами выходных транзисторов, другие с базами информационных транзисторов, эмиттеры выходных транзисторов и базы транзисторов дополняющего типа соединены с первой управляющей

шиной.

Источ П1ки информации, принятые во внимание при экспертизе:

(прототип).

//

Авторы

Даты

1976-12-05—Публикация

1975-09-05—Подача