54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЧЕТНОСТИ

го сигнала, а выход триггера подключен к одному из входов линейного сумматора.

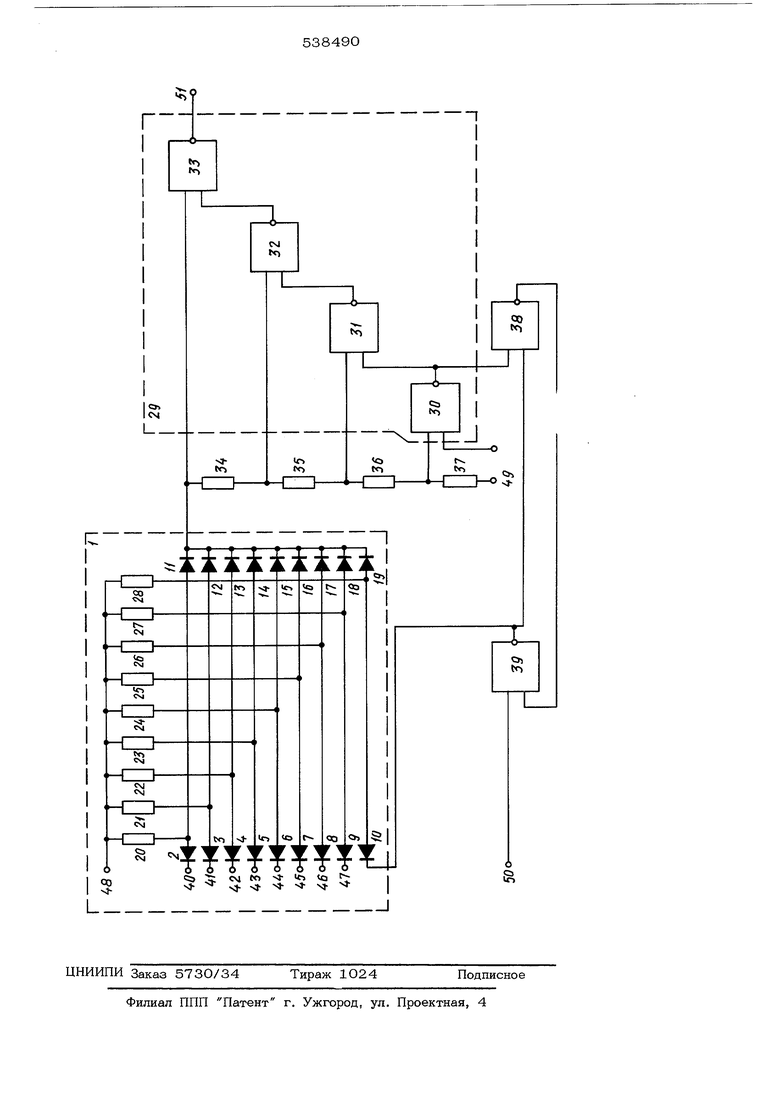

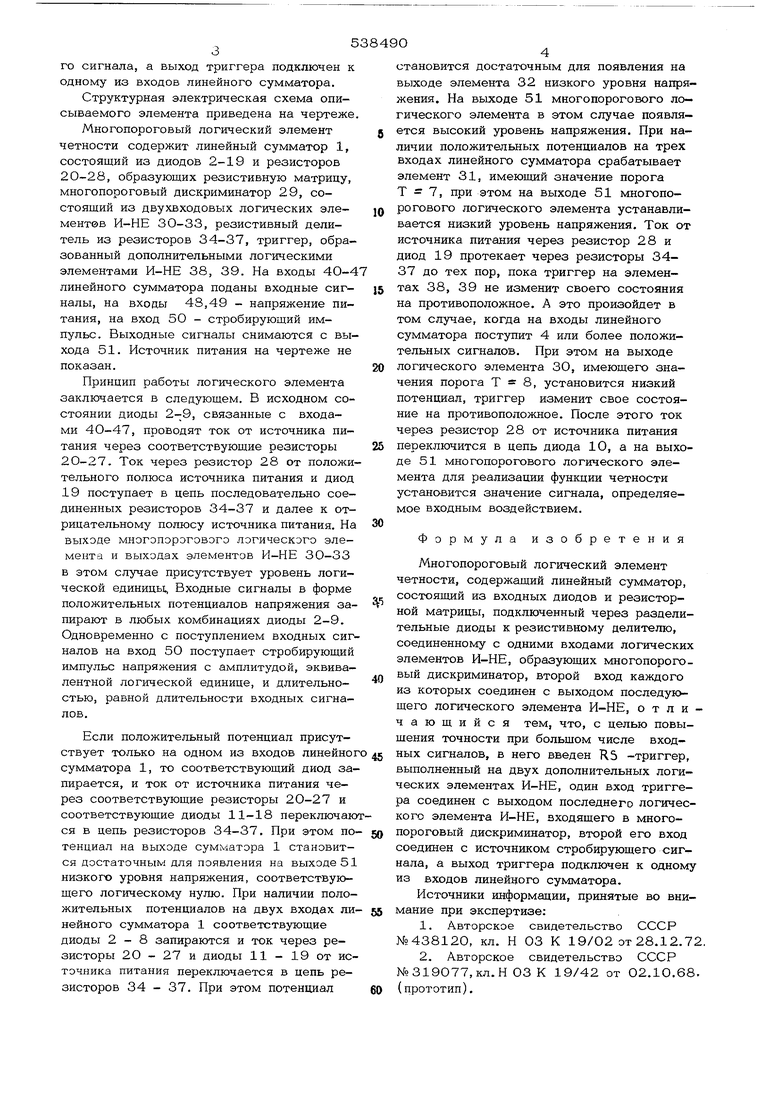

Структурная электрическая схема описываемого элемента приведена на чертеже

Многопороговый логический элемент четности содержит линейный сумматор 1, состоящий из диодов 2-19 и резисторов 20-28, образующих резистивную матрицу, многопороговый дискриминатор 29, состоящий из двухвходовых логических элементов И-НЕ ЗО-ЗЗ, резистивный делитель из резисторов 34-37, триггер, образованный дополнительными логическими элементами И-НЕ 38, 39. На входы 4О-4 линейного сумматора поданы входные сигналы, на входы 48,49 - напряжение питания, на вход 5О - стробирующий импульс. Выходные сигналы снимаются с выхода 51. Источник питания на чертеже не показан.

Принцип работы логического элемента заключается в следующем. В исходном состоянии диоды 2-9, связанные с входами 40-47, проводят ток от источника питания через соответствующие резисторы 2О-27. Ток через резистор 28 от положительного полюса источника питания и диод 19 поступает в цепь последовательно соединенных резисторов 34-37 и далее к отрицательному полюсу источника питания. На выходе многэпэрэговэго логического элемента и выходах элементов И-НЕ ЗО-ЗЗ в этом случае присутствует уровень логической единицы, Входные сигналы в форме положительных потенциалов напряжения запирают в любых комбинациях диоды 2-9. Одновременно с поступлением входных сигналов на вход 5О поступает стробирующий импульс напряжения с амплитудой, эквивалентной логической единице, и длительностью, равной длительности входных сигналов.

Если положительный потенциал присутствует только на одном из входов линейного

сумматора 1, то соответствующий диод запирается, и ток от источника питания через соответствующие резисторы 20-27 и соответствующие диоды 11-18 переключаюся в цепь резисторов 34-37. При этом потендиал на выходе сумматора 1 становится достаточным для появления на выходе 51 низкого уровня напряжения, соответствующего логическому нулю. При наличии положительных потенциалов на двух входах линейного сумматора 1 соответствующие диоды 2-8 запираются и ток через резисторы 2О - 27 и диоды 11 - 19 от источника питания переключается в цепь резисторов 34 - 37. При этом потенциал

становится достаточным для появления на выходе элемента 32 низкого уровня напряжения. На выходе 51 многопорогового логического элемента в этом случае появляется высокий уровень напряжения. При наличии положительных потенциалов на трех входах линейного сумматора срабатывает элемент 31, имеющий значение порога Т 7, при этом на выходе 51 многопорогового логического элемента устанавливается низкий уровень напряжения. Ток от источника питания через резистор 28 и диод 19 протекает через резисторы 3437 до тех пор, пока триггер на элементах 38, 39 не изменит своего состояния на противоположное. А это произойдет в том случае, когда на входы линейного сумматора поступит 4 или более положительных сигналов. При этом на выходе

логического элемента 30, имеющего значения порога Т 8, установится низкий потенциал, триггер изменит свое состояние на противоположное. После этого ток через резистор 28 от источника питания

переключится в цепь диода 10, а на выходе 51 многопорогового логического элемента для реализации функции четности установится значение сигнала, определяемое входным воздействием.

Формула изобретения

Многопороговый логический элемент четности, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к резистивному целителю, соединенному с одними входами логических элементов И-НЕ, образующих многопороговый дискриминатор, второй вход каждого из которых соединен с выходом последующего логического элемента И-НЕ, отличающийся тем, что, с целью повышения точности при больщом числе входвыполненный на двух дополнительных логических элементах И-НЕ, один вход триггера соединен с выходом последнего логического элемента И-НЕ, входящего в многопороговый дискриминатор, второй его вход соединен с источником стробирующего сигнала, а выход триггера подключен к одному из входов линейного сумматора.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР №438120, кл. Н 03 К 19/02 от 28.12.72

2.Авторское свидетельство СССР №319О77,кл.Н ОЗ К 19/42 от О2.10.68. (прототип). ных сигналов, в него введен R5 -триггер.

г

-

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

| Многопороговый логический элемент четности | 1977 |

|

SU660261A2 |

| Многопороговый логический элемент четности | 1976 |

|

SU608266A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Многопороговый логический элемент | 1979 |

|

SU790341A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Многопороговый логический элемент | 1983 |

|

SU1112564A2 |

| Многопороговый логический элемент | 1977 |

|

SU705684A1 |

| Многопороговый логический элемент | 1988 |

|

SU1575307A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

сл

CSJ

IL.

1л tv

sh

t«

.шна

i;;

s

f («-

,

sh

Ol

to

Авторы

Даты

1976-12-05—Публикация

1975-11-24—Подача