тационного триггера подключены к выходам элементов И-НЕ первого и второго разрядов.

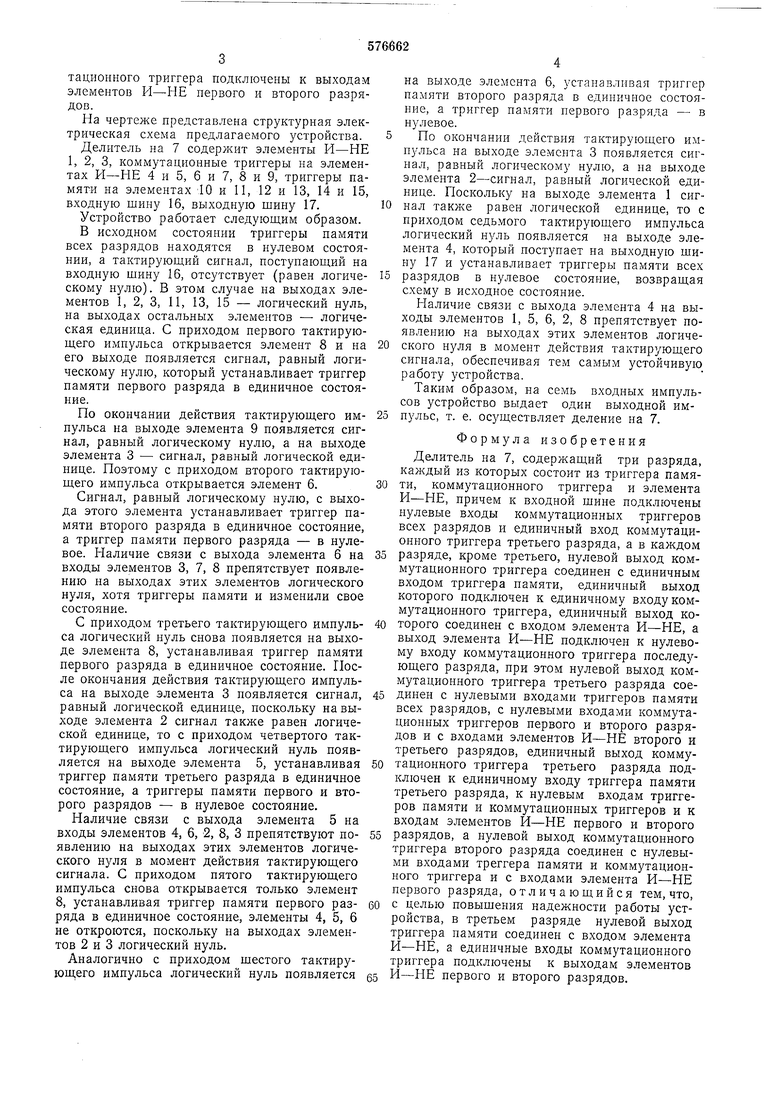

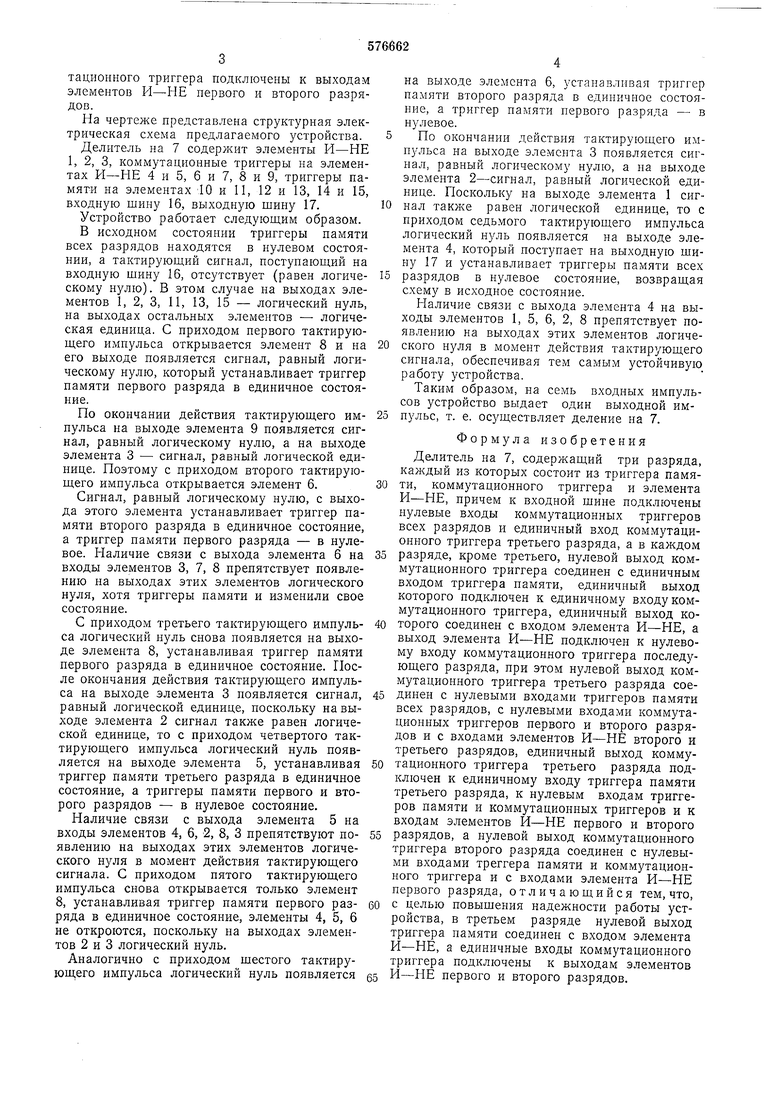

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Делитель на 7 содерл ит элементы И-НЕ 1, 2, 3, коммутащюнные триггеры на элементах И-НЕ 4 и 5, 6 и 7, 8 и 9, триггеры памяти на элементах 10 и 11, 12 и 13, 14 и 15, входную шину 16, выходную шину 17.

Устройство работает следующим образом.

В исходном состоянии триггеры памяти всех разрядов находятся в нулевом состоянии, а тактирующий сигнал, поступающий на входную шину 16, отсутствует (равен логическому нулю). В этом случае на выходах элементов 1, 2, 3, 11, 13, 15 - логический нуль, на выходах остальных элементов - логическая единица. С приходом первого тактирующего импульса открывается элемент 8 и на его выходе появляется сигнал, равный логическому нулю, который устанавливает триггер памяти первого разряда в единичное состояние.

По окончании действия тактирующего импульса на выходе элемента 9 появляется сигнал, равный логическому нулю, а на выходе элемента 3 - сигнал, равный логической единице. Поэтому с приходом второго тактирующего импульса открывается элемент 6.

Сигнал, равный логическому нулю, с выхода этого элемента устанавливает триггер памяти второго разряда в единичное состояние, а триггер памяти первого разряда - в нулевое. Наличие связи с выхода элемента 6 на входы элементов 3, 7, 8 препятствует появлению на выходах этих элементов логического нуля, хотя триггеры памяти и изменили свое состояние.

С приходом третьего тактирующего импульса логический нуль снова появляется на выходе элемента 8, устанавливая триггер памяти первого разряда в единичное состояние. После окончания действия тактирующего импульса на выходе элемента 3 появляется сигнал, равный логической единице, поскольку на выходе элемента 2 сигнал также равен логической единице, то с приходом четвертого тактирующего импульса логический нуль появляется на выходе элемента 5, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти первого и второго разрядов - в нулевое состояние.

Наличие связи с выхода элемента 5 на входы элементов 4, 6, 2, 8, 3 препятствуют появлению на выходах этих элементов логического иуля в момент действия тактирующего сигнала. С приходом пятого тактирующего импульса снова открывается только элемент 8, устанавливая триггер памяти первого разряда в единичное состояние, элементы 4, 5, 6 не откроются, поскольку на выходах элементов 2 и 3 логический нуль.

Аналогично с приходом шестого тактирующего импульса логический нуль появляется

на выходе элемента 6, устанавливая триггер памяти второго разряда в единичное состояние, а триггер памяти первого разряда - в нулевое.

5 По окончании действия тактирующего импульса на выходе элемента 3 появляется сигнал, равный логическому нулю, а на выходе элемента 2-сигнал, равный логической единице. Поскольку на выходе элемента 1 сигнал также равен логической единице, то с приходом седьмого тактирующего импульса логический нуль появляется на выходе элемента 4, который поступает на выходную шину 17 и устанавливает триггеры памяти всех

15 разрядов в нулевое состояние, возвращая схему в исходное состояние.

Наличие связи с выхода элемента 4 на выходы элементов 1, 5, 6, 2, 8 препятствует появлению на выходах этих элементов логического нуля в момент действия тактирующего сигнала, обеспечивая тем самым устойчивую работу устройства.

Таким образом, на семь входных импульсов устройство выдает один выходной им5 пульс, т. е. осуществляет деление на 7.

Формула изобретения

Делитель на 7, содержащий три разряда, каждый из которых состоит из триггера памяти, коммутационного триггера и элемента И-НЕ, причем к входной шине подключены нулевые входы коммутационных триггеров всех разрядов и единичный вход коммутационного триггера третьего разряда, а в каждом

5 разряде, кроме третьего, нулевой выход коммутационного триггера соединен с единичным входом триггера памяти, единичный выход которого подключен к единичному входу коммутационного триггера, единичный выход которого соединен с входом элемента И-НЕ, а выход элемента И-НЕ подключен к нулевому входу коммутационного триггера последующего разряда, при этом нулевой выход коммутационного триггера третьего разряда сое5 Динен с нулевыми входами триггеров памяти всех разрядов, с нулевыми входами коммутационных триггеров первого и второго разрядов и с входами элементов И-НЕ второго и третьего разрядов, единичный выход коммутационного триггера третьего разряда подключен к единичному входу триггера памяти третьего разряда, к нулевым входам триггеров памяти и коммутационных триггеров и к входам элементов И-НЕ первого и второго

5 разрядов, а нулевой выход коммутационного триггера второго разряда соединен с нулевыми входами треггера памяти и коммутационного триггера и с входами элемента И-НЕ первого разряда, отличающийся тем, что,

0 с целью повышения надежности работы устройства, в третьем разряде нулевой выход триггера памяти соединен с входом элемента И-НЕ, а единичные входы коммутационного триггера подключены к выходам элементов

Н-НЕ первого и второго разрядов.

56

Источники информации, принятые во внимание при экспертизе

1. Гутников В. С. Интегральная электрони-2. Авторское свидетельство СССР №418982,

ка в измерительных приборах. Л., «Энергия, кл. Н ОЗК 23/02, 1972. 1974, с. 51, рис. 24.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на шесть | 1976 |

|

SU617846A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

Авторы

Даты

1977-10-15—Публикация

1976-02-13—Подача