ключей к единичному вхоДу третьего и к нулевому входу второго коммутационных триггеров, а выход второго элемента И-НЕ соединен с единичным входом третьего И с нулевым входом второго коммутационных триггеров.

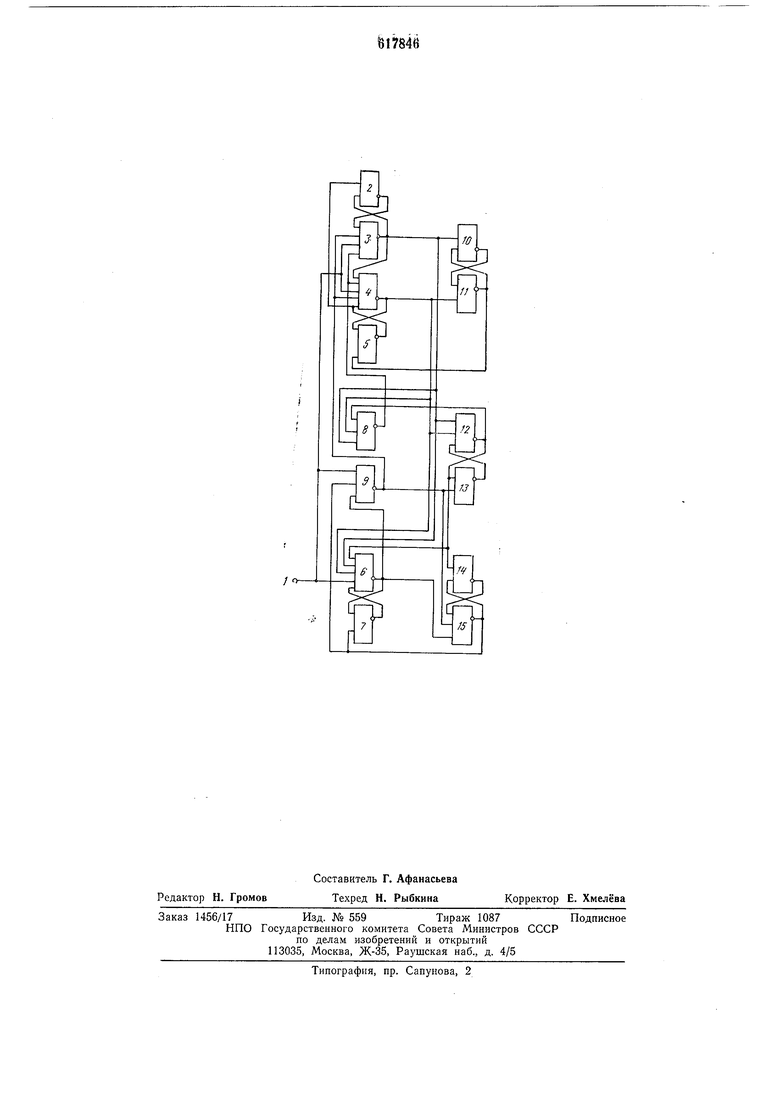

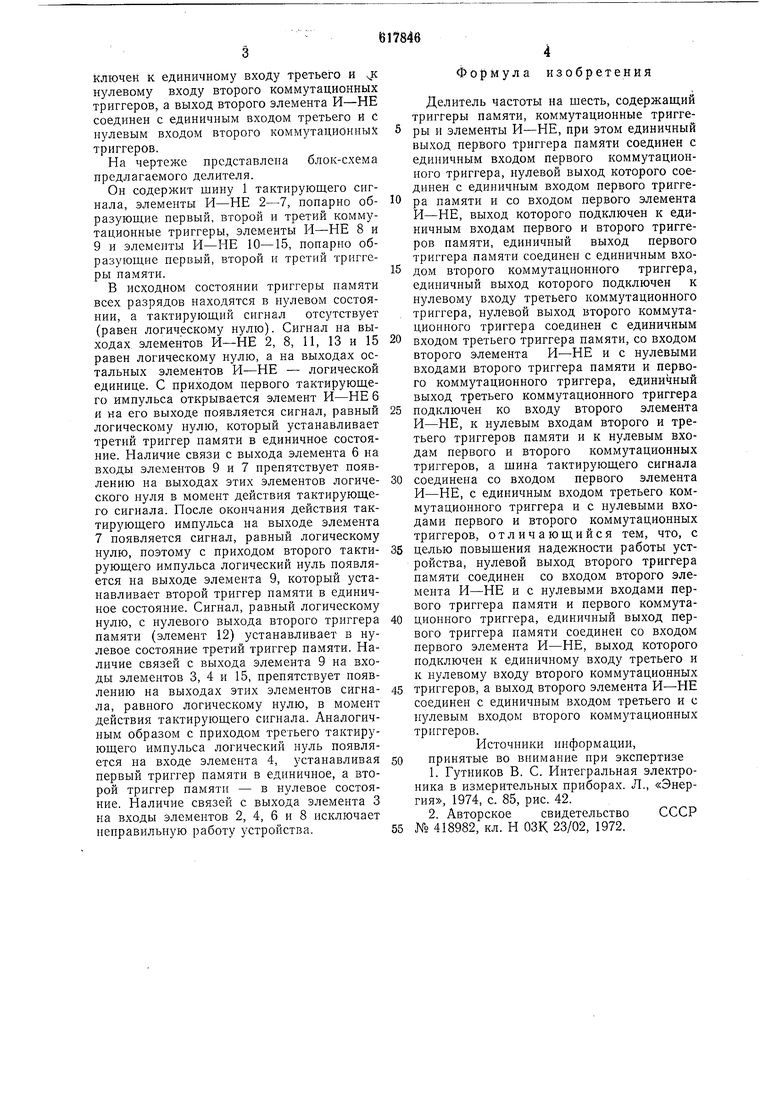

На чертеже представлена блок-схема предлагаемого делителя.

Он содержит шину 1 тактирующего сигнала, элементы И-НЕ 2-7, попарно образующие первый, второй и третий коммутационные триггеры, элементы И-НЕ 8 н 9 н элементы И-НЕ 10-15, попарно образуюш,ие первый, второй и третий триггеры памяти.

В исходном состоянии триггеры намяти всех разрядов находятся в нулевом состоянии, а тактирующий сигнал отсутствует (равен логическому нулю). Сигнал на выходах элементов И-НЕ 2, 8, 11, 13 и 15 равен логическому нулю, а на выходах остальных элементов И-НЕ - логической единице. С приходом первого тактирующего импульса открывается элемент И-НЕ 6 и на его выходе появляется сигнал, равный логическому нулю, который устанавливает третий триггер памяти в единичное состояние. Наличие связи с выхода элемента 6 на входы элементов 9 и 7 препятствует появлению на выходах этих элементов логнческого нуля в момент действия тактирующего сигнала. Носле окончания действия тактирующего импульса на выходе элемента 7 появляется сигнал, равный логическому нулю, поэтому с приходом второго тактирующего импульса логический нуль появляется на выходе элемента 9, который устанавливает второй триггер памяти в единичное состояние. Сигнал, равный логическому нулю, с нулевого выхода второго триггера памяти (элемент 12) устанавливает в нулевое состояние третий триггер памяти. Наличие связей с выхода элемента 9 на входы элементов 3, 4 и 15, препятствует появлению на выходах этих элементов сигнала, равного логическому нулю, в момент действия тактирующего сигнала. Аналогичным образом с приходом третьего тактирующего импульса логический нуль появляется на входе элемента 4, устанавливая первый триггер памяти в единичное, а второй триггер памяти - в нулевое состояние. Наличие связей с выхода элемента 3 на входы элементов 2, 4, 6 и 8 исключает неправильную работу устройства.

Формула изобретения

Делитель частоты на шесть, содержащий триггеры памяти, коммутационные триггеры и элементы И-НЕ, при этом единичный выход первого триггера памяти соединен с единичным входом первого коммутационного триггера, нулевой выход которого соединен с единичным входом первого триггера памяти и со входом первого элемента И-НЕ, выход которого подключен к единичным входам первого и второго триггеров памяти, единичный выход первого триггера памяти соединен с единичным входом второго коммутационного триггера, единичный выход которого подключен к нулевому входу третьего коммутационного триггера, нулевой выход второго коммутационпого триггера соединен с единичным входом третьего триггера памяти, со входом второго элемента И-НЕ и с нулевыми входами второго триггера памяти и первого коммутационного триггера, единичный выход третьего коммутационного триггера подключен ко входу второго элемента И-НЕ, к нулевым входам второго и третьего триггеров памяти и к нулевым входам первого и второго коммутационных триггеров, а щина тактирующего сигнала соединена со входом первого элемента И-НЕ, с единичным входом третьего коммутационного триггера и с нулевыми входами первого и второго коммутационных триггеров, отличающийся тем, что, с целью повыщения надежности работы устройства, нулевой выход второго триггера памяти соединен со входом второго элемента И-НЕ и с нулевыми входами первого триггера памяти и первого коммутационного триггера, единичный выход первого триггера памяти соединен со входом первого элемента Н-НЕ, выход которого подключен к единичному входу третьего и к нулевому входу второго коммутационных триггеров, а выход второго элемента соединен с единичным входом третьего и с нулевым входом второго комм)тационных триггеров.

Нсточники информации, принятые во внимание при экспертизе

1.Гутников В. С. Интегральная электроника в измерительных приборах. Л., «Энергия, 1974, с. 85, рис. 42.

2.Авторское свидетельство СССР № 418982, кл. Н ОЗК 23/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Делитель частоты на 1,5 | 1976 |

|

SU566359A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Регистр сдвига | 1975 |

|

SU552638A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

Авторы

Даты

1978-07-30—Публикация

1976-12-03—Подача