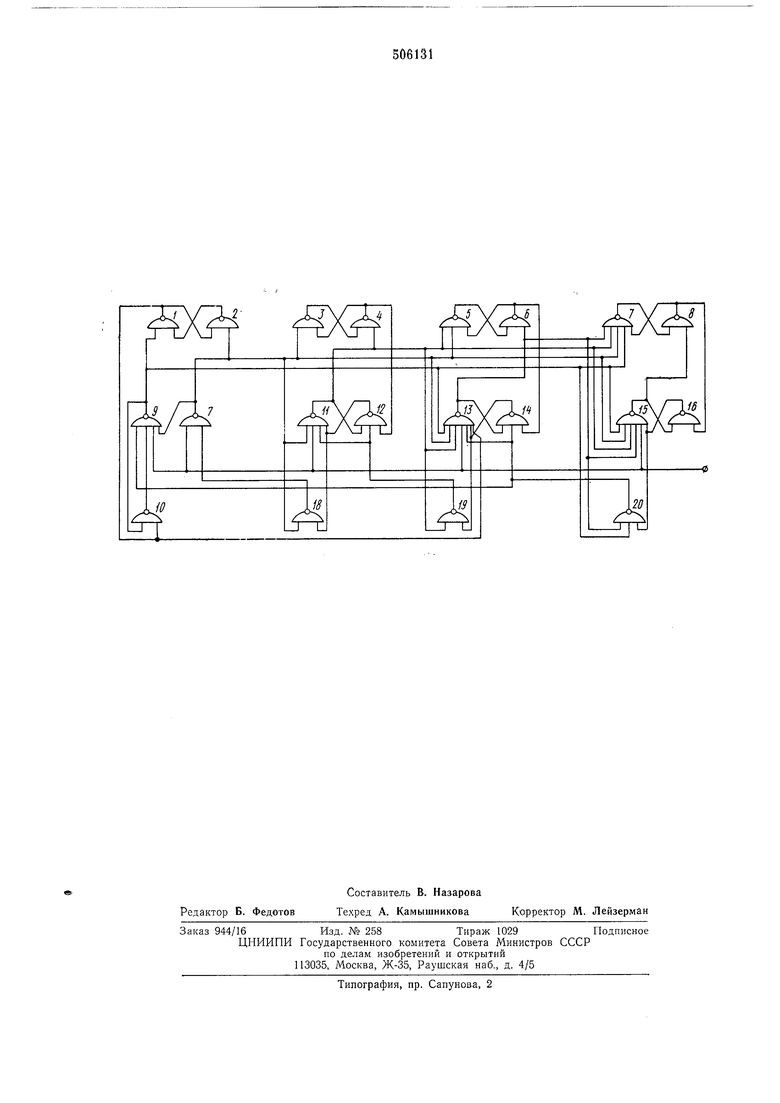

логическая единица. Следовате; ьно, на выходах схем «И-НЕ 10, 18-20 - логический нуль. Таким образом, с приходом иервого тактирующего импульса срабатывает только схема «И-НЕ 15, устанавливая триггер памяти первого разряда в состояние «единица. По окончании действия тактирующего сигнала па выходе схемы «И-НЕ 20 появляется сигнал, равный логической единице. Следовательно, с нриходом следующего тактирующего сигнала срабатывает схема «И-НЕ 13, устанавливая триггер памяти второго разряда -в состояние «единица, а триггер памяти первого разряда - в состояние «нуль. Чтобы схема «И-НЕ 15 первого разряда не могла сработать в момент действия этого тактирующего сигнала после того как триггер памяти первого разряда установится в состояние «пуль, а также для обеспечения устойчивой работы схемы «И-НЕ 13, выход этой схемы «PI-НЕ соединен со входами схем «И-НЕ 15 и 20. Таким образом, сигнал на выходе схемы «И-НЕ может измениться лишь но окончании действия тактирующего сигнала. С приходом третьего тактирующего сигнала срабатывает только схема «И-НЕ 15, поскольку па выходах схемы «И-НЕ 10, 18-20 - логические нули. По окончании действия тактирующего сигнала на выходе схемы «Н-НЕ 20 оказывается логическая единица, а поскольку триггер памяти второго разряда паходится в состоянии «единица, на выходе схемы «П-НЕ 19 - также логическая единица. Таким образом, с приходом четвертого тактирующего импульса схема «П-НЕ 11 устанавливает триггер памяти третьего разряда в состояние «единица, а триггеры памяти второго и первого разрядов - в состояние «нуль. Наличие связи с выхода схемы «П-НЕ 11 на входы схем «И-НЕ 13, 15, 19 опять препятствует неправильной работе счетчика. Аналогичным образом с приходом восьмого тактирующего импульса схема «И-НЕ 17 устанавливает триггер памяти четвертого разряда в состояние «единица, а триггеры памяти остальных разрядов - в состояние «нуль. С приходом девятого тактирующего пмпульса срабатывает схема «И-НЕ 15, и в счетчике устанавливается код 1001. С приходом десятого тактирующего сигнала схема «Н-НЕ 13 не срабатывает, поскольку на выходе схемы «П-НЕ 1 - логический нуль. Поэтому срабатывает только схема «Н-НЕ 9, которая устанавливает триггеры памяти четвертого и первого разрядов в состояние «нуль. Наличие связи с выхода схемы «И-НЕ 9 па входы схем «И-НЕ 10, 13, 15 и 20 опять препятствует неправильной работе счетчика. Таким образом, схема возвращается в исходное состояние, в счетчике устанавливается код 0000, и цикл работы счетчика повторяется. Формула изобретения Двоичио-десятичный счетчик, каждый разряд которого содержит триггер памяти, коммутационный триггер и схему «И-НЕ, причем едипичный выход триггера памяти соединен с единичным входом коммутационного триггера, пулевые выходы коммутационных триггеров первого, второго и третьего разрядов соединены с единичными входами триггеров памяти своих разрядов и с нулевыми входами коммутационных триггеров, триггеров памяти и схем «Н-НЕ всех более младших разрядов, выходы схем «И-НЕ первого и второго разрядов соединены со входами коммутационных триггеров второго и третьего разрядов соответственно, единичные выходы коммутационных триггеров первого, второго и третьего разрядов соединены со входами схем «И-НЕ своего разряда, пулевые входы коммутационных триггеров всех разрядов и вход схемы «Н-НЕ четвертого разряда соединены со входом счетчика, выход схемы «И-НЕ четвертого разряда соединен с пулевыми входами коммутационных триггеров, триггеров памяти и схем «И-НЕ всех разрядов, нулевой выход коммутационного триггера четвертого разряда соединен с единичным входом триггера памяти четвертого разряда и нулевыми входами коммутационных триггеров первого и второго разрядов и триггера памяти первого разряда, отличающийся тем, что, с целью уменьшения количества оборудования, выход схемы «И-НЕ четвертого разряда соединен со входом схемы «И-НЕ первого разряда, выход которой соединен с нулевым входом коммутациопного триггера четвертого разряда, выход схемы «И-НЕ третьего разряда соедипеп со ходом схемы «И-НЕ четвертого разряда, диничный выход триггера памяти четвертого азряда соединен с нулевым входом коммутаионного триггера второго разряда. Ж

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Реверсивный счетчик | 1973 |

|

SU476687A1 |

| Быстродействующий счетчик | 1977 |

|

SU677107A2 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

Авторы

Даты

1976-03-05—Публикация

1974-04-11—Подача