1

Изобретение относится к вычислительной технике и может быть использовано при построении устройства для решения задач математической физики, описываемых уравнениями в частных производных.

Известен вычислительный узел цифровой сетки, содержащий многовходовой сумматор, регистр сдвига, элемент И, группу элементов И, входы сумматора соединены с входами узла, выход сумма- ю тора соединен с последовательным входом регистра сдвига, последовательный выход регистра сдвига, соединен с первым входом элемента.И, параллельные выходы регистра сдвига соединены с пер- 15 выми входами группы элементов И, выход элемента И соединен с последовательным выходом уйла, управляющие входы регистра сдвига и элементов И соединены с управляющими входами узла l. 20

Узел не предназначен для непосредственного решения дифференциальных уравнений с переменными коэффициентами. Использование рассматриваемого узла для рещения такого класса задач требует применения двухступенчатых итерационных методов.

Наиболее близким по технической сушности к изобретению является вычислительный узел цифровой сетки, который содержит запоминающее устройство, коммутаторы, сумматор, регистр сдвига, регистр коэффициента, элемента И, груптту элементов И.

Выходы группы элементов И являются группой выходов узла, последовательный выход регистра сдвига соединен с входом элемента И, выход которого $гв- ляется выходом узла, вход регистра коэффициента является информационным входом узла, адресный вход запоминающего устройства соединен с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно пер- -вой и второй группами входов узла, выход запоминающегоустройства соединен с первым

39764484

BXQQOM сумматора, первый и второй входытъего элементов И являются вторым и

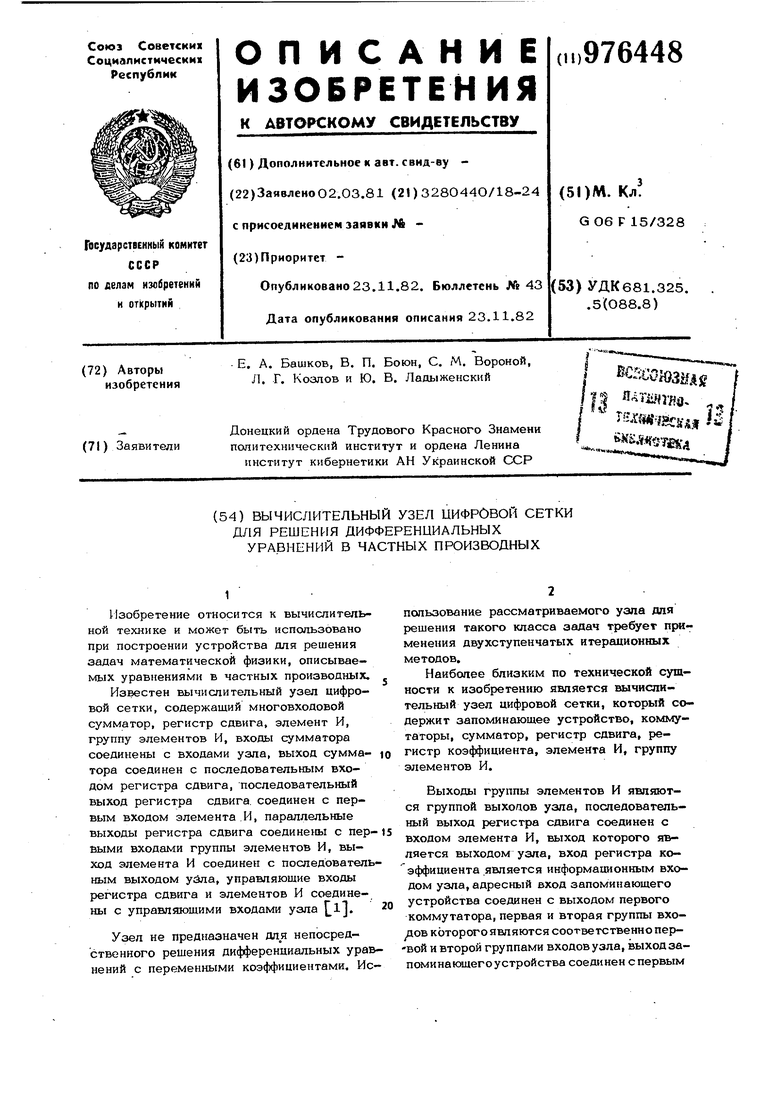

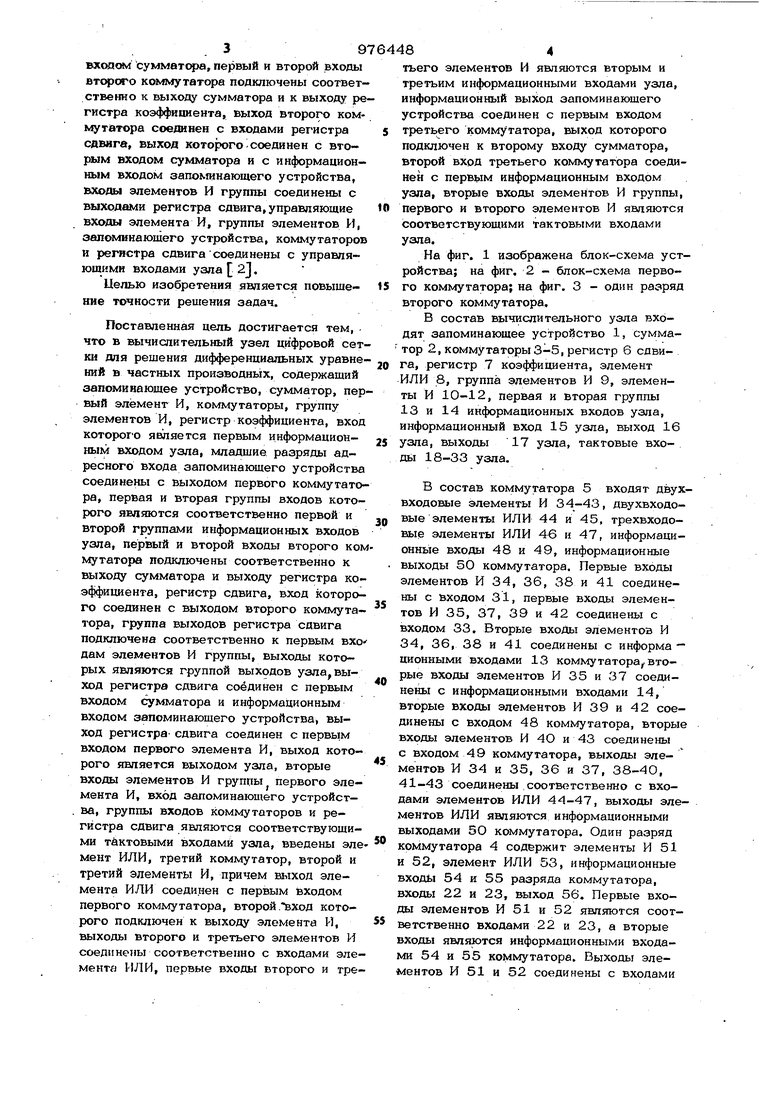

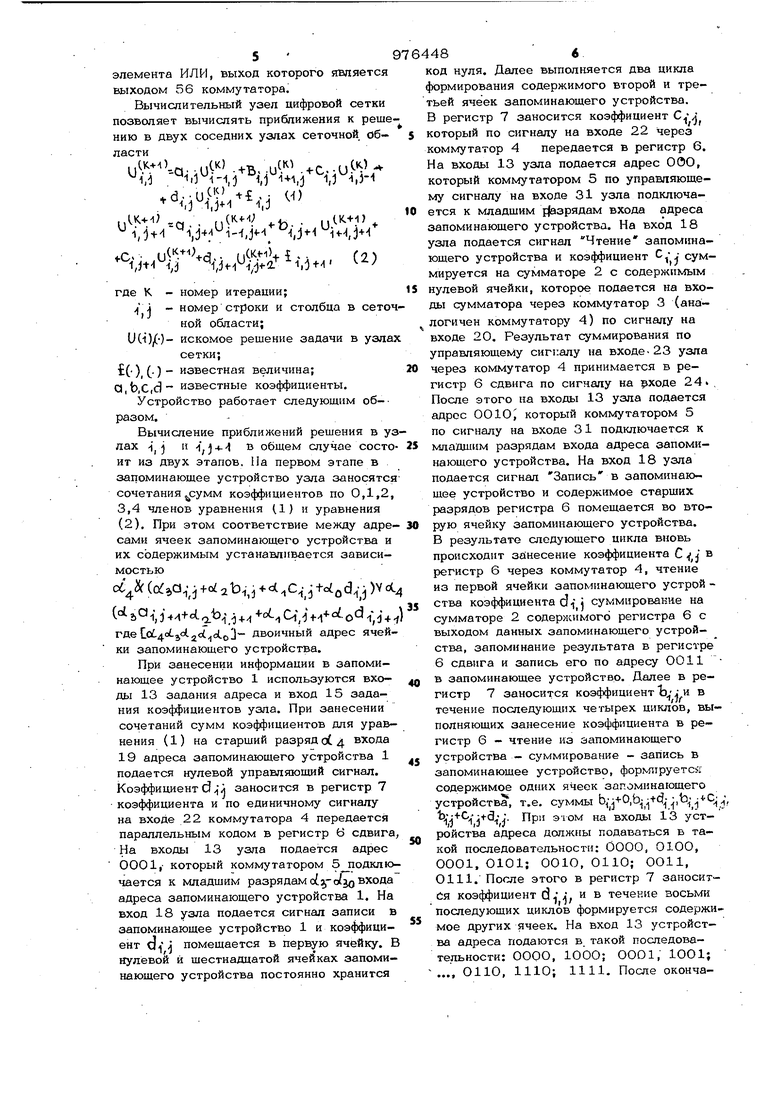

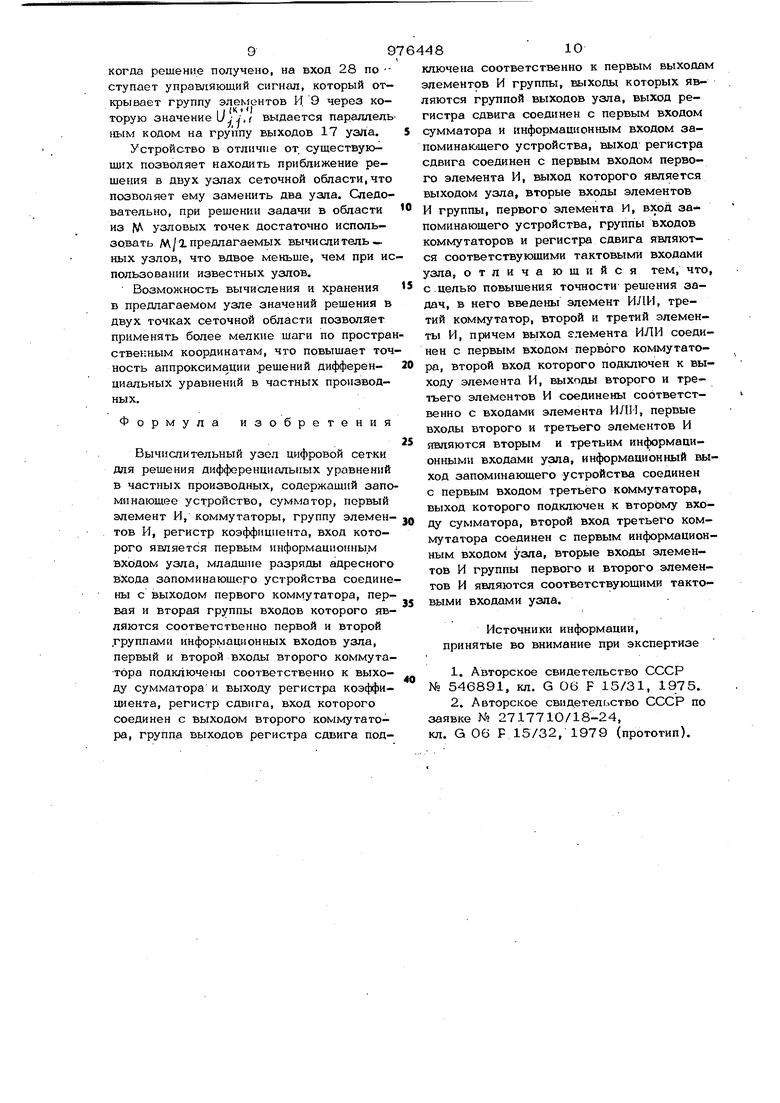

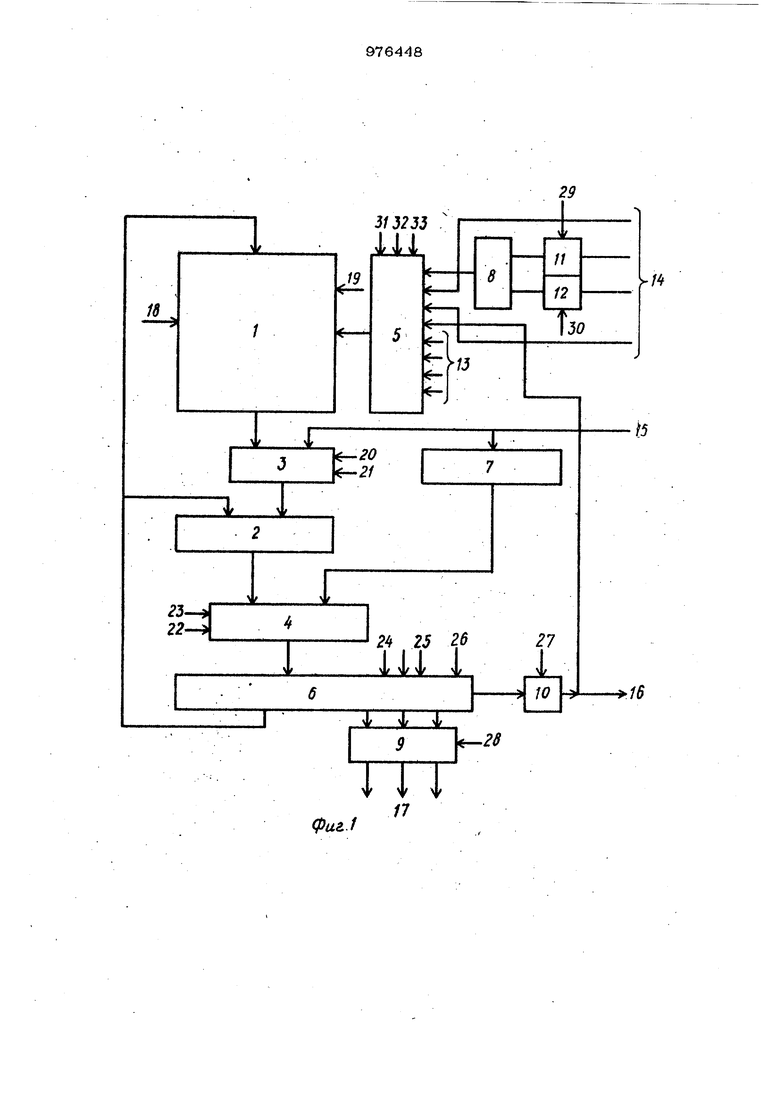

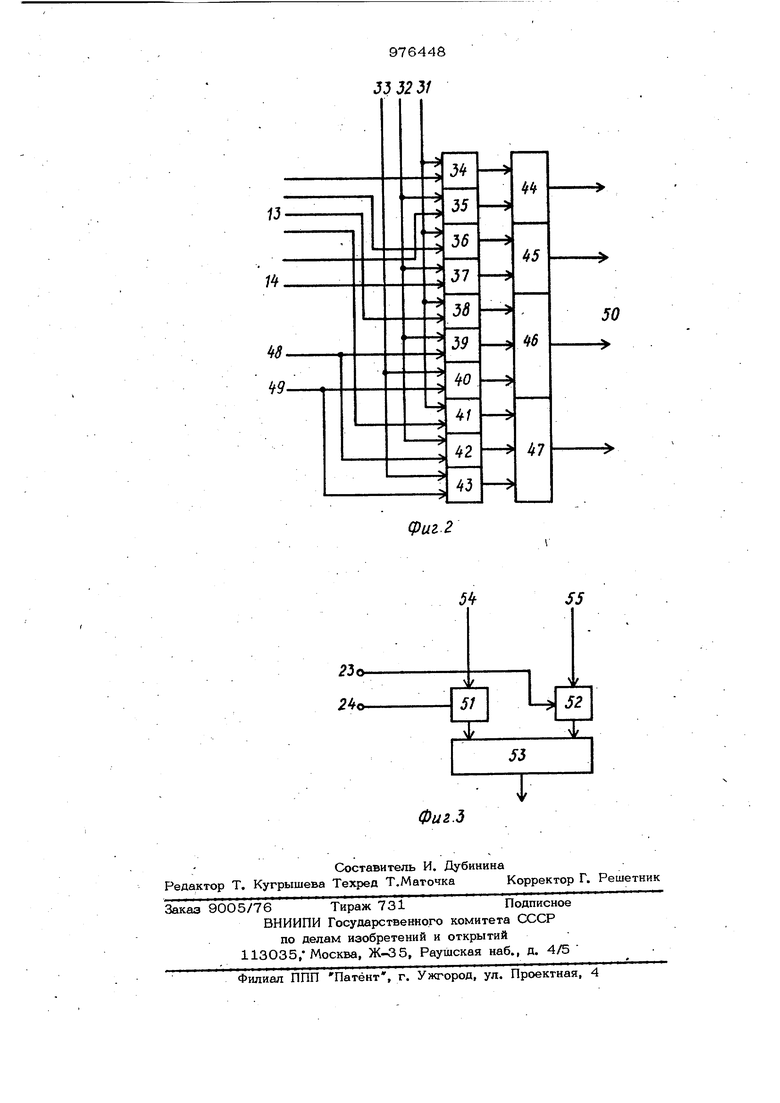

втсфого коммутатора подключены соответ- третьим информационными входами узла, ственно к выходу сумматора и к выходу ре гистра коэффициента, выход второго коммутатора соединен с входами регистра сдвиге, выход которогоСоединен с вторым входом сумматора и с информационным входом запоминающего устройства, входы элементов И группы соединены с выходами регистра сдвига, управляющие входы элемента И, группы элементов И, запоминающего устройства, коммутаторов и регистра сдвига соединены с управляющими входами . Целью изобретения является повыщение точности рещения задач. Поставленная цель достигается тем, что в вычислительный узел цифровой сетки дяя решения дифференциальных уравнеНИИ в частных производных, содержащий запоминающее устройство, сумматор, пер вый элемент И, коммутаторы, группу элементов И, регистр коэффициента, вход которого является первым информационным входом узла, младщие разряды адресного входа запоминающего устройства соединены с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно первой и второй группами информационных входов узла, первый и второй входы второго ком мутатора подключены соответственно к выходу сумматора и выходу регистра коэффициента, регистр сдвига, вход которого соединен с выходом второго коммутатора, группа выходов регистра сдвига подключена соответственно к первым вхо дам элементов И группы, выходы которых являются группой выходов узла, выход регистра сдвига соединен с первым входом сумматора и информационным входом запоминающего устройства, выход регистра- сдвига соединен с первым входом первого элемента И, выход которого является выходом узла, вторые входы элементов И группы первого элемента И, вход запоминающего устройства, группы входов коммутаторов и регистра сдвига являются соответствующиМИ тактовыми входами узла, введены эле мент ИЛИ, третий коммутатор, второй и третий элементы И, причем выход элемента ИЛИ соединен с первым входом первого коммутатора, второй .вход которого подключен к выходу элемента И, выходы второго и третьего элементов И соединены соответственно с входами элемента ИЛИ, первые входы второго и треинформационный выход запоминающего устройства соединен с первым входом третьего коммутатора, выход которого подключен к второму входу сумматора, второй вход третьего коммутатора соединен с первым информационным входом узла, вторые входы элементов И группы, первого и второго элементов И являются соответствующими тактовыми входами узла. На фиг. 1 изображена блок-схема устройства; на фиг. 2 - блок-схема первого коммутатора; на фиг. 3 - одни разряд второго коммутатора. В состав вычислительного узла входят запоминающее устройство 1, сумматор 2, комму та торы 3-5, регистр 6 сдвига, регистр 7 коэффициента, элемент pj g группа элементов И 9, элемен ы И 10-12, первая и вторая группы 13 и 14 информационных входов узла, информационный вход 15 узла, выход 16 узла, выходы 17 узла, тактовые входы 18-33 узла. В состав коммутатора 5 входят двухвходовые элементы И 34-43, двухвходовые элементы ИЛИ 44 и 45, трехвходовые элементы ИЛИ 46 и 47, информационные входы 48 и 49, информационные выходы 50 коммутатора. Первые входы элементов И 34, 36, 38 и 41 соединены с входом 31, первые входы элементов И 35, 37, 39 и 42 соединены с входом 33. Вторые вхоДы элементов И 34, 36, 38 и 41 соединены с информационными входами 13 коммутатора,, вторые входы элементов И 35 и 37 соединены с информационными входами 14, вторые входы элементов И 39 к 42 соединены с входом 48 коммутатора, вторые входы элементов И 4О и 43 соединены с входом 49 коммутатора, выходы элементов И 34 и 35, 36 и 37, 38-40, 41-43 соединены .соответственно с входами элементов ИЛИ 44-47, выходы элементов ИЛИ являются информационными выходами 5О коммутатора. Один разряд коммутатора 4 содержит элементы И 51 и 52, элемент ИЛИ 53, информационные входЬ 54 и 55 разряда коммутатора, входы 22 и 23, выход 56. Первые входы элементов И 51 и 52 являются соответственно входами 22 и 23, а вторые входы являются информационными входами 54 и 55 коммутатора. Выходы элементов И 51 и 52 соединены с входами элемента ИЛИ, выход которого является выходом 56 коммутатора. Вычислительный узел цифровой сетки позволяет вычислять приближения к реше нию в двух соседних узлах сеточной, области ,,, .;j .. .q. , nC 13. . 1,:)- d- r -J fC (-d. ( i f -3 ) 1, I,:) S, i.j t -2} где К - номер итерации; .) j - номер строки и столбца в сето ной области; UC-t)/-)- искомое решение задачи в узла (), О) - известная величина; a,b,Cid известные коэффициенты. Устройство работает следующим об-разом. Вычисление приближений решения в уз лах -i| j и j4-1 в общем случае состо ит из двух этапов. На первом этапе в запоминающее устройство узла заносятся сочетания сумм коэффициентов по 0,1,2, 3,4 членов уравнения (1) и уравнения (2). При этом соответствие между адресами ячеек запоминающего устройства и их содержимым устанавливается зависимостьюo64(o;ja,;j+oi2to,,.,i,C,-.,;j)Yc(. (°tbai,34.,tc(.,,b,-,+,C,.od,;.,rasLoL dL dy cL cli - двоичный адрес ячейки запоминающего устройства. При занесении информации в запоминающее устройство 1 используются вхо- ды 13 задания адреса и вход 15 задания коэффициентов узла. При занесении сочетаний сумм коэффициентов для уравнения (1) на старший разряд 0(4 опа 19 адреса запоминающего устройства 1 подается нулевой управляющий сигнал. Коэффициент заносится в регистр 7 коэффициента и по единичному сигналу на входе 22 коммутатора 4 передается параллельным кодом в регистр в сдвига На входы 13 узла подается адрес 0001,- который коммутатором 5 подключается к младшим разрядамо(а,-озо®° адреса запоминающего устройства 1. На вход 18 узла подается сигнал записи в запоминающее устройство 1 и коэффициент d{ помещается в первую ячейку. В нулевой и шестнадцатой ячейках запоминающего устройства постоянно хранится КОД нуля. Далее выполняется два цикла формирования содержимого второй и третьей ячеек запоминающего устройства. В регистр 7 заносится коэффициент который по сигналу на входе 22 через коммутатор 4 передается в регистр 6. На входы 13 узла подается адрес 000, который коммутатором 5 по управляющему сигналу на входе 31 узла подключается к младщим фзрядам входа адреса запоминающего устройства. На вход 18 узла подается сигнал Чтение запоминающего устройства и коэффициент С суммируется на сумматоре 2 с содержимым нулевой ячейки, которое подается на входы сумматора через коммутатор 3 (аналогичен коммутатору 4) по сигналу на входе 20. Результат суммирования по управляющему сигналу на входе-23 узла через коммутатор 4 принимается в регистр 6 сдвига по сигналу на 1ходе 24 , После этого на входы 13 узла подается адрес OOlOi который коммутатором 5 по сигналу на входе 31 подключается к младшим разрядам входа адреса запоминающего устройства. На вход 18 узла подается сигнал Запись в запоминающее устройство и содержимое старщих разрядов регистра 6 помещается во вторую ячейку запоминающего устройства. В результате следующего цикла вновь происходит занесение коэффициента С в регистр 6 через коммутатор 4, чтение из первой ячейки запоминающего устрой ства коэффициента di ; суммирование на сумматоре 2 содержимого регистра 6 с выходом данных запоминающего устройства, запоминание результата в регистре 6 сдвига и запись его по адресу ООН в запоминающее устройство. Далее в регистр 7 заносится коэффициент л и в течение последующих четырех циклов, выполняющих занесение коэффициента в регистр 6 - чтение из запоминающего устройства - суммирование - запись в запоминающее устройство, формируетсьг содержимое одних ячеек запоминающего устройства, т.е. суммы Ь,--0,.,,,, ,,j- При этом на входы 13 устройства адреса должны подаваться в такой последовательности: ОООО, 0100, ООО1, О101; 001О, ОНО; ООН, от. После этого в регистр 7 заносится коэффициент d.д, и в течение восьми последующих циклов формируется содержимое других ячеек. На вход 13 устройства адреса подаются в такой последовательности: ОООО, ЮОО; ОО01, 10О1; ..., ОНО, 1110; 1111. После окончания формирования сочетаний сумм коэффи циентов для уравнения (1) на входы 14 узла подается единичный сигнал и аналогичным образом формируются сочетания сумм коэффициентов уравнения (2). В ре гистр 7 в соответствующие моменты времени заносятся при этом коэффициенты ,j.i4j4-i.i;dHНа втором этапе осуществляется вычисление нового приближения решения. В исходном состоянии в младщих разрядах регистра 6 сдвига находится LIS i -По -V сигналу на входе 25 старщие разряды ре гистра 6 устанавливаются в ноль.На уп- равляющем входе 19 узла устанавливается нулевой сигнал и осуществляется реализация форму лы (1). На входы коммутатора 5 подаются, начиная с младших разрядов, последовательный код величины Uj ; .(Поступающий с выхода регистра 6 через элемент И 10, и последовательные коды Л) :,U; Ulf :, поступающие с соседних вычислительных узлов сетки. Каждый S-й разряд этих чисел через коммутатор 5 по единичному сигналу на входе 32 и нулевому сигналу на входе 33 узла подается на входы адреса запоминающего устройства. На вход 18 узла подается сигнал Чтение запоминающего устройства. Из ячейки запоминающего устройства, адрес которой определяется кодом (и,,,,,..,Сб:ц.-,, выбирается очередное, ранее подготовлен ное частичное произведение f..d, которое коммутатором 3 по сигналу на входе 20 подается на входы сумматора 2, где складывается с содержимым старших разрядов регистра 6 сдвига. По сигналу, подаваемому на вход 23, сумма с выходов сумматора 2 передается коммутатором 4 на входы старших разрядов ре гистра 6 и по сигналу на входе 24 принимается в регистр 6 сдвига. Значение хранящееся в младших разрядах регистра 6 сдвр1га, выдается на выход 16 узла через элемент И 10, который открывается сигналом, поступающим на вход 27 узяа. После прохождения Vi тактов работы устройства, где и - разрядность на сумматоре 2 складывается содержимое старших разрядов ре- Гистра 6 сдвига и значение f i поступающее с инфоря ационного входа 15 узла через, коммутатор 3 по сигналу на входе 21 узла. Полученное значение U ; по сигналу на входе 24 узла принимается в регистр 6. В точение последующих Vvi 4- С. тактов ( VYI - разряд юсть коэффициентов) старшие разряды найденного значения искомой функции сдвигаются в младшие разряды регистра 6 сдвига, при этом элемент И 10 закрыт нулевым сигналом на входе 27. Затем в вычислительном узле реализуется формула (2). Для этого на вход 1-9 узла подается единичный сигнал и старшие разряды регистра 6 по сигналу на входе 25 устанавливаются в ноль. На входы коммутатора 5 подаются, начиная с младших разрядов, последовательные ко V J- i ды величин: с выхода регистра 6 через элемент И 10, открытый сигналом на входе 27 узла и Uf ., ,0 из соседних вычислительных узлов сетки. Каждый разряд этих чисел через коммутатор 5 по единичному управляющему сигналу на входе 33 узла подается на входы адреса запоминающего устройства. На вход 18 узла подается сигнал Чтение запоминающего устройства. Из соответствующей ячейки запоминающего устройства выбирается соответствующее частичное произведение, которое через коммутатор 3 по сигналу на входе 20, подается на входы сумматора 2, где складывается с накопленной в регистре 6 суммой частичных произведений для предыдущих разрядов неизвестных,поступающих на вход коммутатора 5. Результат сум - мирования по сигналу на входе 24 принимается в регистр 6 сдвига через коммутатор 4. Значение хранящееся в младщих разрядах регистра 6 сдвига, выдается на выход 16 узла, через элемент И 10, который открывается сигналом, поступающим на вход 27 узла. После прохождения п -тактов работы узла на сумматоре 2 складывается значение 1 j./); поступающее на его входы через коммутатор 3 с информационного входа 15 узла по сигналу на входу 21, и содержимое старщих разрядов регистра 6 сдвига. Полученное значение ) по сигналу на входе 24 узла принимается в регистр 6. После сдвига старших разрядов найденного значения искомой функции в младшие разряды регистра 5 вычислительный узел готов к вычислению очередного приближения в узле ( i j ). Последующие итерации осуществляются диалогично, и когда решение получено, на вход 28 по -ступает управляющий сигнал, который открывает группу элементов И 9 через которую значение и ; v.f выдается параллель ным кодом на группу выходов 17 узла. Устройство в отличие от. существующих позволяет находить приближение ре- щения в диух узлах сеточной области,что позволяет ему заменить два узда. Следовательно, при решении задачи в области из fj узловых точек достаточно использовать M/lпредлагаемых вычислительных узлов, что вдвое меньше, чем при ис пользовании известных узлов, Возможность вычисления и хранения в предлагаемом узле значений решения в двух точках сеточной области позволяет применять более мелкие шаги по простра ственным координатам, что повышает точ ность аппроксимации .решений дифферен- циальных уравнений в частных производных. ормула изобретения Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных, содержащий запо минающее устройство, сумматор, первый элемент И, коммутаторы, группу элементов И, регистр коэффициента, вход которого является первым информационны.м входом узла, младшие разряды адресного выхода запоминающего устройства соединены с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно первой и второй .группами информационных входов узла, первый и второй входы второго коммутатора подключены соответственно к выходу сумматора и выходу регистра коэффициента, регистр сдвига, вход которого соединен с выходом второго коммутатора, группа выходов регистра сдвига под94810 ключена соответственно к первым выходам элементов И группы, выходы которых являются группой выходов узла, выход регистра сдвига соединен с первым входом сумматора и информационным входом запоминающего устройства, выход регистра сдвига соединен с первым входом первоIX) элемента И, выход которого является выходом узла, вторые входы элементов И группы, первого элемента И, вход запоминающего устройства, группы входов коммутаторов и регистра сдвига являются соответствующими тактовыми входами узла, отлича ющийся тем, что, с .целью повышения точности решения задач, в него введены элемент ИЛИ, третий коммутатор, второй и третий элементы И, причем выход глемента ИЛИ соединен с первым входом первого коммутатора, второй вход которого подключен к выходу элемента И, выходы второго и третьего элементов И соединены соответственно с входами элемента ИЛИ, первые входы второго и третьего элементов И являются вторым и третьим информационными входами узла, информационный выход запоминающего устройства соединен с первым входом третьего коммутатора, выход которого подключен к второму входу сумматора, второй вход третьего коммутатора соединен с первым информационным входом узла, вторые входы элементов И группы первого и второго элементов И являются соответствующими тактовыми входами узла. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 546891, кл. G 06 F 15/31, 1975. 2.Авторское свидетельство СССР по заявке № 2717710/18-24, кл. G 06 F 15/32, 1979 (прототип).

фиг..1

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сеточной модели для решения дифференциальных уравнений в частных производных | 1980 |

|

SU894717A1 |

| Вычислительный узел цифровой сеточ-НОй МОдЕли для РЕшЕНия диффЕРЕНциАль-НыХ уРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU840920A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1985 |

|

SU1249593A1 |

Фиг 2

5

S5

Авторы

Даты

1982-11-23—Публикация

1981-03-02—Подача