(54) ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Встроенный мультиплексный канал | 1977 |

|

SU734649A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный процессор | 1982 |

|

SU1037264A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

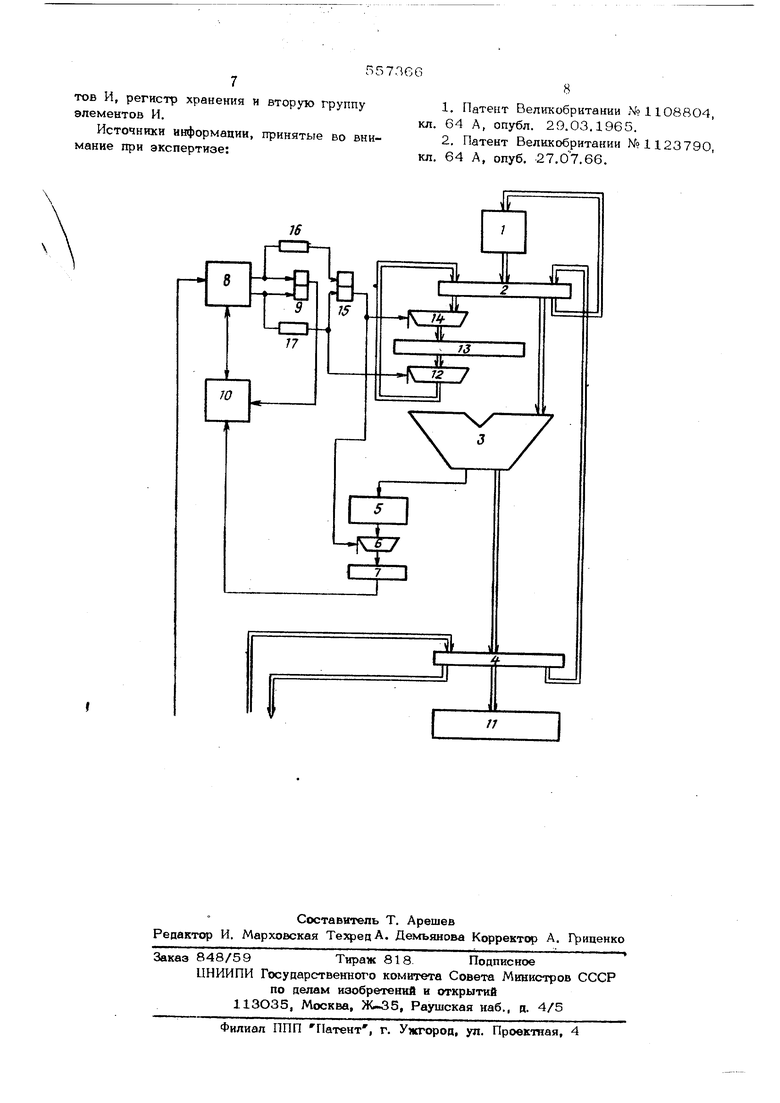

Изобретение относится к вьгчислительной технике и может быть использовано при ко струировании процессоров, оборудование которых используется для передачи данных между каналами ввода-вывода и главной па мятью. Известен процессор, содержащий информационные регистры и каналы, первые выходы и входы которых подключены соответственно к входным и выходным информационным шинам главной памяти, а вторые выходы - к адресным щинам, которые через регистр адреса соединены с адресным входом главной памяти, информационные регистры соединены также двусторонней связью с арифметическим блоком ij. Недостатком этого устройства является значительный расход оборудования, связанный с наличием адресных шин, п также аппаратуры дпя хранения и модификации адресов в каналах. Наиболее близким техническим решением является процессор, содержащий блок местной памяти, выход и вход которое о соединены соответственно с первыми входом и выходом ив| ормаыионного регистра, второй выход которого через «сумматор соединен с первым входом выходного регистра, первый выход которого соединен со вторым входом информационного регистра, вторые вход и выход выходного регистра соединены соответственно с первыми выходом и входом процессора, выходной регистр также соединен двусторонней связью с информационной магистралью каналов, второй выход сумматора соединен через последовательно соединенный узел формтфования признаков, пер вую группу элементов И, регистр признаков с первым входом узла микропрограммного управления, второй вход которого соединен с единичным выходом первого триггера режима, единичный и нулевой входы которого соединены соответстпеиио о первым и вторым выходами узла упраилония микропрерываниями, вход которого соодичен со вторым выходом процессора, у.чсл управления микропрерываниями соединен двусторонней связью с узлом микропротрлммного управления. Нецсютатком jpVf. n;: uv ::npa «в.-ЛЯеТСЯ потеря МЛПтННОГО Г ;::.;;: tin Iepoключечне с 5.-лй. , -,i,|.i;- aii; ni5T машинных команд на режим ьводо-оывода н в обратном направлен .. Эта потеря обусловлена , использованием местной .ггн для сохранения содерж 1мого информапион ого регистра. Целью изобретения являегся повышение быстродействия процессора за счет исклкь. чения потерь машинного времени при переключении режимов. Поставленная цель дост1агается тем, Чю устройство дополнительно содержит две группы элементов И, регистр хранения, два элемента задержки и второй триггвр , единичный и нулевой входы которого через элементы задержка соедШ1еЕЫ соот ветственно с первым и вторым аыхопамн узла управлеяия MHKTjOqiiepE TDaHHs NfHi пуле вой вхоц второго триггера режима соединен с управлкющик входом второй группы элементов И а нулевой выход - с управ- ляющими входами первой и третьей групп элементов И, третт-и РЫХОД н вход нифор-мационцог-о регистра соединены через поСП | 0- ТЙГг-ИО Ог ТП.ЮПТЬС .j .3Jit-. itUiUu il, tiiii i|./ ,4piutii;uii 4 ii аторук) rpjnny элементов И. На чертеже изображена блок-схема процесс Г . Процессор содержит блок 1 местной памяти, информациотозтй регистр 2, сумматор 3, -- Г1коЯ регистр 1: узел 5 формн-рования признаков, первая группа элементов И 6, регистр 7 признаков, узел. 8 управления MHKponnepL-iRaii TMii, триггер 9 ре жима, ii-/ :- 1 ::г . ления, содержащий память микрокоманд, ре гистр адреса, регистр микрокоманды с дешифратором мпкрооперапий, информационная магистра/ш 11 каналов, вторая группа эле ментов И 12, регистр 13 хранения, третья группа элементов И 14, BTOpoit ре жима 15, элементы 16,17 задержки. Устройство работает следующим обра- зом. В режиме выполнения машинных команд (режим процессора) триггеры 9 и 15 находятся в нулевом состоянии, сигналы на их входах отсутствуют. Из блока 1 ш40рмация считывается в информационные регистры 2, (на чертеже показан один из трех регистров). Содержимое информационного регистра 2 передается на входы сумматора 3, результат операции которого помешается в регистр 4 Ila последнего информация постувэ о т Г1 главную пам5гть процессора или (и) в один из нцформациотилх ре гистров 2. Из информационного регистра 2 на ,описывается в блок 1 или (и) пере- aaoic-i на вход сутиматора 3. В каждом цикле содержимое регистра 2 переписывается в регистр 13. Передача ос тцествляется через третью группу элв ментов И 14, на управляющем входе «оторой действует разрешающий потенциал с Нулевого выхода триггера 15, Этот же потенциал поддерживает в открытом состоянии первую группу элементов И 6, через котогрую признаки, формируемые узлом 5, передаются R регистр 7, где они запоминаются Содержимое регистра 7 служит условием ветвлений для микропрограмм процессора. Одновременно с вьтолвением микропрограм гы процессора происходит побайтная перейс)Ча данных между каналами ввода-вывода и внешними устройствами. Если выполняется операция чтения, данные принимаются из внешнего устройства и накапливаются в канале. Если выполняется операция записи, данные из канала передаются во внеипгее устройство. Обмен данными между каналами и внешними устройствами вы- попьглеюи вптоаомно, без использования микропрограммного правления. Когаа вохЗнг-кает необход1:; юсть в обращении к главной памяти, каналы вырабатывают запросы на микропрерываиие, поступающие на вход узла 8. Последний выделяет наиболее приоритетный из одновременно существующих запросов и вырабатывает последовательность сигналов, реализующую тереключение на режим ввода-вывода. ЕСЛИ запрос принят узлом 8 в цикле вы« полнения микрокоманды процессора с номего П , 15 сл-.цующем цикле выполнение микрокоманды Т) 4- 1 совмещается с переклк чением на режим ввода-вывода: в узле 1О сохраняется адрес очередной микрокоманды процессора (п. +2), формируется адреп пепюй микрокоманды ввода-вывода и считывается эта микрокоманда; триггер 9 /станавливается в единичное состояние. Сигсал на единичном входе триггера 9, задержанный элементом 16, переключает в единичное состояние второй 15, в результате чего запираются первая и третья группы элементов И 6 и 14 и тем самым запрещается запись в регистры 7 и 13. Запержка, форм1фуемая элементом 16, подобрана таким образом, что триггер 15 устанасливаотся в единичное состояние, этим обеспечивается сохранение в регистрах 13 и 7 именно той информации, которая была сформиропана в регистре 2 и узле 5 в конце цикла выполнения микрокоманды И +1 - последней микрокоманды процессора, выполнявшейся перец микоопоерыванием. (Элементы 16 и 17 могут быт реализованы, например, в виде сдвиговых регистров). Вслед за микрокомандой процессора Ti +1 выполняется первая микрокоманда микропрограммы ввода-вывода. Эта микро программа осуществляет обращение к глав ной памяти для передачи данных в канал или из него. Адрес данных считывается из блока 1 в регистр 2 и затем передается в сумматор 3, где к нему прибавляется4 если обмен с главной памятью четырехбай товый. Обновленный адрес поступает в регилр 4, затем в регистр 2 и записываетс в блок 1. Он же с регистра 4 передается в главную память. По этому адресу происходит передача данных между главной памятью и каналом; если выполняется операция чтени данные через информационную магистраль 11 каналов и регистр 4 записываются в главную память. Если выполняется операция записи, данные считываются из Г(рав ной памяти и через регистр 4 и информационную магистраль 11 передаются в канал. На вьшолнеиие микропрограммы канала требуется тн циклов. Если в цикле считывания микрокоманды тп отсутствуют запросы от каналов, ожидающие обслуживания, происходит возврат на микропрограмму процес сора. Если микрокоманда тп не использует регистр 2, пикл возврата совмещается с овклом выполнения микрокоманды тп. Во время этого цикла: в узле 1О считывает ся очередная микрокоманда процессора ( Т1 +2), а триггер 9 сбрасывается в нулевое состояние. Сигнал на нулевом входе триггера 9, задержанный элементом 17, открывает вто рую группу элементов И 12, разрешая передачу в регистр 2 из регистра 13, и сбрасывает в нулевое состояние триггера 15, Величина задержки, формируемой элементом 17, подобрана такой, чтобы восста новление информации в регистре 2 сброс триггера 15 происходили на одном синхроимпульсе цикла выполнения последней микрокоманды ввода-вывода. В результате к моменту возобновления работы микропрограммы процессора содержимое регистров 2,7 и состояние схем оказываются такими же, как если бы мнкропрерыпания не было. За циклом выполнения тп -и мнкрокоман ды ввода-вывода следует никл выполнения ( TI +2) -ой микрокоманды процессора, и таким образом возобновляется работа микропрограммы процессора. Таким образом в предложенном процессоре переключение режимов совмещено во времени с выполнением микрокоманд. Благодаря, этому на каждое обращение к главной памяти со стороны каналов продессор затрачивает равно столько машинных циклов, сколько необходимо для вьптолнения микропрограммы ввода-вывода. В резуль-i тате на каждом таком обращении экономится два машннаых цикла, что приводит к существенному повышению произвоаительнозти процессора. Формула изобретения Процессор, содержащий блок местной па.мяти, выход и вход которого соединены сооветственно с первыми входом н выходом информационного регистра, второй выход которого через сумматор соединен с первым входом ш 1ходного регистра, первый выход которого соединен со вторым входом информационного регистра, вторые бход и выход выходного регистра соединены соответственно с первыми выходом и входом процессора, выходной регистр также соединен двусторонней связью с информационной магистралью каналов, второй выход сумматора соединен через лоследовате. соединенный узел формирования признаков, первую группу эле.ментов И, регистр признаков с первым входом узла мюсропрограммного управления, второй вход которого соединен с единичным выходом первого триггера режима, единичный и нулевой входы которого соединены соотв ;-ствекно с первым и вторым выходами узла управления микропрерываниями, | вход которого соединен со вторым выходом процессора, узел управления микропреры- ваниями соединен двусторонней связью с узлом микропрограммного управления, о т - пичаюШийся тем, что, с целью повышения быстродействия процессора, он дополнятельно содержит две группы элементов И, регистр хранения, два элемента задержки и второй триггер режима, единичный и нулевой входы которого через элементы задержки соединены соответственно с первым и вторым выходами узла правления микропрерываниями нулевой ход второго триггера режима соединен с правляющим входом второй группы элеменов И, а нулевой выход - с управляющими ходами первой и третьей групп элеменов И, третьи выход и вход информационого регистра соединены через последоваельно соединенные третью группу элемонтов и, регистр хранения и вторую группу элементов И.

Источники информации, принятые во внимание при экспертизе:

16

8

Авторы

Даты

1977-05-05—Публикация

1974-12-08—Подача