Изобретение относится к области цифровой вычислительной техники и дискретной автоматики и может быть использовано, в частности, в преобразователях аналоговых сигналов в цифровой код. При разработке устройств управления аналого-цифровыми преобразователями в виде отдельных гибридных микросхем повышенной степени интеграции важно при выборе схемы учитывать наряду с количеством логических элементов устройства количество связей между логическими элементами, как внутри разрядов, так и между разрядами. Количество связей в совокупности с минимальным количеством элементов в конечном итоге определяет .размеры подложки микросхемы, ее надежность, процент выхода годных микросхем и их стоимость. Одним из условий применимости й-разрядной микросхемы в п-разрядном устройстве управления () является универсальность схемы й-разрядной микросхемы, т. е. возможность применения ее как в старших, так и в младших разрядах устройства управления без каких-либо изменений структуры связей между отдельными разрядами. Известно устройство управления преобразователем аналог-код с поразрядным уравновешиванием, содержашее распределительное устройство (распределитель импульсов), триггерный регистр и регистр формирования кода 1. Известное устройство обладает сложной схемой, что его надежность. Известно также устройство управлении преобразователем аналог-код с поразрядным взвешиванием, каждый разряд которого содержит один триггер и элементы И и И-ИЛИ на единичных и нулевых входах соответственно. Требуемый алгоритм работы достигается за счет соответствующей организации связей между разрядами. Это устройство по сравнению с другими аналогичными содержит наименьшее количество элементов на разряд 2. Его недостатком является нарастание количества связей от младших (разрядов к старшим, что затрудняет Построение многоразрядных (с количеством разрядов свыше 8) преобразователей и уменьшает их надежность. Это обусловлено принципом построения схемы управления в известном устройстве в виде многоустойчивого триггера с импульсно-комбинационным распределительным устройством тактов и сигналов кода по входам разрядов; в каждом разряде имеется лишь один триггер памяти. Целью изобретения является упрощение устройства, т. е. уменьшение количества связей как в разряде, так и между разрядами.

Поставленная цель достигается тем, что в устройстве управления преобразователем аналог-код с поразрядным уравновешиванием, содержащем триггер запуска, формирователь задержанных импульсов, элементы И, И-НЕ, схему стробирования выходного сигнала элемента сравнения, регистр, каждый разряд которого содержит управляющий элемент И-НЕ и два триггера, состоящие из СДНОГО элемента И- ИЛИ-НЕ с входами триггерной связи и установки, элемента И-НЕ для первого триггера и элемента НЕ для второго триггера, шину тактирующих импульсов и шину начальной установки, выход управляющего элемента И-НЕ в каждом разряде регистра соединен со входом триггерной связи элемента И-ИЛИ-НЕ первого триггера и с первым входом установки элемента И-ИЛИ-НЕ второго триггера, выход элемента |И-ИЛИ-НЕ второго триггера соединен с первым входом управляющего элемента И-НЕ своего разряда и с первым входом установки элемента И-ИЛИ-НЕ первого триггера предыдущего (старшего) разряда, второй вход управляющего элемента И-НЕ соединен с выходом элемента НЕ второго триггера предыдущего (старшего) разряда, третий вход управляющего элемента И-НЕ соединен с шиной тактирующих импульсов, второй вход установки элемента И-ИЛИ-НЕ второго триггера соединен с выходом элемента И-ИЛИ-НЕ первого триггера, второй вход установки элемента И-ИЛИ-НЕ первого триггера соединен с выходом схемы стробирования выходного сигнала элемента сравнения.

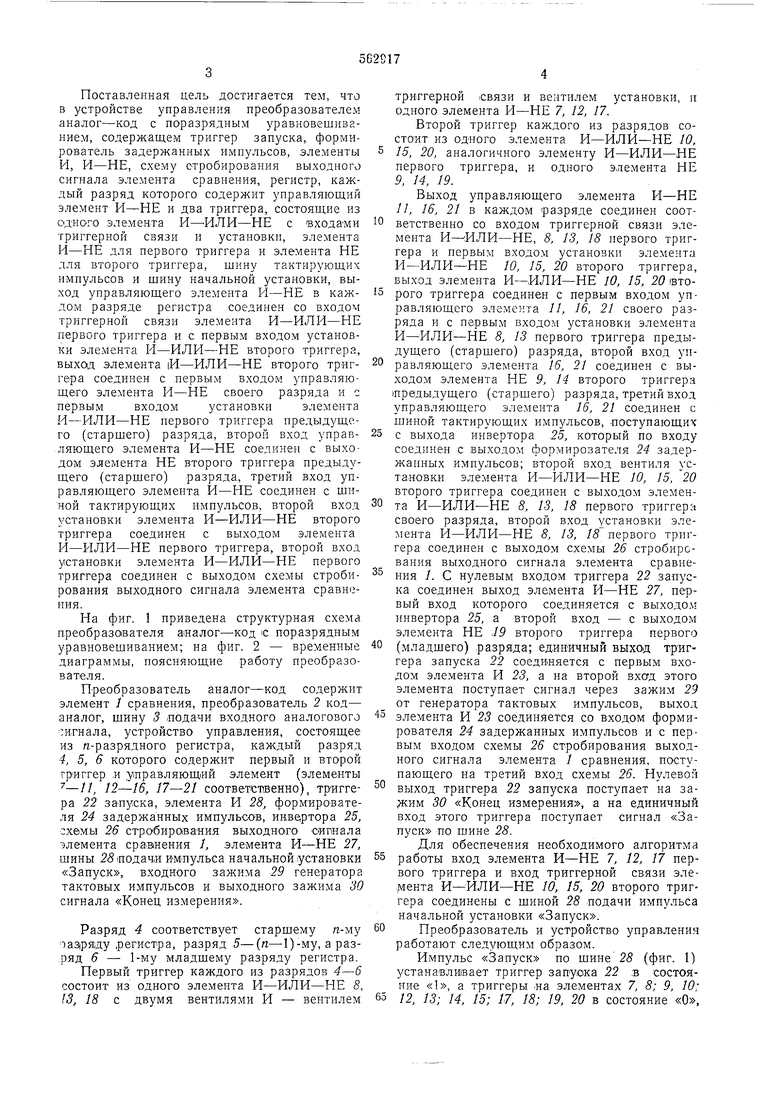

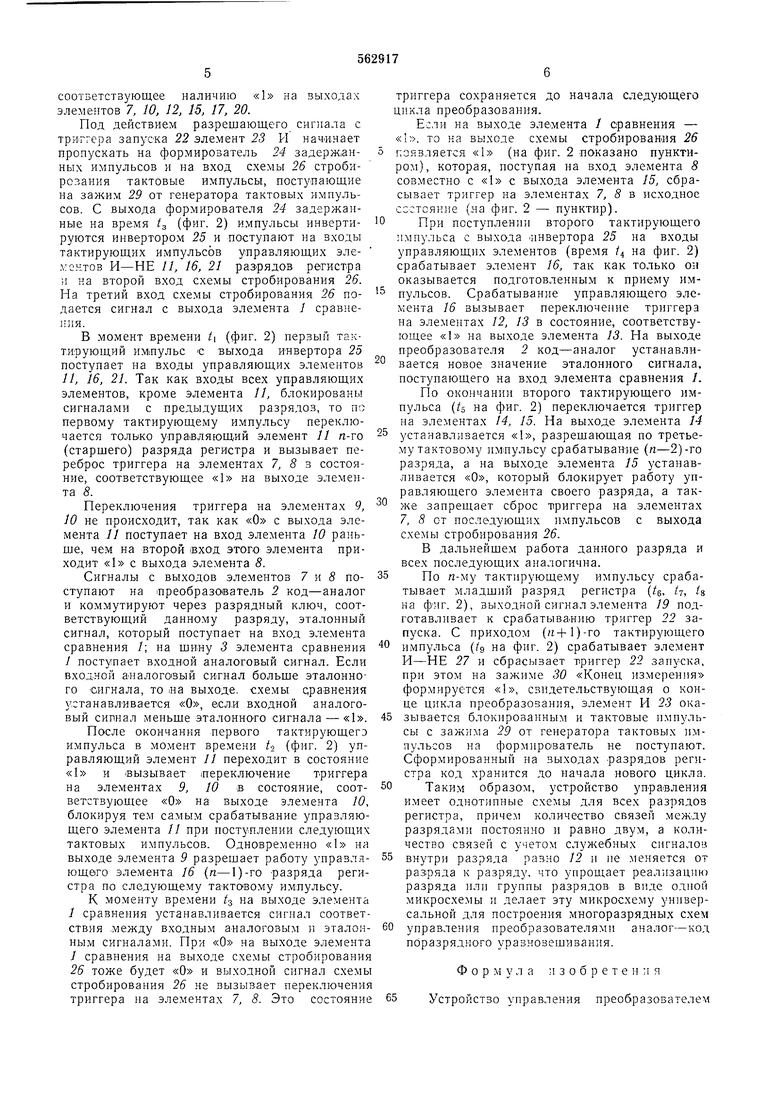

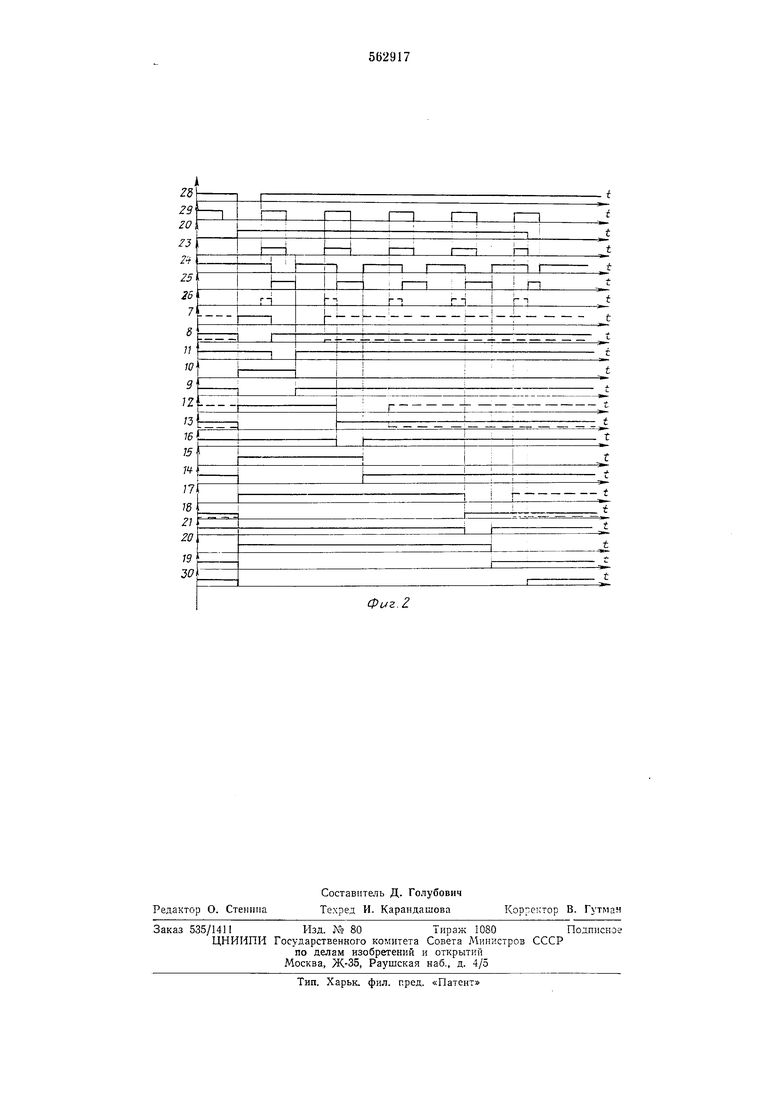

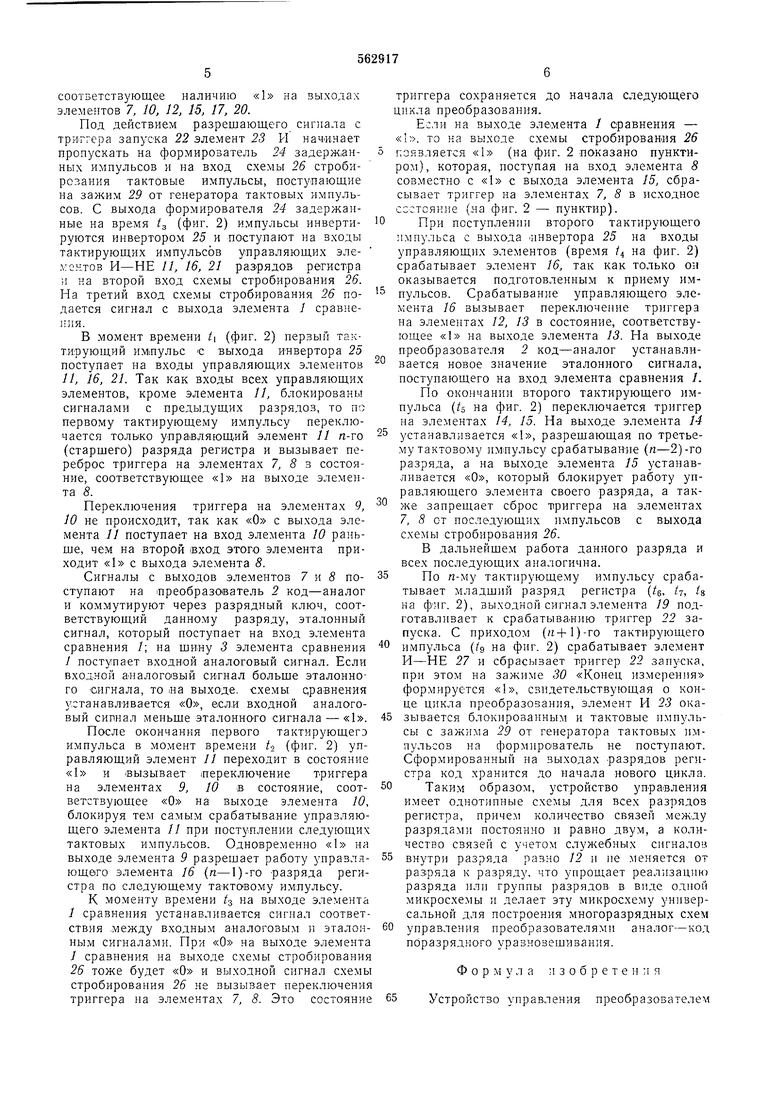

На фиг. 1 приведена структурная схема преобразователя аналог-код ic поразрядным уравновещиванием; на фиг. 2 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь аналог-код содержит элемент 1 сравнения, преобразователь 2 код- аналог, щину 3 -подачи входного аналогового сигнала, устройство управления, состоящее из п-разрядного регистра, каждый разряд 4, 5, 6 которого содержит первый и второй триггер .и управляющий элемент (элементы , 12-16, 17-21 соответственно), триггера 22 за пуска, элемента И 28, формирователя 24 задержанных импульсов, HHBeipTOpa 25, схемы 26 стробираваяия выходного сипнала элемента сравнения 1, элемента И-НЕ 27, шины 25 подачи ИМшульса начальной установки «Запуск, входного зажима 29 генератора тактовых импульсов и выходного зажима 30 сигнала «Конец измерения.

Разряд 4 соответствует старшему п-му паЗ|ря;ду .регистра, разряд 5-(п-1)-му, а разряд 6 - 1-му младшему разряду регистра.

Первый триггер каждого из разрядов 4-6 состоит из одного элемента И-ИЛИ-НЕ 8, 13, 18 с двумя вентилями И - вентилем

триггерной связи и вентилем установки, п одного элемента И-НЕ 7, 12, 17.

Второй триггер каждого из разрядов состоит из одного элемента И-ИЛИ-НЕ 10,

5 15, 20, аналогичного элементу И-ИЛИ-НЕ первого триггера, и одного элемента НЕ 9, 14, 19.

Выход управляющего элемента И-НЕ 11, 16, 21 в каждом разряде соединен соответственно со входом триггерной связи элемента И- ИЛИ-НЕ, 8, 13, 18 первого триггера и первым входом установки элемента И-ИЛИ-НЕ 10, 15, 20 второго триггера, выход элемента И-ИЛИ-НЕ 10, 15, 20 второго триггера соединен с первым входом управляющего элемента 11, 16, 21 своего разряда и с первым входом установки элемента И-ИЛИ-НЕ 8, 13 первого триггера предыдущего (старшего) разряда, второй вход управляющего элемента 16, 21 соединен с выходом элемента НЕ 9, 14 второго триггера тредыдущего (старшего) разряда, третий вход управляющего элемента 16, 21 соединен с шиной тактирующих импульсов, поступающих

с выхода инвертора 25, который по входу соединен с выходом формирователя 24 задержанных импульсов; второй вход вентиля установки элемента И-ИЛИ-НЕ 10, 15, 20 второго триггера соединен с выходом элемента ц-ИЛИ-НЕ 8, 13, 18 первого триггера своего разряда, второй вход установки элемента И-ИЛИ-НЕ 8, 13, 18 первого триггера соединен с выходом схемы 26 стробирования выходного сигнала элемента сравнения /. С нулевым входом триггера 22 запуска соединен выход элемента И-НЕ 27, первый вход которого соединяется с выходом инвертора 25, а второй вход - с выходом элемента НЕ ;/5 второго триггера первого

0 (младшего) разряда; единичный выход триггера запуска 22 соединяется с первым входом элемента И 23, а на второй вхад этого элемента поступает сигнал через зажим 29 от генератора тактовых импульсов, выход

3 элемента И 23 соединяется со входом формирователя 24 задержанных импульсов и с первым входом схемы 26 стробировання выходного сигнала элемента / сравнения, поступающего на третий вход схемы 26. Нулевой

0 выход триггера 22 запуска поступает на зажим 30 «Конец измерения, а на единичный вход этого триггера поступает сигнал «Запуск по шине 28.

Для обеспечения необходимого алгоритма

5 работы вход элемента И-НЕ 7, 12, 17 первого триггера и вход триггерной связи элемента И-ИЛИ-НЕ 10, 15, 20 второго триггера соединены с щиной 28 подачи импульса начальной установки «Запуск.

0 Преобразователь и устройство управления работают следующим образом.

Импульс «Запуск по шине 28 (фиг. 1) устанавливает триггер запуска 22 в состояние «1, а триггеры на элементах 7, 8; 9, 105 12, 13; 14, 15; 17, 18; 19, 20 в состояние «О,

соотБетстзующее наличию «1 на выходах элементов 7, 10, 12, 15, 17, 20.

Под действием разрешающего сиг)1ала с триггера запуска 22 элемент 23 И нач-ннает пропускать на формирователь 24 задержанных импульсов и на вход схемы 26 стробирозания тактовые импульсы, поступающие на зажим 29 от генератора тактовых импульсов. С выхода формирователя 24 задержанные на время з (фиг. 2) импульсы инвертируются инвертором 25 и поступают на входы тактирующих импульсов управляющих элементов И-НЕ //, 16, 21 разрядов регистра } на второй вход схемы стробирования 26. На третий вход схемы стробирования 26 подается сигнал с выхода элемента 1 сравнения.

В момент времени ti (фиг. 2) первый тактирующий им1пульс с выхода инвертора 25 поступает на входы управляющих элементов 11, 16, 21. Так как входы всех управляющих элементов, кроме элемента //, блокированы сигналами с предыдущих разрядов, то по первому тактирующему импульсу переключается только управляющий элемент 11 п-го (старщего) разряда регистра и вызывает переброс триггера на элементах 7, 8 в состояние, соответствующее «1 на выходе элемента 8.

Переключения триггера на элементах 9, 10 не происходит, так как «О с выхода элемента 11 поступает на вход элемента 10 раньще, чем на второй 1Вход этого элемента приходит «1 с выхода элемента 8.

Сигналы с выходов элементов 7 и S поступают на 1преобразо1ватель 2 код-аналог и коммутируют через разрядный ключ, соответствующий данному разряду, эталонный сигнал, который поступает на вход элемента сравнения /; на щину 3 элемента сравнения 1 поступает входной аналоговый сигнал. Если входной а-налоговый сигнал больще эталонного сигнала, то «а выходе, схемы сравнения устанавливается «О, если входной аналоговый сигнал меньще эталонно-го сигнала - «1. После окончания первого тактирующего импульса в момент времени t (фиг. 2) управляющий элемент // переходит в состояние «1 и вызывает переключение триггера на элементах 9, 10 в состояние, соответствующее «О на выходе элемента 10, блокируя тем самым срабатывание управляющего элемента // при поступлении следующих тактовых импульсов. Одновременно «1 на выходе элемента 9 разрешает работу управляющего элемента 16 (п-1)-го разряда регистра по следующему тактавому имлульсу.

К моменту времени /з на выходе эле.ента 1 сравнения устанавливается сигнал соответствия .между входным аналоговым и эталонным сигналами. При «О на выходе элемента 1 сравнения на выходе схемы стробирования 26 тоже будет «О и выходной сигнал схемы стробирования 26 не вызывает переключения триггера на элементах 7, 8. Это состояние

триггера сохраняется до начала следующего икла преобразования.

Если на выходе элемента / сравнения - «Ь. то на выходе схемы стробирования 26 появляется «1 (на фиг. 2 показано пунктиром), которая, поступая на вход элемента 8 совместно с «1 с выхода элемента 15, сбрасывает триггер на элементах 7, 8 ъ исходное ссстояние (на фиг. 2 - пунктир). При поступлении второго тактирующего имиульса с выхода -инвертора 25 на входы управляющих элементов (время /4 на фиг. 2) срабатывает элемент 16, так как только ол оказывается подготовленным к приему импульсов. Срабатывание управляющего элемента 16 вызывает переключение триггера на элементах 12, 13 в состояние, соответствующее «1 на выходе элемента 13. На выходе преобразователя 2 код-аналог устаиавливается новое значение эталонного сигнала, поступающего на вход элемента сравнения /. По окончании второго тактирующего импульса (/5 на фиг. 2) переключается триггер на элементах 14, 15. На выходе элемента 14 устанавливается «1, разрещающая по третьему тактовому 1М1нульсу срабатывание (п-2)-го разряда, а на вы.ходе элемента 15 устанавливается «О, который блокирует работу управляющего элемента своего разряда, а также запрещает сброс триггера на элементах 7, 8 от последующих 11мпульсов с выхода схемы стробирования 26.

В дальнейшем работа данного разряда и всех последующих аналогична. По п-му тактирующему импульсу срабатывает младший разряд регистра (te, (, ts на фиг. 2), выходной сигнал элемента 19 подготавливает к срабатыванию триггер 22 запуска. С при.ходом (n-fl)-ro тактирующего импульса (/9 на фиг. 2) срабатывает элемент И-НЕ 27 и сбрасывает триггер 22 запуска, при этом на зажиме 30 «Конец измерения формируется «I, свидетельствующая о конце цикла преобразования, элемент И 23 оказывается блокированным и тактовые импульсы с зажима 29 от генератора тактовых импульсов на формирователь не поступают. Сформированный на выходах разрядов регистра код хранится до иачала иового цикла. Таким образом, устройство управления имеет однотипные схемы для всех разрядов регистра, причем количество связей между разрядами постоянно и равно двум, а количество связей с учетом служебных сигналов внутри разряда равно 12 и не меняется от разряда к разряду, что упрощает реализацию разряда или группы разрядов в виде одной микросхемы и делает эту микросхему универсальной для построения многоразрядных схем управления преобразователями аналог-код поразрядного уравновешивания.

Формула изобретен и 5i Устройство управления преобразователем

аналог-код с поразрядным уравновешиванием, содержащее триггер запуска, формирователь задержанных импульсов, элементы И, И-НЕ, схему стробироваиия выходного сигнала элемента сравнения, регистр, каждый разряд которого содержит управляющий элемент И-НЕ и два триггера, состоящие из одного элемента И-ИЛИ-НЕ с входами триггерной связи и установки, элемента И-НЕ для первого триггера и элемента НЕ для второго триггера, щину тактирующих импульсов и шину начальной установки, о тличающееся тем, что, с целью упрощения устройства, выход управляющего элемента И-НЕ в каждом разряде регистра соединен со входом триггерной связи элемента И-ИЛИ-НЕ первого триггера и с первым входом установки элемента И-ИЛИ-НЕ второго триггера, выход элемента И-ИЛИ- НЕ второго триггера соединен с первым входом уп2авляющего элемента И-НЕ своего разряда и с первым входом установки элемента И-ИЛИ-НЕ первого триггера предыдущего (старшего) разряда, второй вход управляющ-его элемента И-НЕ соединен с выходом элемента НЕ второго триггера предыдущего (старшего) разряда, третий вход управляющего элемента И-НЕ соединен с шиной тактирующих импульсов, второй вход установки элемента И-ИЛИ-НЕ второго тр иггера соединен с выходом элемента И-ИЛИ-НЕ первого триггера, второй вход установки элемента И-ИЛИ-НЕ первого триггера соединен с выходом схемы стробирования выходного сигнала элемента сравнения.

15

Источники информации, принятые во внимание при экспертизе:

1.«Экопресс-информация, сер. «Нриборы и элементы автоматики н вычислительной техники, 1973, № 35, с. 12.

2.Авторское свидетельство СССР № 310267, кл. Н 03 К 13/17, 26.07.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1977 |

|

SU728222A1 |

| Устройство управления преобразователем аналог-код последовательного приближения | 1979 |

|

SU858206A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Аналого-цифровой преобразователь с самокоррекцией в кодах с естественной избыточностью | 1986 |

|

SU1381703A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU995316A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU945977A1 |

| Цифровой следящий привод | 1980 |

|

SU941926A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Преобразователь код-ШИМ-сигнал | 1989 |

|

SU1667255A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

Фиг.1

±JL

JH

Фиг.2

Авторы

Даты

1977-06-25—Публикация

1975-10-03—Подача