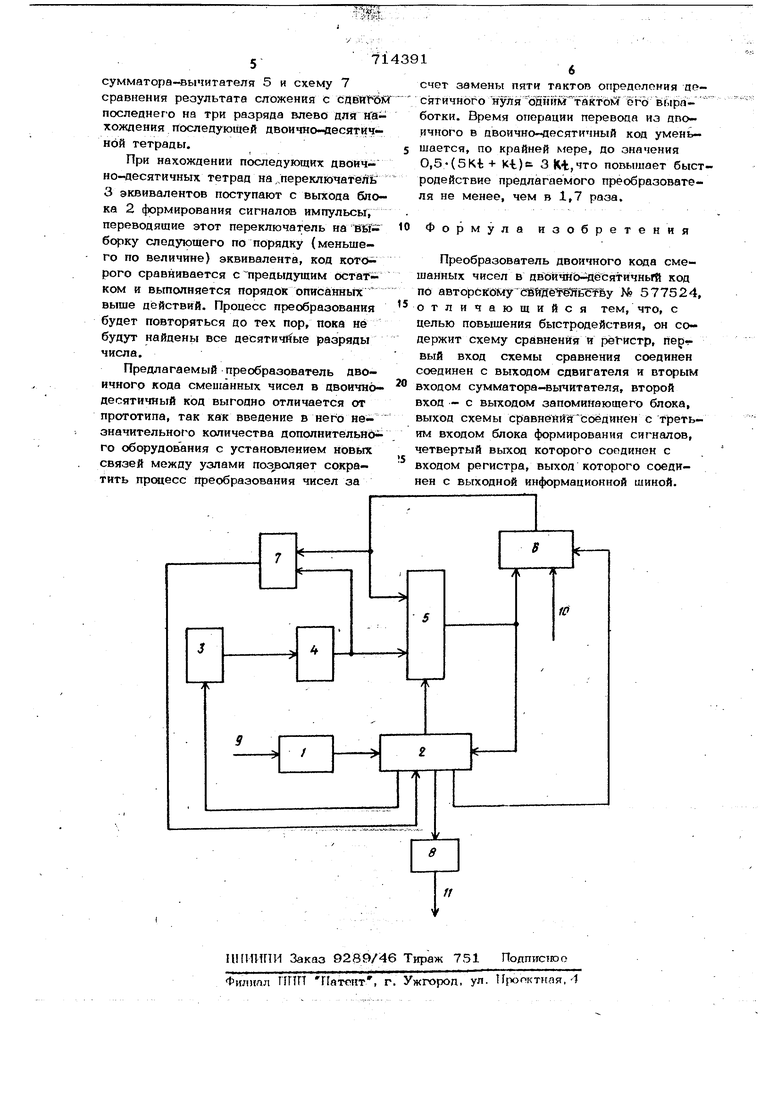

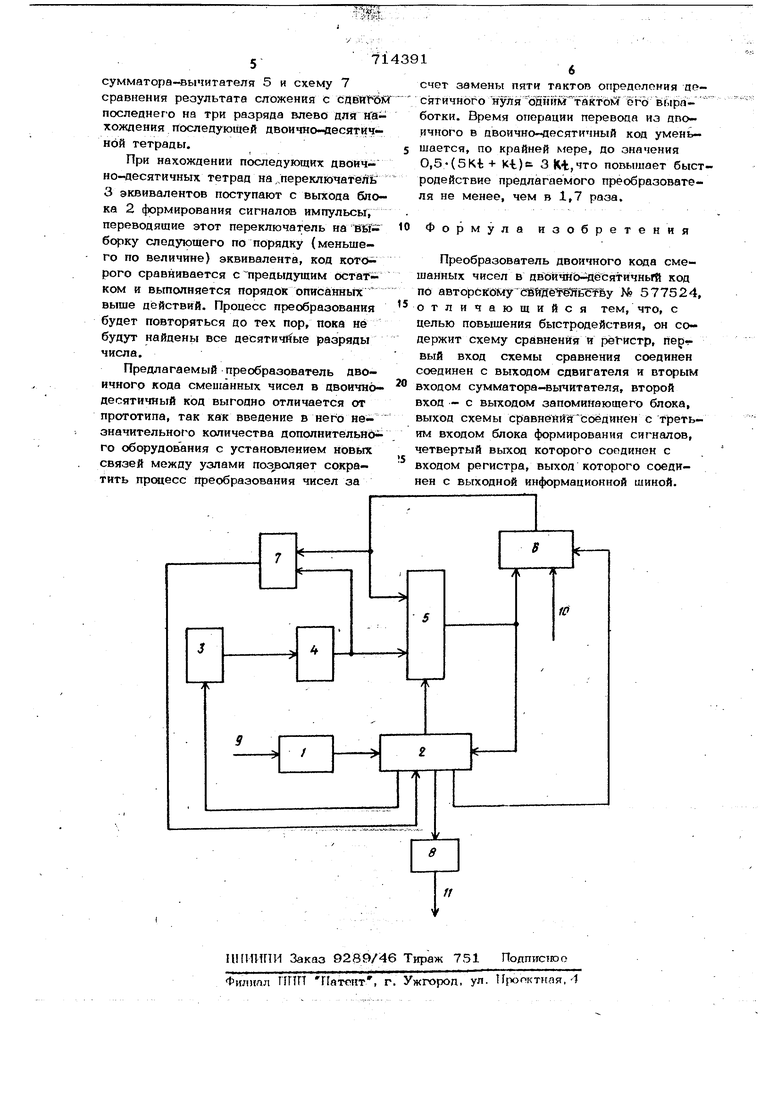

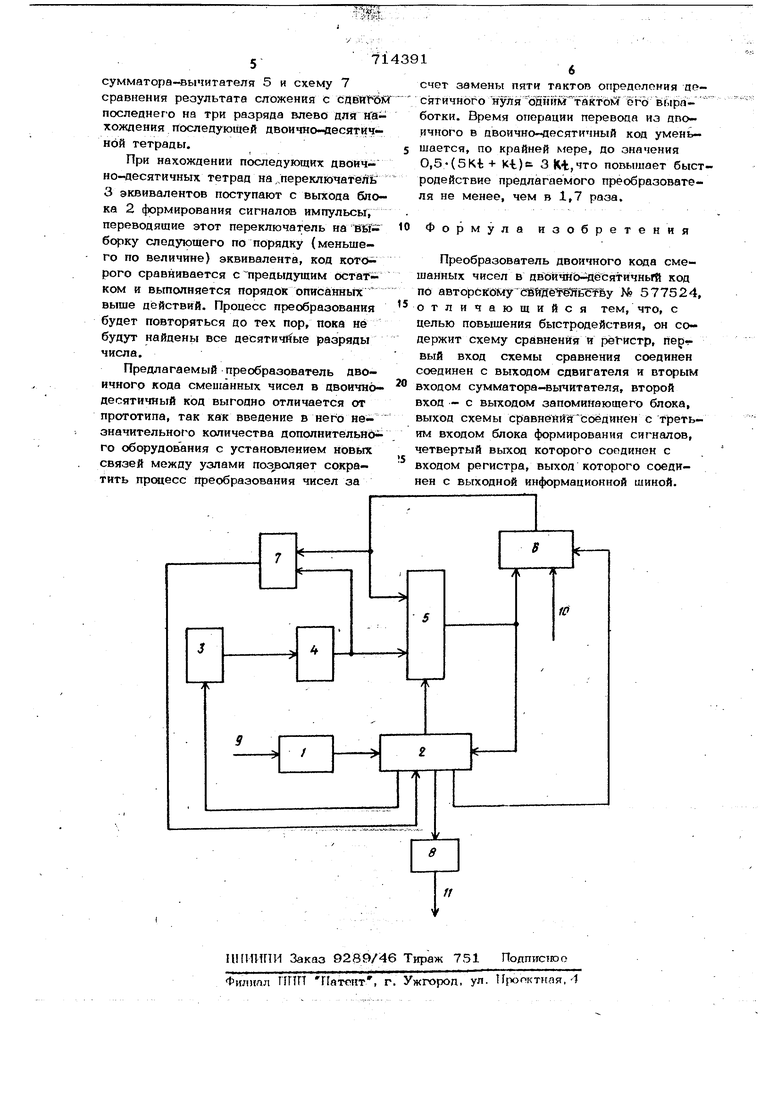

37 смешанных чисел в двоично-десятичный код. Преобразователь двоичного кода смешанных чисел в двоично-десятичный код содержит блок 1 управления, блок 2 формирования сигналов, переключатель 3 эквивалентов, запоминающий блок 4, сум м&тор-еычитатель 5, сдвигатель б, схе- му 7 сравнения, регистр 8, вход 9, на который подается управляющий импульс, вход 10, на который подается двоичный код и выходная информационная шина 11 Работает преобразователь следующим образом. Управляющий импульс поступает на вход 9 блока 1 уйравленйя, который вырабатывает импульсы, необходимые для -автономного функционирования преобразователя. Запоминающий блок 4. содержит двоичные эквиваленты десятичных чисел . .,. где m-l, 2, 3 ... (К-1), К- Количество двоичных эквива лентов определяется принятой разряд.ностью десятичных чисел. Преобразование осуществляется методом деления переводимого числа (а в дальнейшем остатков) без восстановления остатка на свой двоичный эквивалент при нахождении каждой двоично-десятичной . тетрады соответствующей десятичной цифре,отличной от . нуля. Если определяемая тетрада соответствует десятичному нулю, то деление на данный эквивЕИент не производится. Выбор соответствующего эквивалента задается переключателем 3 эквивалентов, которы Управляется блоком 2 формирования сигналов. Управляющие импульсы с выхода блока 2 формйрования сйгналов, про№я чё- рез переключатель 3 эквивалентов, возбуждают в запоминающем блоке 4 шину соответствующего эквивалента (в начале преобразования -старшего, т. е . - 1) двоичный параллельный код которого наступает на вход сумматора- ычитателя ; 5, а также с сдвигом на три разряда вгфаво (за направление вправо принято направление от старших разрядов к млад шим) на вход схемы 7 сравнения. Одновременно на другой вход сумматора-вы- читателя 5 и схемы 7 сравнения подается 6 начале преобразованиячерез сдвига тель 6 от входа 10 переводимое число без сдвига двоичного кода. В схеме 7 сравнения двоичный код переводимого ЧШШ брШЙ М§1 Ш е Шбйад1Ш :КШбм эквивалента . Если переводимое число больше значения 1 . . то схема 7 сравнения вырабатывает сигнал, по которому блок 2 формирования сигнала, формирующий серию управляющих импульсов, ,разрешает в первом такте преобразования вычитание кода эквиЬалента, который служит делителем, из переводимого числа, являющегос я делимым, в сумматоревычитателе 5, откуда на вход сдвигателя 6 поступает код полученного частичного остатка, знаковый разряд которого поступает также в блок 2 формирования сигналов, где формируется код двоичнодесятичной тетрады -и определяется необходимость вычитания или сложения в следующем такте преобразования. При этом, если по анализу знакового разряда сумматора-вычнтателя 5 частичный ост.аток оказался отрицательным, блок 2 формирования сигналов выдает в регистр 8 в виде очередной цифры двоично- |еся- : тичной тетрады нуль и подготавливает в сумматоре-вычитателе 5 цепи сложения для следующего такта преобразования, а если частичный остаток получается положительным, то в регистр 8 выдается единица, а в следующем такте производится вычитание делителя из делимого. В качестве делимого в последующих тактах определения данной двоично-десятичной тетрады берется предыдущий частичный остаток, код которого поступает с сдвигом на один разряд влево (за направление влево принято направление от младших разрядов к старшим) на вход сумматора-вычитателя 5 и схему 7 сравнения от.сдвигателя 6, делитель остается прежним. После нахождения всех цифр двоично-десятичной тетрады, т. е. выполнения четырех тактов, в пятом такте производится, если чадтичный остаток оказался отрицательным, восстановление попбжительного остатка путем прибавления в сумматоре- ычитателе 5 того же делителя к отрицательному остатку под воздействием управляющих импульсов блока 9 формирования сигналов. Если переводимое число меньше значения , . , то схема 7 сравнения вырабатывает сигнал, по котор у блок 2 формирования сигналов выдает параллельным кодом нулевое значение данной тетрады в регистр 8. Одновременно блок 2 формирования сигналов разрешает сложение кода переводимого чйсЛаё нулевым кодом в качестве второго слагаемого в сумматоре-вычитате- ле 5 и подготавливает передачу на вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода смешанных чисел в двоично-десятичный код | 1975 |

|

SU577524A1 |

| Преобразователь двоичного кода сме-шАННыХ чиСЕл B дВОичНО-дЕСяТичНый КОд | 1978 |

|

SU809149A2 |

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

Авторы

Даты

1980-02-05—Публикация

1976-01-08—Подача