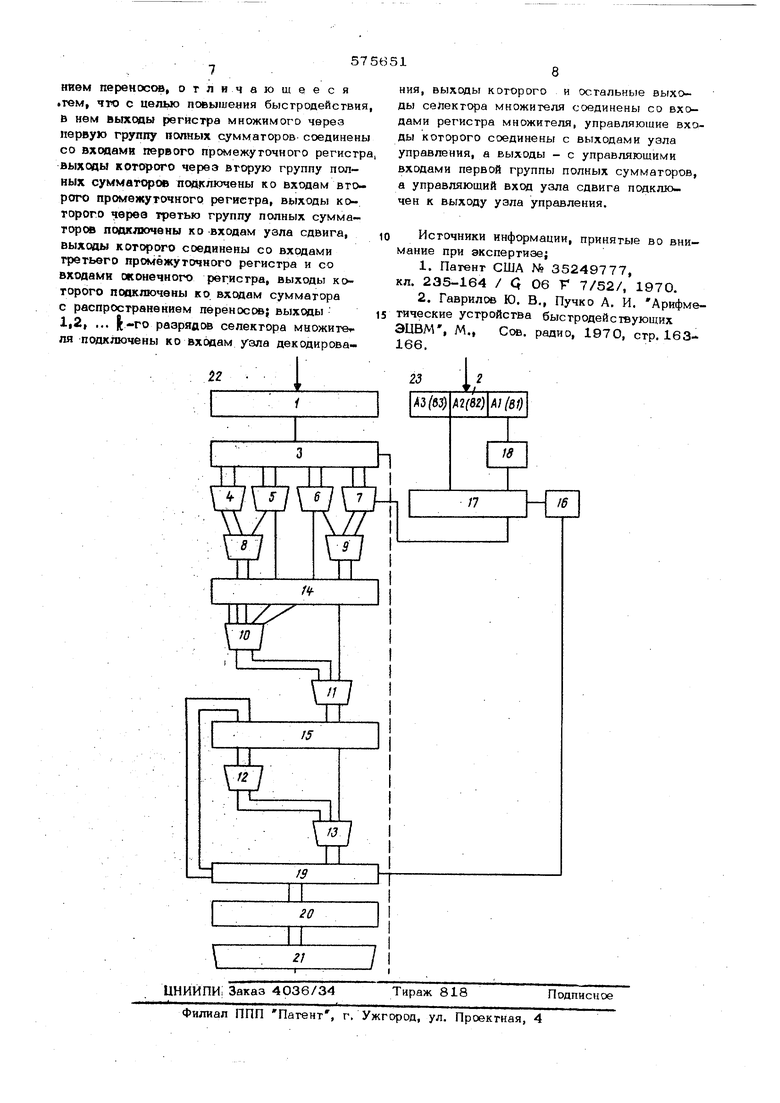

(54) УСТРОЙСТВО ДЛЯ УЛ НОЖЕНИЯ Н -РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ управляющими входами первой группы полных сумматоров. Управляющий вход узла сдвига подключен к выходу узла управления Блок-схема устройства представлена на чертеже. Устройство содержит селектор множимого 1, селектор множителя 2, регистра множимого 3, полные сумматоры 4-13, промежуточные регистры 14,15, узел управления 16, регистр множителя 17, узел декодирования 18, узел сдвига 10, оконечный регистр 20, сумматор с распространением переносов, входные шины 22 первого операнда, входные шины 23 второго операнда. Устройство paiJJTaeT следующим образом Сомножители записываются в соответству щие регистры 3 и 17 через селекторы 1 и 2. Из регистра множимого 3 данные передаются на сумматоры 4-7. Селектор множителя 2 разделен на три части (A3, А2 и А1) таким образом, что часть множителя (A3, А2), которая не попадает в оценку в первом цикле переработки, запоминаетс в регистре множителя 17, а часть мноЖчителя, (AI) которая оценивается в первом цикле переработки в прямом инверсном кодах, заносится через узел декодирсвания 18 в регистр множителя 17. Эта часть используется для управления сумматорами 4-7. По шине управления сигналы с выходов регистра множителя 17 подаются на управляющие входы сумматоров 4-7, которые через сумматоры 8 и 9 с запоминанием переноса соединены с регистром i 14. Быхо ды регистра 14 соединены со входами сумматоров 10 и 11, причем соответствующие выходы сумматора 10 подключены ко входам сумматора 11. Выходы сумматора 11 соединены со входами регистра 15. Выходы регистра 15 также подключены ко входам сумматоров 12 и 13. Соответствующие выходы сумматора 12 подключены ко входам румматора 13, выходы которого соединены со входами узла сдвига 19., Выходы узла сдвига 19 соединены со входами регистра 15, и со входами регистра 20, обеспечиваю щего прием промежуточных результатов. Регистр множителя 17 управляющей шиной соединен с узлом управления. 16, выход которого подкорочен ко вxt|дУ j5r Злa сдвига 19. Выходы регистра 2:0 -0Р : кйб«Ы со входами сумматора с продвижением переноса 21. Все с умматоры 4-13 являются сумматорами с запоминанием переноса, их реализация не представляет трудностей. Они формируют сигналы в соответствии со следующей табл цей Выходные величины Выходная функция Выбор выходной функции определяется сигналами на входах управления полного сумматора. Значения этих сигналов для сумматоров 4-7 определяются выходными сигналами узла декодирования 18, которые запоминаются в регистре множителя 17. Узел декодирования 18 по двум батам множителя Х| и X 2 выбирает одно из четырех возможных значений выходной функции. Сумматоры 8-13 выполняют только сло женке, и управление ими не производится. Число m элементов, образующих полные сумматоры, выбрано таким образом, чтобы они могли сложить два частных произаеде ния с учетом их общей длины, и оно равно четверти общего числа разрядов складываемых частных произведений или частных сумм. Одновременная оценка всех разряде мноидателя при больших сомножителях приводит к усложнению устройства, связанному с необходимостью построения последовательностей сумматоров. Соответственно возрастает и время выполнения операции. В предложенном устройстве множитель подразделен на К одинаковых по числу групп разрядов по tt 5 битов и однсеременно использует ся только л битов множителей. Следующие группы битов множителя обрабатываются в последующих циклах выполнения операции. Для выполнения оценки множителя (ж-fti) разряды множителя соединены через селектор множителя 17 с управляющим входом YI -Л полного сумматора. При этом множитель в каждом цикле .обработки сдвигается вправо на И битов, и имеется соответсгву ющий адрес сдвига входа селектора множителя 2. Например, 24-разрядньй множитель обрабатывается в течение, трех циклов. Ко входам узла декодирования ;1;8 подключены восемь младших раарящ ой;: 1Инйжителя и их инверсные значе;||Цй В узла/ Ьания 18 cteif W ribr управления для сумматОрвв4 5 ti;i3Hw -сй запоминаются в (1& -мН;Эж1йгёля 17, поэтому уже к нач(а{1у. цикла Ьёрэботкн имеется информация на управляющих входах первых четырех сумматоров 4-7. При этом время распространения сигналов через узел декоди рования .18 сокращается за счет использования прямых и инверсных значений сигналов селекторов множителя. Регистр множимого 3 с длиной 24 разряда таксоеди-. нен с информационными входами сумматоров 4-7, что на входах каждого из них множимое подведено дважды, причем оба они сдвинуты одно относительно другого на один разряд, поэтому частные произведения в процессе умножения могут складываться. Процесс умножения разделен во времени на четыре такта. Каждому из этих тактов соответствуют передачи информации на соответствующие промежуточные и оконечные регистры. Промежуточный регистр 15, подключенный к последс«ательностн сумматоров 4-11 запоминает на время цикла частные суммы. В сумматорах 12,13 в третьем такте выполнения операции они складываются, таким образом, после трех циклов обработки весь множитель оказывается обработанным. Окончательное произведение множимого и множителя формируется после восьми циклов, причем в шестом цикле производится запись по сигналу управления в счсонечный регистр 20. Для этой цели множитель разбивается на три равных по длине группы битов А1, А2, A3 ига В1, В2, ВЗ или С1,-С2, СЗ. В сумматорах 4-7 частные проиэдедения суммируются до частшых сумм и частных переносов и через полные сумматоры 8,0 заносятся в - регистр 14. Некоторые частные переносы сразу попадают в регистр 14, не проходя через полные сумматоры. Одновременно множитель в регистре множителя 17 с помощью узла управления 16 сдвигает ся на Bocevjb разрядов вправо с помощью j eneKTopa множЦт.еля 2, так что в узле, аекодирования 18 декодируются разряды с 8 до 15, которые затем заносятся на регистр мно жителя 17.в в следующем цикле пд{омежутонный резуль тат попадает из регистра 14 на регистр 15 Кшс и в предыдущем цикле к сумматорак 4-7 подключено множимое. Декодированный множитель переносится с регистра множителя 17 и определяет в сумматорах 4-7, какие частные произведения будут сложены. Одновременно множитель из регистра множителя 17 с помощью селектора множителя 2 сдвигается еще на восемь разряде вправо, так что в узле декодирования 18 декодируются последние разряды от 16 до 23. В третьем цикле первый промежуточный результат с регистра 15 проходит через сумматоры 12, 13. Посредством управляюще го импульса из узла управления 1 6, который передается на узел сдвига 19, первый промежуточный результат сдвигается на восемь разрядов и в конце цикла вместе со вторым промежуточным результатом поступает на регистр 15. Третий промежуточный результат от третьего и последнего участком множителя запоминается в регистре 14. Теперь новая пара сомножителей может быть записана в регистр множителя 17 и регистр множимого 3. В четвертом цикле оба первых промежуточных результата (частные суммы и частные переносы) объединяются через сумматоры 12,13. Посредством сигнала управления-с узла управления 16, который подается на узел сдвига 19, объединенные промежуточные результаты сдвигаются еше на восемь разрядов вправо. Эти промежуточные результаты в кон- це цикла вместе с третьим и последним промежуточным результатом попадают на регистр 15. В следующем цикле объединенные промежуточные результаты добавляются в сум- маторах 12, 13 к третьему и последнему промежуточным результатам, так что получается общая сумма и общие переносы всех частных произведений. Пocpeдcтвo импульса управления с узла 1 управления 16 на узел сдвига 19 передается конанда записи в регистр 20. Общая сумма и общий перенос аапоминаются, В циклах с шестого по восьмой в сумматоре продвижения переноса 21 складывают ся общая сумма и общие переносы в .(жончательное произведение. После восьми циклов переработки получают произведение. В то лее время, когда форм руются конечная сумма ч конечные переносы, от третьей пары сомножителей объедуняются первая и вторая частные суммы, Технико-экономический эффект иаобретеНИН заключается в пс ьгщен{ге -быстродействвия устройства в 3,5 - 4 раза при достаточно простой н однородной структуре. Ф о р М- у л а изобретения Устройство для умножения п -разрядных ДВО1ГЧНЫХ чисел, содержащее селектор множимого, входы которого соединены со входными щинами первого операнда, а выходы со входами регистра множимого, се юктор множителя, входы которого подключены ко входным щинам второго операнда, регистру множителя, сумматоры с распространением переносов, узел сдвига, узел декэдирс(вания, узел управления, оконечный и npot,reжуточный, регистры, сумматор с распростране

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ УМНОЖИТЕЛЬ С ФИКСИРОВАННОЙ ТОЧКОЙ | 1998 |

|

RU2131617C1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1973 |

|

SU409222A1 |

Авторы

Даты

1977-10-05—Публикация

1974-04-30—Подача